【第一季】CH05_FPGA设计Verilog基础(二)Enter a post title

【第一季】CH05_FPGA设计Verilog基础(二)

5.1状态机设计

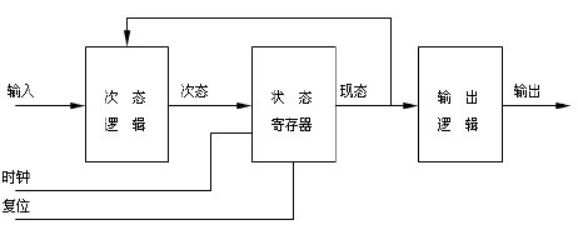

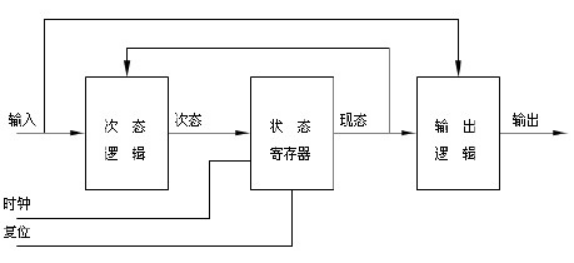

状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路。通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态的时序逻辑电路,三是输出组合逻辑电路。通常,状态机的状态数量有限,称为有限状态机(FSM)。由于状态机所有触发器的时钟由同一脉冲边沿触发,故也称之为同步状态机。

根据状态机的输出信号是否与电路的输入有关分为Mealy型状态机和Moore型状态机。

1、Moore型有限状态机:是指那些输出信号仅与当前状态有关的有限状态机,即可以把Moore型有限状态机的输出看成是当前状态的函数。

2、Mealy型有限状态机:是指那些输出信号不仅与当前状态有关,而且还与所有的输入信号有关的有限状态机,即可以把Mealy有限状态机的输出看成是当前状态和所有输入信号的函数。可见,Mealy有限状态机要比Moore型有限状态机复杂一些。

Moore型和Mealy型有限状态机的区别:Moore型有限状态机仅与当前状态有关,而与输入信号无关;Mealy型有限状态机不但与当前状态有关,而且还与状态机的输入信号有关。

状态机的状态转移图,通常也可根据输入和内部条件画出。一般来说,状态机的设计包含下列设计步骤:

• 根据需求和设计原则,确定是Moore型还是Mealy型状态机;

• 分析状态机的所有状态,对每一状态选择合适的编码方式,进行编码;

• 根据状态转移关系和输出绘出状态转移图;

• 构建合适的状态机结构,对状态机进行硬件描述。

状态机的描述通常有三种方法,称为一段式状态机,二段式状态机和三段式状态机。状态机的描述通常包含以下四部分:

1)利用参数定义语句parameter描述状态机各个状态名称,即状态编码。状态编码通常有很多方法包含自然二进制编码,One-hot编码,格雷编码码等;

2)用时序的always块描述状态触发器实现状态存储;

3)使用敏感表和case语句(也采用if-else等价语句)描述状态转换逻辑;

4)描述状态机的输出逻辑。

下面根据状态机的三种方法,来比较各种方法的优劣。

5.2一段式状态机

|

module detect_1( input clk_i, input rst_n_i, output out_o ); reg out_r; //状态声明和状态编码 reg [1:0] state; parameter [1:0] S0=2'b00; parameter [1:0] S1=2'b01; parameter [1:0] S2=2'b10; parameter [1:0] S3=2'b11; always@(posedge clk_i) begin if(!rst_n_i)begin state<=0; out_r<=1'b0; end else case(state) S0 : begin out_r<=1'b0; state<= S1; end S1 : begin out_r<=1'b1; state<= S2; end S2 : begin out_r<=1'b0; state<= S3; end S3 : begin out_r<=1'b1; end endcase end assign out_o=out_r; endmodule |

一段式状态机是应该避免使用的,该写法仅仅适用于非常简单的状态机设计,不符合组合逻辑与时序逻辑分开的原则,整个结构代码也不清晰,不利用维护和修改。

5.3两段式状态机

|

module detect_2( input clk_i, input rst_n_i, output out_o ); reg out_r; //状态声明和状态编码 reg [1:0] Current_state; reg [1:0] Next_state; parameter [1:0] S0=2'b00; parameter [1:0] S1=2'b01; parameter [1:0] S2=2'b10; parameter [1:0] S3=2'b11; //时序逻辑:描述状态转换 always@(posedge clk_i) begin if(!rst_n_i) Current_state<=0; else Current_state<=Next_state; end //组合逻辑:描述下一状态和输出 always@(*) begin out_r=1'b0; case(Current_state) S0 : begin out_r=1'b0; Next_state= S1; end S1 : begin out_r=1'b1; Next_state= S2; end S2 : begin out_r=1'b0; Next_state= S3; end S3 : begin out_r=1'b1; Next_state=Next_state; end endcase end assign out_o=out_r; endmodule |

两段式状态机采用两个always模块实现状态机的功能,其中一个always采用同步时序逻辑描述状态转移,另一个always采用组合逻辑来判断状态条件转移。两段式状态机是推荐的状态机设计方法。

5.4三段式状态机

|

module detect_3( input clk_i, input rst_n_i, output out_o ); reg out_r; //状态声明和状态编码 reg [1:0] Current_state; reg [1:0] Next_state; parameter [1:0] S0=2'b00; parameter [1:0] S1=2'b01; parameter [1:0] S2=2'b10; parameter [1:0] S3=2'b11; //时序逻辑:描述状态转换 always@(posedge clk_i) begin if(!rst_n_i) Current_state<=0; else Current_state<=Next_state; end //组合逻辑:描述下一状态 always@(*) begin case(Current_state) S0: Next_state = S1; S1: Next_state = S2; S2: Next_state = S3; S3: begin Next_state = Next_state; end default : Next_state = S0; endcase end //输出逻辑:让输出out,经过寄存器out_r锁存后输出,消除毛刺 always@(posedge clk_i) begin if(!rst_n_i) out_r<=1'b0; else begin case(Current_state) S0,S2: out_r<=1'b0; S1,S3: out_r<=1'b1; default : out_r<=out_r; endcase end end assign out_o=out_r; |

三段式状态机在第一个always模块采用同步时序逻辑方式描述状态转移,第二个always模块采用组合逻辑方式描述状态转移规律,第三个always描述电路的输出。通常让输出信号经过寄存器缓存之后再输出,消除电路毛刺。这种状态机也是比较推崇的,主要是由于维护方便,组合逻辑与时序逻辑完全独立。

【第一季】CH05_FPGA设计Verilog基础(二)Enter a post title的更多相关文章

- 【第一季】CH04_FPGA设计Verilog基础(一)Enter a post title

[第一季]CH04_FPGA设计Verilog基础(一) 4.1 Verilog HDL 代码规范 u 项目构架设计 项目的构架用于团队的沟通,以及项目设计的全局把控 u 接口时序设计规范 模块和模块 ...

- 【第一季】CH06_FPGA设计Verilog基础(三)

[第一季]CH06_FPGA设计Verilog基础(三) 一个完整的设计,除了好的功能描述代码,对于程序的仿真验证是必不可少的.学会如何去验证自己所写的程序,即如何调试自己的程序是一件非常重要的事情. ...

- Hadoop 2.x从零基础到挑战百万年薪第一季

鉴于目前大数据Hadoop 2.x被企业广泛使用,在实际的企业项目中需要更加深入的灵活运用,并且Hadoop 2.x是大数据平台处理 的框架的基石,尤其在海量数据的存储HDFS.分布式资源管理和任务调 ...

- QQ聊天界面的布局和设计(IOS篇)-第一季

我写的源文件整个工程会再第二季中发上来~,存在百度网盘, 感兴趣的童鞋, 可以关注我的博客更新,到时自己去下载~.喵~~~ QQChat Layout - 第一季 一.准备工作 1.将假数据messa ...

- 【第一季】CH09_FPGA多路分频器设计

[第一季]CH09_FPGA多路分频器设计 在第七节的学习中,笔者带大家通过一个入门必学的流水灯实验实现,快速掌握了VIVADO基于FPGA开发板的基本流程.考虑到很多初学者并没有掌握好Vivado ...

- 超感猎杀/超感八人组第一季至二季/全集Sense8迅雷下载

本季 Sense8 (2015)看点:<超感八人组>由沃卓斯基姐弟执导的科幻剧集是Netflix继“纸牌屋第二季”后的又一大手笔制作,讲述未来世界不同地区的8个人因同时目睹同一暴力事件.从 ...

- 【第一季】CH08_FPGA_Button 按钮去抖动实验

[第一季]CH08_FPGA_Button 按钮去抖动实验 按键的消抖,是指按键在闭合或松开的瞬间伴随着一连串的抖动,这样的抖动将直接影响设计系统的稳定性,降低响应灵敏度.因此,必须对抖动进行处理,即 ...

- Bootstrap<基础二> 网格系统

Bootstrap 提供了一套响应式.移动设备优先的流式网格系统,随着屏幕或视口(viewport)尺寸的增加,系统会自动分为最多12列. 什么是网格(Grid)? 摘自维基百科: 在平面设计中,网格 ...

- JAVA入门第一季(mooc-笔记)

笔记相关信息 /** * @subject <学习与创业>作业1 * @author 信管1142班 201411671210 赖俊杰 * @className <JAVA入门第一季 ...

随机推荐

- 带下划线的 HTTP Header无法获取到可能是因为nginx

背景:新版本修改了个功能是在老版本的基础上做的,同一个接口,需要兼容老版本,因此让前台在header中封装了 version版本号,client_type 客户端类型,根据这两个字段判断接口要走的逻辑 ...

- jvm 线程状态

NEW: Just starting up, i.e., in process of being initialized.NEW_TRANS: Corresponding transition sta ...

- QMessageBox改变大小

创建一个QMessageBox: QMessageBox msgBox(this);msgBox.setWindowTitle(tr("MailBox Location"));ms ...

- C++的精髓——代码复用、接口复用

C++的精髓——代码复用.接口复用 在另一篇文章中提到C++三大特点的核心概括,也写在这里吧.封装:信息隐藏继承:代码复用多态:面向对象C++并不是面向对象,它包容多种编程思想,如面向过程,面向对象, ...

- uWSGI Apache 处理 惊群效应的方式 现代的内核

Serializing accept(), AKA Thundering Herd, AKA the Zeeg Problem — uWSGI 2.0 documentationhttps://uws ...

- Android 显示系统:Vsync机制

一.Vsync简介: 屏幕的刷新过程是每一行从左到右(行刷新,水平刷新,Horizontal Scanning),从上到下(屏幕刷新,垂直刷新,Vertical Scanning).当整个屏幕刷新完毕 ...

- postgreSQL 之 Privilege & grant & revoke(未完待续)

When an object is created, it is assigned an owner. The owner is normally the role that executed the ...

- 1-18-2 LVM管理和ssm存储管理器使用&磁盘配额 (二)

LVM管理和ssm存储管理器使用&磁盘配额 (二) 内容如下: ü LVM快照 ü ssm存储管理器的使用 ü 磁盘配额 第1章 LVM快照 lvm快照:为了保持系统的一致性,我们先做 ...

- 中国行政区划表,包括34个省、直辖市的所有数据 mysql数据

中国行政区划表,包括34个省.直辖市的所有数据 sql文件地址 https://gitee.com/zwh_9527/ChinaProvince

- 微信小程序---查看更多的显示与隐藏

平时工作中经常遇到开始只显示几行文字,点击按钮,可以查看全部文字内容. 简单写了个,代码如下: <view class="item_content f28 gray"> ...