如何新建Quartus工程—FPGA入门教程【钛白Logic】

这一章我们来实现第一个FPGA工程—LED流水灯。我们将通过流水灯例程向大家介绍一次完整的FPGA开发流程,从新建工程,代码设计,综合实现,管脚约束,下载FPGA程序。掌握本章内容,大家就算正式的开始入门FPGA开发了。

1.1.1.电路说明

1.1.2.新建工程

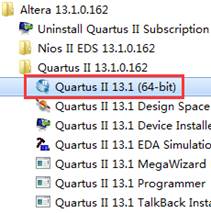

第一步:从开始菜单启动Quartus II 13.1(64 bit) ,如下图。

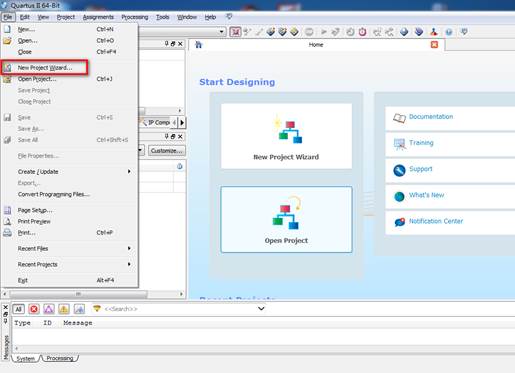

第二步:菜单栏选择File—>New Project Wizard,新建工程。

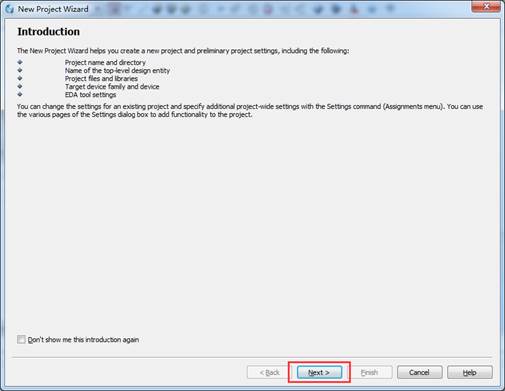

第三步:弹出新建工程对话框,点击Next,下一步。

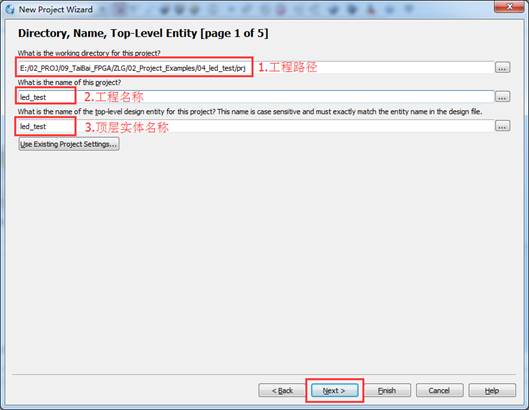

第三步:如下图,依次设置工程的存放路径,工程名称,顶层文件名称,如图依次设置好,这里我们将所有工程相关的文件放在prj文件夹内,便于工程文件与源码文件的管理,同时要保持工程名称与顶层实体名称一致,继续Next。

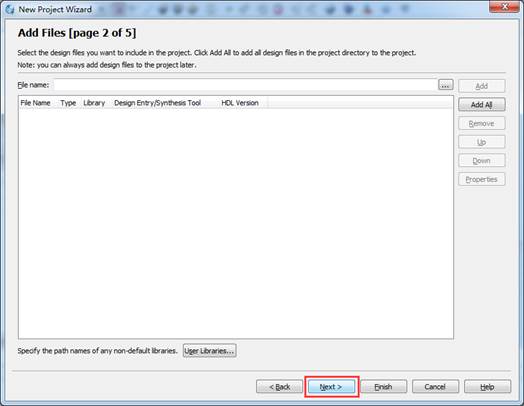

第四步:添加设计文件,这一步我们不需要添加,后续我们会新建相应的代码文件。这里继续Next。

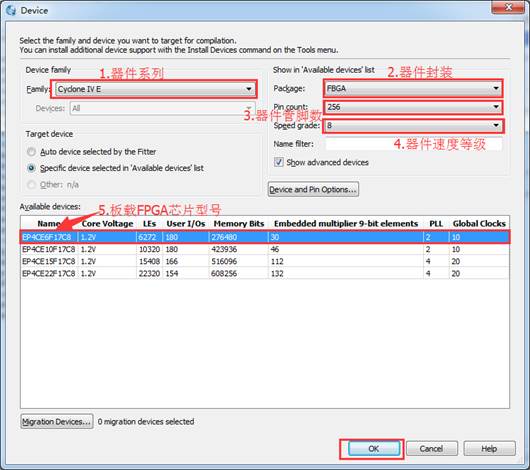

第五步:选择FPGA器件,如图所示,这里我们选择器件家族是CycloneIV系列的,封装是FBGA,管脚数为256,速度等级为8。这里速度等级越小,速度越快。这里我们FPGA的具体型号为EP4CE6F17C8。大家通过这个对话框了解这个器件的基本资源。这里我简单介绍一下这些资源的名称,在后面的章节里我们还会详细讲解FPGA内部资源与结构。

1、CoreVoltage是内核电压,Cyclone IV的内核电压是1.2V。

2、LE是Altera最基本的逻辑单元,LEs表示FPGA的所有的逻辑资源, 我们这款芯片的逻辑资源数为6272。

3、User I/Os表示用户IO数,这里共有180个IO可以供用户使用。

4、Memory Bits与embedded multiplier 9-bit elements实际是一回事,后者简称M9K,M9K就是指位宽为9bit,深度为1K的RAM。这里一共有30个M9K,大家计算一下9*1024*30=276480就是Memory Bits。

5、PLL锁相环,内部一共有两个锁相环。

6、Global clocks全局时钟网络数,这里一共有10个。

第六步:设置EDA工具,这里我们就设置一下仿真工具,使用默认Modelsim

-Altera,语言选择Verilog。实际后面我们不建议大家使用Modelsim-Altera。我们会推荐大家在直接使用Modelsim-SE,后者的通用性更强。继续Next。

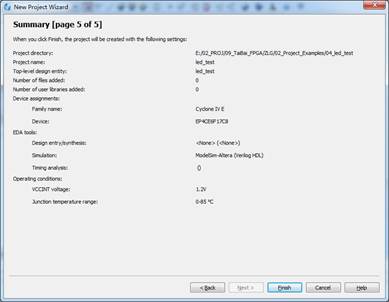

第七步:总结新建工程的基本信息。到这里就完成工程的建立。

1.1.3.代码设计

大家阅读本节前,首先应该对Verilog语法有一定了解,其次阅读我们提供的编码规范文件,了解基本的命名规则和工程架构,从一开始就培养良好的编码习惯。

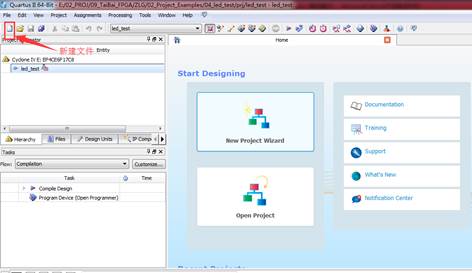

第一步:新建verilog源文件,如下图,点击新建文件图标,或者通过菜单栏File—>New打开新建文件向导。

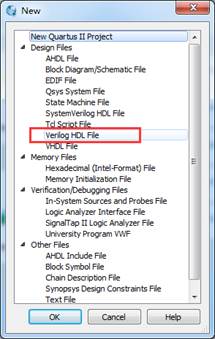

第二步:在新建文件向导中,选择Verilog HDL File,点击OK。

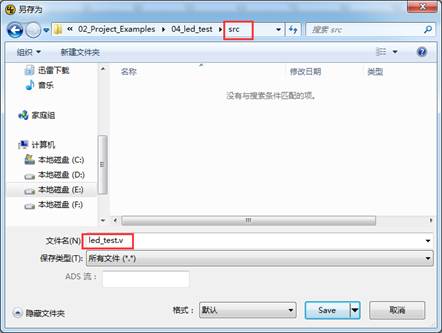

第三步:因为我们已经配置过UltraEdit为默认编辑器,此时会打开UltraEdit(注意:UltraEdit编辑Verilog代码前,要添加语法高亮文件,详见3.3.3节内容),弹出新建源文件,将源文件另存至src文件夹下,命名为led_test.v与顶层实体名称一致。我们将源码文件和工程文件放在不同文件夹下,方便日后的工程维护。

第四步:编写代码逻辑,这里我们实现了一个流水灯。这里我们用了一个27位的计数器,时钟频率为50MHz,周期为20ns,当计数到第25位置位时,计数器值为25’d16777216,此时时间为16777216*20ns=335ms。这样每大约经过335ms,计数器的[26:24]位就会加1。我们第一个always实现计数器,第二个always实现控制不同时间时LED的输出,即每隔335ms改变一次LED的输出状态。

1. module led_test

2. (

3. input i_clk, //input clk ,50mhz

4. input i_rst_n, //reset, active low

5. outputreg [3:0]o_led //led out

6. );

7. reg [26:0] led_count;

8. always @ (posedge i_clk or negedge i_rst_n)

9. begin

10. if(!i_rst_n)

11. led_count <=27'd0;

12. else

13. led_count <=led_count + 27'd1;

14. end

15. always @ (posedge clk or negedge i_rst_n)

16. begin

17. if(!i_rst_n)

18. o_led <=4'b1111;

19. else begin

20. case(led_count[26:24]) //when 25th bit set= 335ms

21. 3'b000: o_led<= 4'b1110;

22. 3'b001: o_led<= 4'b1101;

23. 3'b010: o_led<= 4'b1011;

24. 3'b011: o_led<= 4'b0111;

25. 3'b100: o_led<= 4'b1100;

26. 3'b101: o_led<= 4'b1001;

27. 3'b110: o_led<= 4'b0011;

28. 3'b111: o_led<= 4'b0000;

29. endcase

30. end

31. end

32.endmodule

1.1.4.综合实现

对于刚接触FPGA的同学可能不太了解综合实现的意思,其实简单里说,综合实现就相当于单片机的编译过程。而FPGA的编译过程不像其他高级语言的编译过程,FPGA编译过程实际是相应硬件电路的实现过程。

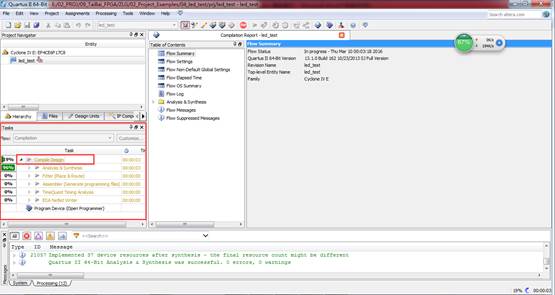

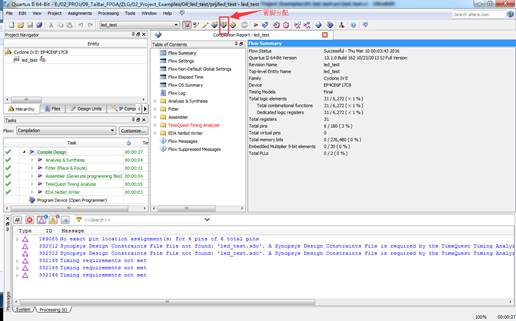

第三小节,我们完成了代码设计,我们就可以综合实现了。步骤就是双击task窗口下的“Compile Design”,就会开始综合实现了。

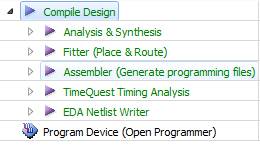

Altera的FPGA编译过程大致分为以下几个过程:分析综合,布局布线,生成烧写文件,时序分析,EDA网表生成。如下图所示。

分析综合:这个过程首先是完成对源码文件的语法编译,其次是将我们设计的语言综合成相应的网表文件,而这个网表文件实际是与FPGA上资源是相互映射的。首先什么是网表文件?网表文件描述了相应工程的FPGA设计中包含了FPGA资源,同样描述了这些资源又是如何连接的。其次,FPGA有哪些资源?我们会在后续章节详细介绍,这里就说一个最简单的资源——触发器,这个是我们数电里面学习过的,在FPGA里一般叫做寄存器。例如我们这个工程中,最终led_count和o_led都会映射到相应的寄存器。

布局布线:这个过程是根据分析综合中得到的网表文件进行的,如果大家有PCB设计经验可能会更好理解。所谓布局,就像PCB布局,将设计中用到的资源布局到FPGA器件内部不同的位置。所谓布线,同样类似PCB布线,将FPGA内部用到的资源根据网表文件中描述的链接关系连在一起。

生成烧写文件:这个过程比较好理解,基于上述过程产生的文件,再生成用烧写FPGA的文件。

EDA网表生成:这个过程则是用来生成仿真所需网表文件。仿真时会用到。

1.1.5.管脚分配

这一节我们将介绍管脚分配,管脚分配过程中我们会同时讲解关于Altera FPGA管脚主要特点及分类。

第一步:管脚分配前应该先将源码文件进行综合,让Quartus获取相应的IO信息。这一步第四小节已经讲了,我就不做详细介绍了。

第二步:打开管脚分配工具Pin Planner,如下图。或者可以通过菜单栏Assignments—>Pin Planner打开,也可以下图所示快捷图标打开。

第三步:分配管脚之前,我们先介绍一下FPGA的IO分布情况、管脚的特点及种类,以及Pin Planner工具的使用。如下图为Pin Planner界面。

Pin Planner工具界面大致可分为以下几个部分:

总体管脚布局区域:如图所示,中间器件图描述了每个管脚的位置。

Report区域:通过这个区域,将相应信息打上√,就可以高亮我们所关心的IO信息。这里我们高亮IO的bank信息。FPGA的管脚是分bank的,而且每个bank的IO的电平都可以独立配置的。

Tasks区域:这个区域包含了很多IO信息,我们可以双击需要的IO信息,相应的信息就会添加到Repoat区域中。

Pin Legend区域:这里具体说明IO的所有种类,并用不同的颜色和形状表示出来。而FPGA的IO管脚大致分为 用户IO,配置管脚,电源管脚这几类。

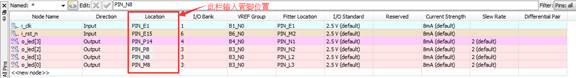

管脚分配区域:我们在这个区域内对我们设计中的IO进行分配。

第四步:分配管脚。在Location栏中输入相应管脚的位置,完成管脚分配。

1.1.6.程序烧写

如何新建Quartus工程—FPGA入门教程【钛白Logic】的更多相关文章

- Quartus II 安装教程—FPGA入门教程【钛白Logic】

Quartus II 工具安装一般分为两个部分,首先是开发工具本身的安装,其次就是器件库的安装,我们可以根据我们的需要选择相应的器件库来安装,这里我们使用Cyclone IV的FPGA,即安装Cycl ...

- Quartus II 破解教程—FPGA入门教程【钛白Logic】

这一节主要说明如何破解Quartus II 13.1.首先找到我们提供的破解工具,这里我们的电脑是64位的,所以使用64位破解器.如下图. 第一步:将破解工具拷贝到安装目录下“D:\altera\13 ...

- 边沿检测方法-FPGA入门教程

本节实验主要讲解FPGA开发中边沿检测方法,我们在设计中会经常用到.这个地方大家一定要理解. 1.1.1.原理介绍 学习HDL语言设计与其他语言不一样,HDL语言设计需要考虑更多的信号的电气特性,时序 ...

- Microsemi Libero系列教程(二)——新建点灯工程

前言 上一篇文章,介绍了Microsemi Libero系列教程(一)-Libero开发环境介绍,下载,安装与注册,作为嵌入式开发中的Hello World,点灯是再也基础不过的实验了,通过点灯实验, ...

- ASP.NET MVC 5 入门教程 (1) 新建项目

文章来源: Slark.NET-博客园 http://www.cnblogs.com/slark/p/mvc-5-get-started-create-project.html 下一节:ASP.NET ...

- Photoshop入门教程(一):文本新建与概念解析

写在开头 <Photoshop实用入门>系列教程可能对于一点都没有接触过Photoshop的人来说不太容易接受,因为本教程并没有细致到教你如何使用画笔工具等一系列很基础的东西,有些地方的讲 ...

- Keil MDK入门---从新建一个工程开始

熟悉Keil C51的朋友对于Keil MDK上手应该比较容易,毕竟界面是很像的.但ARM内核毕竟不同于51内核,因此无论在设置上还是在编程思想上,都需要下番功夫研究的.本文以MDK V4.03为例, ...

- 【小梅哥FPGA进阶教程】MC8051软核在FPGA上的使用

十.MC8051软核在FPGA上的使用 本教程内容力求以详细的步骤和讲解让读者以最快的方式学会 MC8051 IP core 的应用以及相关设计软件的使用,并激起读者对 SOPC 技术的兴趣.本实验重 ...

- [转]Scrapy入门教程

关键字:scrapy 入门教程 爬虫 Spider 作者:http://www.cnblogs.com/txw1958/ 出处:http://www.cnblogs.com/txw1958/archi ...

随机推荐

- 《Linux内核分析》 之 计算机是如何工作的

[李行之原创作品 转载请注明出处 <Linux内核分析>MOOC课程http://mooc.study.163.com/course/USTC-1000029000] <Linux内 ...

- java实验报告一

一.实验内容 1. 使用JDK编译.运行简单的Java程序 2.使用Eclipse 编辑.编译.运行.调试Java程序 二.实验步骤 (一)命令行下Java程序开发 1. 首先双击桌面上的Xface终 ...

- 配置HugePage

翻译自https://www.thegeekdiary.com/centos-rhel-67-how-to-configure-hugepages/ 什么是HugePage HugePages是Lin ...

- Github: 团队账号:https://github.com/ChenRuTing

Github: 团队账号:https://github.com/ChenRuTing 以后我们做好的代码会随时更新上传到这里,请老师届时帮我们看看.谢谢老师.

- Alpha冲刺——day7

Alpha冲刺--day7 作业链接 Alpha冲刺随笔集 github地址 团队成员 031602636 许舒玲(队长) 031602237 吴杰婷 031602220 雷博浩 031602634 ...

- canvas技术整理

canvas技术整理 html <canvas id= "canvas"></canvas> javascript var canvas = documen ...

- 洛谷P13445 [USACO5.4]奶牛的电信Telecowmunication(网络流)

题目描述 农夫约翰的奶牛们喜欢通过电邮保持联系,于是她们建立了一个奶牛电脑网络,以便互相交流.这些机器用如下的方式发送电邮:如果存在一个由c台电脑组成的序列a1,a2,...,a(c),且a1与a2相 ...

- 【设计模式】—— 解释器模式Interpret

前言:[模式总览]——————————by xingoo 模式意图 自定义某种语言后,给定一种文法标准,定义解释器,进行解析. 做过搜索的朋友们可能更了解一些,平时我们搜索所需要的词库,通常就需要用这 ...

- 如何把EntityList转换成DataSet

public static DataSet ToDataSet<TSource>(this IList<TSource> list) { Type elementType = ...

- Spring Shell打Jar包时需要注意的地方

Spring-Shell打Jar包时需要注意的地方: 1.Main-Class spring-shell项目打Jar包的一个必要条件就是,指定Main-Class为org.springframew ...