为什么现在使用多周期CPU,而单周期CPU被弃用?

最初设计的CPU结构简单,内部不复杂。之所以制造它是为了让机器自动跑程序,算数。

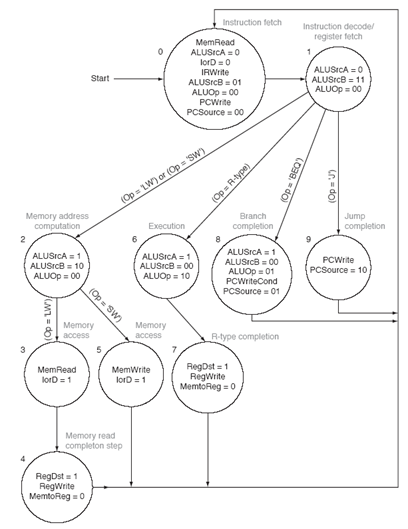

早期CPU都是单周期的,人们没考虑那么多,性能啥的。就让CPU每个时钟周期跑一个指令,这些时钟周期等长。这样下来,有的指令跑完耗时长,有的指令跑完耗时短, 而CPU是走完一条指令再处理下一条的,给每个指令的时钟周期都是相同的,那么木桶原理,时钟周期肯定就是耗时最长的指令所需的时间。后来人们意识到了计算机的巨大威力,便开始专心制造更强的电子计算机。这时,为了提升CPU的速度,优化CPU的结构,有人设计了一套多周期CPU结构。对指令集的所有指令作分析,可以发现它们处理过程有相同的地方,那这下好了,我把所有的指令切成几段基本操作(换句话说,所有的指令都可以看成是几个基本操作的序列组成),例如:指令1可以看成{opA——>opC——>opV},指令2可以看成{opA——>opK——>opV——>opT}。然后让时钟周期适配op,而不是单条指令。每个指令需要多个周期(周期值较小)。这里的多周期CPU依然是逐条执行每个指令。下图为一个多周期CPU的控制器状态自动机。

举例对比上面所述单周期CPU和多周期CPU的耗时:

CPU的指令集Ins中有多条指令,指令4耗时最长,执行一次它需要800ps。

单周期CPU的时钟周期最少设为800ps。此时假如我们要执行指令1,2,3,4,5,6,那么总共耗时6x800ps=4800ps。

多周期CPU,分别可以把指令123456分解为3个op,2个op,4个op,8个op,3个op,5个op。每个op延时为100ps。那么假如我们要执行指令1,2,3,4,5,6,则总共耗时为(3+2+4+8+3+5)x100ps=2500ps。

这样一对比多周期CPU相较于单周期CPU的优势是不是很明显啦。

在这之后,有人发现了上面所说的多周期CPU还可以改进优化提速,他把流水线的思想拿到了CPU设计上,允许指令并行执行,这样一来速度又得到了提升。现在的CPU基本都是使用流水线技术设计的CPU。

为什么现在使用多周期CPU,而单周期CPU被弃用?的更多相关文章

- verilog实现的16位CPU单周期设计

verilog实现的16位CPU单周期设计 这个工程完成了16位CPU的单周期设计,模块化设计,包含对于关键指令的仿真与设计,有包含必要的分析说明. 单周期CPU结构图 单周期CPU设计真值表与结构图 ...

- 单周期CPU设计的理论基础

写在前面:本博客内容为本人老师原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文! 本博客全网唯一合法UR ...

- 单周期CPU设计

终于有点时间了,恰好多周期的设计也已经完成,其实只想写写多周期的,无奈单周期补上才好,哈哈哈~ —————+—————黄金分割线—————+————— 首先要理解什么叫单周期CPU(与后面多周期CPU ...

- 单周期cpu设计代码解读

目录 写在前面 单周期cpu设计代码讲解 概念回顾 Verilog代码讲解 写在前面 欢迎转载,转载请说明出处. 单周期cpu设计代码讲解 概念回顾 一.电子计算机的部件 分为:中央处理器(cpu). ...

- P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2.p3.p4.p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽 ...

- 单周期CPU

一个时钟周期执行一条指令的过程理解(单周期CPU): https://blog.csdn.net/a201577F0546/article/details/84726912 单周期CPU指的是一条指令 ...

- 使用logisim搭建单周期CPU与添加指令

使用logisim搭建单周期CPU与添加指令 搭建 总设计 借用高老板的图,我们只需要分别做出PC.NPC.IM.RF.EXT.ALU.DM.Controller模块即可,再按图连线,最后进行控制信号 ...

- 使用Verilog搭建一个单周期CPU

使用Verilog搭建一个单周期CPU 搭建篇 总体结构 其实跟使用logisim搭建CPU基本一致,甚至更简单,因为完全可以照着logisim的电路图来写,各个模块和模块间的连接在logisim中非 ...

- Verilog单周期CPU(未完待续)

单周期CPU:指令周期=CPU周期 Top模块作为数据通路 运算器中有ALU,通路寄存器(R1.R2.R3.R4),数据缓冲寄存器(鉴于书上的运算器只有R0)........... 此为ALU和通用寄 ...

随机推荐

- [考试反思]1109csp-s模拟测试107:低能

诶一看这不是水题AK场吗?然后80分钟就拿到了285分. 然后,对拍?还是卡T2常数?还是想T2正解? 于是上述三项我依次进行了. 前两项让我的分数丝毫不变但是吃掉了我一个多小时的时间. 卡常卡的也不 ...

- [考试反思]0815NOIP模拟测试22

40分,15名. 1-4:120 75 70 70 35分20名...总之差距极小不想说了 昨天教练说:以后的考试还是联赛知识点,但是难度比联赛高. 没听进去,以为是对于所有人而言的,也就是T1难度变 ...

- CSPS模拟 84

整场考试就一个字虚 真的啥也不会 T1 80很好打 可是100这鬼畜的数据范围...二分答案? 没做过蚯蚓跪..果然多刷题有好处.. 于是死在80分处 T2 56很好打 可是100这鬼畜....... ...

- 考试T2修剪草坪

传送门 这题的DP真是刷新了我的理解,竟然还要用队列优化.... #include<iostream> #include<cstdio> using namespace std ...

- 当 Redis 发生高延迟时,到底发生了什么

Redis 是一种内存数据库,将数据保存在内存中,读写效率要比传统的将数据保存在磁盘上的数据库要快很多.但是 Redis 也会发生延迟时,这是就需要我们对其产生原因有深刻的了解,以便于快速排查问题,解 ...

- 爬虫学习--Day4(网页采集器的实现)

#UA: User-Agent {请求载体的身份标识}#(反爬机制)UA检测:门户网站的服务器回检测对应请求的载体身份标识,如果检测到请求的载体身份为某一款浏览器就说明该请求时一个正常的请求.但是,如 ...

- 数组去重(高效率,ES6才支持)

//数组去重 function distinct(arr) { let result = []; let obj = {}; for(let i of arr) { if(!obj[i]) { res ...

- c#数据结构之Array、ArrayList、List、LinkedList对比分析

一.前言: 在c#数据结构中,集合的应用非常广泛,无论是做BS架构还是CS架构开发,都离不开集合的使用,比如我们常见的集合包括:Array.ArrayList.List.LinkedList等.这一些 ...

- k8s部署高可用Ingress

部署高可用Ingress 官网地址https://kubernetes.github.io/ingress-nginx/deploy/ 获取ingress的编排文件 wget https://raw. ...

- [Verilog] 从系统时钟转换出想要的时钟

如何50MHZ时钟转换出一个250KHZ的时钟出来? 假如系统时钟是50MHZ,然后想得到250KHZ的新时钟,那么50MHZ / 250KHZ = 200倍,然后令k=200,程序如下: ; :] ...