(原创)Spice 网表范例

一、常规网表

Inverter

.lib "D:\lib\l0040ll_v1p4_1r.lib" TT .param SUPPLY=.1V

.param T=10ns

.param dt=.02ns

.temp

.global VDD VSS

.option MEASDGT= post *MEASDGT=3表示输出结果保留3位有效数字 VVDD VDD 'SUPPLY' *********** 反相器 ****************

.subckt Inverter

*Inputs

+ in

*Supply

+ VDD GND

*Outputs

+ out XP1 out in VDD VDD p11ll_ckt W=200n L=40n

XN1 out in GND GND n11ll_ckt W=120n L=40n .ends

******************************************** X_Inverter

*Inputs

+ in

*Supply

+ VDD GND

*Outputs

+ out

+ Inverter C_load out 1.5f *Vin in PWL(0n 0V,"T-dt" 0V , T SUPPLY , "2*T-dt" SUPPLY, "2*T" 0V , "3*T-dt" 0V) *--

Vin in PULSE( SUPPLY "T*0.5" 0n 0n "T*0.5" T) _| ̄|_ *测量语句

.Measure tran V_in find V(in) when V(out)="0.1*SUPPLY" rise= .Measure tran pwr AVG P(VVDD) From=0ns To="3*T-dt" .Measure tran Tr trig V(out) val='0.1*SUPPLY' rise=

+ targ V(out) val='0.9*SUPPLY' rise= *瞬态扫描语句

.tran .001n "6*T"

*+ sweep monte=

+ sweep SUPPLY .6V .1V .1V *.print tran V(in) V(out) .probe v(*)

.end

二、直流分析网表

HSPICE demo .LIB ".\cmos25_level49.lib" TT .temp

.plot DC I(M0) VVSS VSS

VVDS D VSS

VVGS G VSS 0.5 .dc VVDS 0.1 sweep VVGS 0.5 2.5 0.5

M0 D G VSS VSS nmos L=.5u W=.8u .end

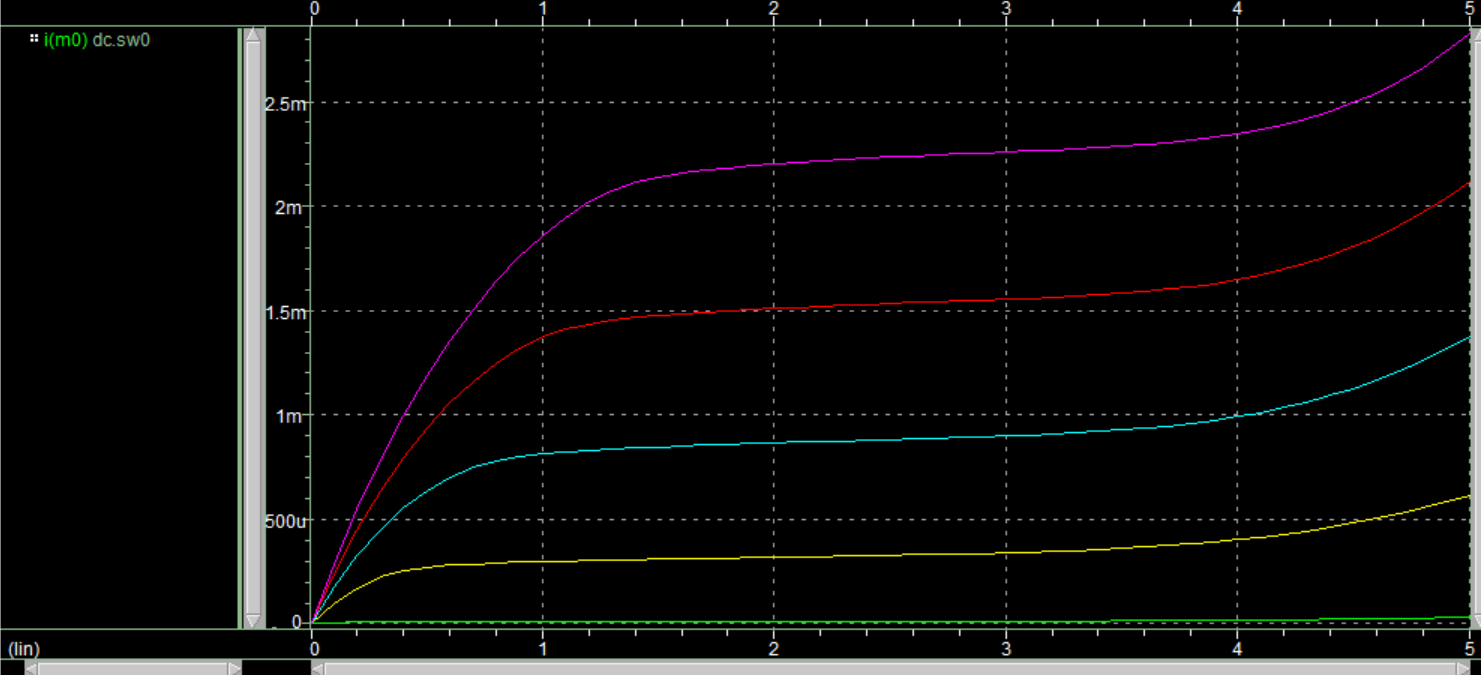

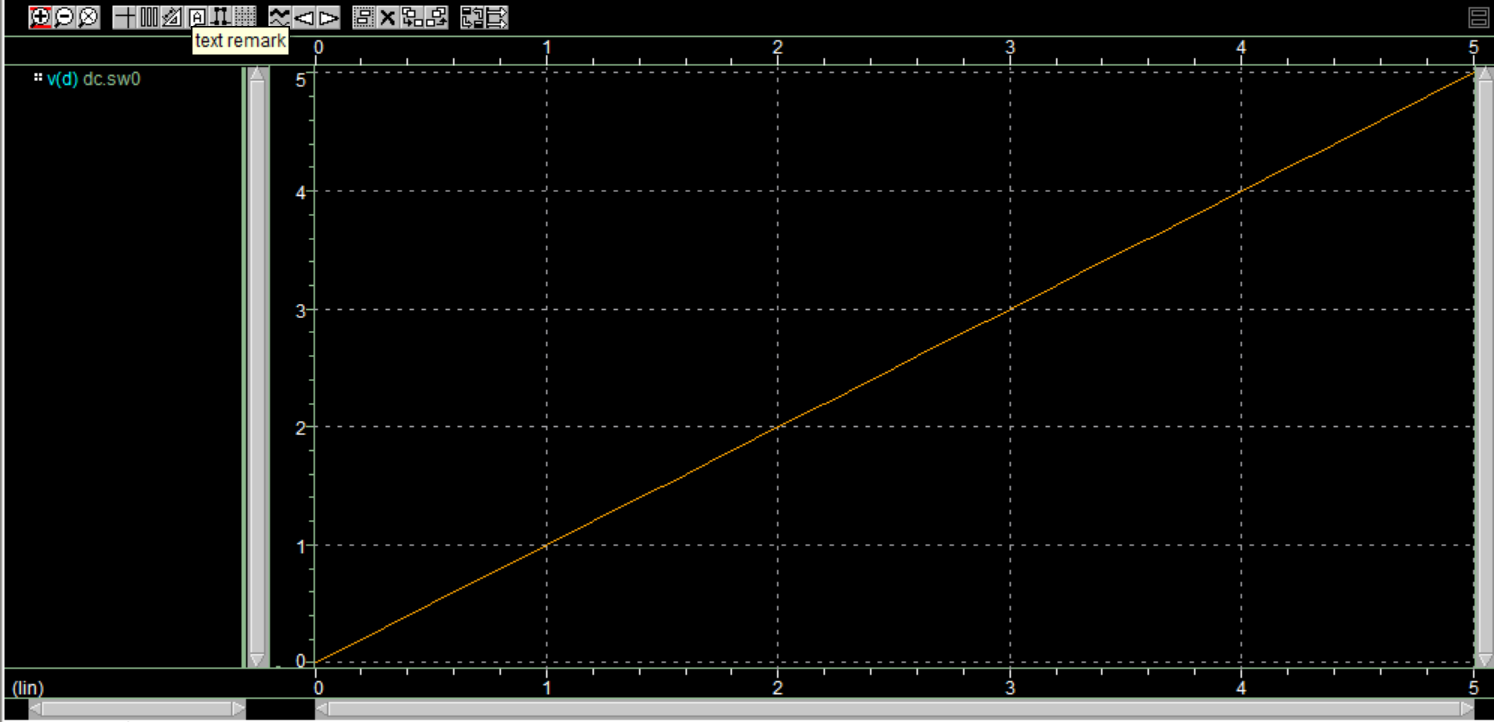

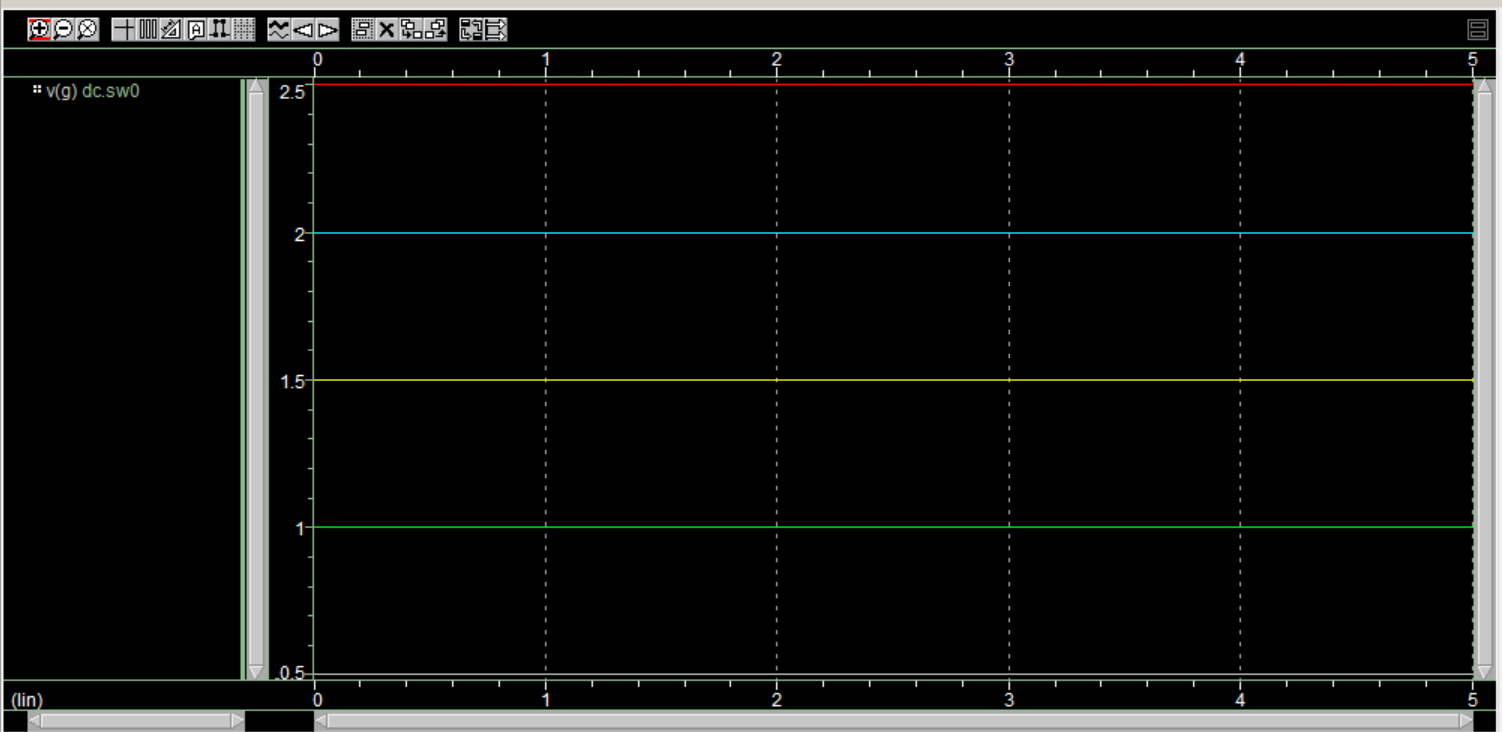

打开生成的.sw0文件可以看到如下的波形:

Ids:

Vd:

Vg:

(原创)Spice 网表范例的更多相关文章

- 【黑金原创教程】【TimeQuest】【第二章】TimeQuest模型角色,网表概念,时序报告

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- 【黑金原创教程】【TimeQuest】【第五章】网表质量与外部模型

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- (原创)详解Quartus导出网表文件:.qxp和.vqm

当项目过程中,不想给甲方源码时,该如何?我们可以用网表文件qxp或者vqm对资源进行保护. 下面讲解这两个文件的具体生成步骤: 一.基本概念 QuartusII的qxp文件为QuartusII Exp ...

- 15.导入网表及status介绍[原创]

一.导入网表 在导入网表之前你的封装需确认是在你的封装路径下 建立Board工程后: ① ② ③ ④放置器件 ⑤ (切记,封装路径一定要添加) 二.status介绍 --- (常用) -------- ...

- [转载][FPGA]Quartus代码保护-生成网表文件

0. 简介 当项目过程中,不想给甲方源码时,该如何?我们可以用网表文件qxp或者vqm对资源进行保护. 下面讲解这两个文件的具体生成步骤: 1. 基本概念 QuartusII的qxp文件为Quartu ...

- cadence16.6 中orcad导出网表时ERROR (ORCAP-5004)

ORCAD网表输出时 ERROR (ORCAP-5004):Error initializing COM property pages 之前遇到过这个问题,解决后忘了记录下来了.依稀记得问题答 ...

- 用Modelsim仿真QuartusII综合后网表时库的添加方法(转)

这两天做综合后仿真,发现FPGA器件库又不会加了,无奈上网找方法.说起来不好意思,很早就接触Modelsim这个仿真软件了,可是没有好好琢磨.把这两天找的方法贴出来,再加上自己的理解,以后忘了可以上博 ...

- hive建表范例

建表范例:支持update和delete create table aaa( id string, visitor_name string ) clustered by(id) into bucket ...

- OrCAD生成网表

1. 先选中.dsn设计文件 2. 按照默认设置,点击OK即可生成网表

随机推荐

- 远程连接bat

@Echo offSet SERVER=10.40.61.101Set USERNAME=AdministratorSet PASSWORD=Marvin2008 Cmdkey /generic:TE ...

- jdbc、jpa、spring data jpa、hibernate、mybatis之间的关系及区别

基础概念 jdbc(Java DataBase Connectivity)是java连接数据库操作的原生接口.JDBC对Java程序员而言是API,对实现与数据库连接的服务提供商而言是接口模型.作为A ...

- php 两次encodeURI,解决浏览器跳转请求页乱码报错找不到页面的bug

Not Found The requested URL /index.php/XXX/mid/97329240798095910/bname/3000T/D/sname/水泥粉磨/un ...

- springboot返回页面

1.使用@Controller注解: @Controller必须配合模板 先导入依赖: <dependency> <groupId>org.springframework.bo ...

- zzw_非root用户安装python3.5

目的:不想改变linux 自带的python,只想要用特定的非root用户运行特定版本的python 1.进入非root用户 2.新建一个python3.5的安装目录 [a4_csbdc@bdc816 ...

- [转]java 关于httpclient 请求https (如何绕过证书验证)

原文:http://www.blogjava.net/hector/archive/2012/10/23/390073.html 第一种方法,适用于httpclient4.X 里边有get和post两 ...

- 了解计算机与操作系统发展阶段以及android操作系统的发展史

计算机与操作系统发展阶段 计算机的发展: 第一代(1946-1957年),电子管计算机 第二代(1958-1964年),晶体管计算机 第三代 (1964—1970年),集成电路数字机 第四代 (19 ...

- css的position属性

position: relative:保持未定位前的位置不变,若给了left,top的值,那么就会相对于原来的位置进行移动 absolute:元素原先在正常文档流中所占的空间会关闭,就好像元素原来不存 ...

- PHP语言学习之php-fpm 三种运行模式

本文主要向大家介绍了PHP语言学习之php-fpm 三种运行模式,通过具体的内容向大家展示,希望对大家学习php语言有所帮助. php-fpm配置 配置文件:php-fpm.conf 开启慢日志功能的 ...

- 小谈对Python的认知与期望

18级新生,在大学之前并未接触过程序语言编程,在众多语言编程中只对C语言有个名字上认知.在上个学期初次了解到Python语言,计算机老师表示Python是现在编程语言中如雨后春笋般的发展飞速的计算机语 ...