ROM存储1/4周期正弦信号构造DDS

简单的dds程编写过程中我遇到问题以及一些个人的思考。初次接触FPGA,如有问题请多多指教~

1.几个疑问,解决和没有解决的。

为何采用ROM而不是直接采用DDS核来进行正弦信号的合成?

实际中如果只需要合成正弦信号,那么DDS核是一个很好的选择,而且DDS核可以选择是否采用泰勒校正以获取更低的杂散。由于ROM表中的数据可以由我们自己选择,采用ROM做DDS具有更强的灵活性。

在使用chipscope时,添加ICON核和.cdc文件的区别?

ICON核的添加需要改变原有程序的结构,需要重新综合,正是由于这个核在程序内部,我们可以轻易地选择需要观察的信号;

.cdc文件的插入不改变程序结构,只需要重新translate等,由于是对综合后的程序进行插入,所以有些信号会被优化掉或者改名字等。

双口ROM有无缺陷?

不知道……modelsim反正中表明,无法仿真collision等……Block Ram的手册中没有提到双口ROM,也许看看双口RAM会有帮助。

2.Matlab仿真

注意:由于采用了1/4周期存储,要求整个周期的数值是中心对称的,半个周期的数值是轴对称的。这就意味着采样点中不应该有0值得存在。

Matlab仿真——ROM表存储数据

%% ROM产生 (无符号数)

ROM_N=^; %ROM表深度

DATA_L=; %ROM位宽

t=:ROM_N;

y=(^DATA_L-)*(sin(*pi*(t-0.5)/ROM_N/));%-.5保证对称性 ROM_DATA=round(y);

Matlab仿真——DDS程序(请原谅我没有用case……)

%% 正弦波dds产生

F_CLK=*^; %时钟频率10M

PINC_IN_L=; %增量长度

DDS_CLK=*^; %dds输出频率10k

PHASE_IN=; %初始相位

pinc=round(DDS_CLK*^PINC_IN_L/F_CLK); %相位增量 SIM_L=; %仿真长度

phase=PHASE_IN+pinc*(:SIM_L-);

addr=mod((floor(phase/^PINC_IN_L*ROM_N)),ROM_N*);

flag=floor(addr/ROM_N);

dds_out=:SIM_L;

for i=:SIM_L

if(flag(i)==)

dds_out(i)=ROM_DATA(addr(i)+);

else if(flag(i)==)

dds_out(i)=ROM_DATA(-addr(i)+);

else if(flag(i)==)

dds_out(i)=-ROM_DATA(addr(i)-+);

else

dds_out(i)=-ROM_DATA(-addr(i)+);

end

end

end

end plot(dds_out);

3.DDS的解释

Xilinx的DDS核的User Guide中队DDS做了很详细的说明,本节不再重复此内容,本节将叙述一种全新的DDS理解方式。这种理解方式解决了频率控制字长于ROM表深度时DDS的理解上的问题。

连续还是离散?

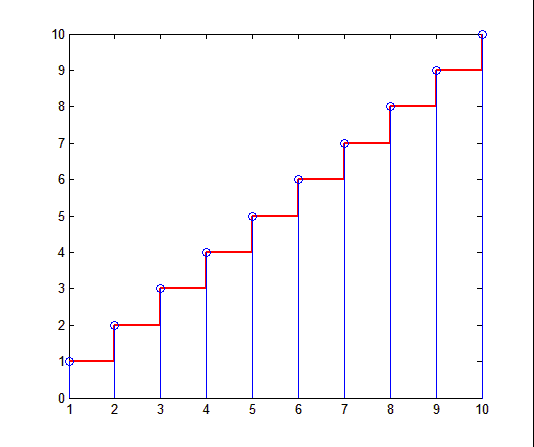

连续还是离散,在于我们用什么眼光去看待。如下图所示,我们可以理解蓝色的图是离散的,而红色的线是连续的。然而,对于我们要获取的信息而言,这两幅图是完全没有区别的。抽样定理中有理想抽样和平顶抽样(采样保持电路)之分,然而在频域效果上,是并没有很大区别的。

ROM表存储的是连续的数值

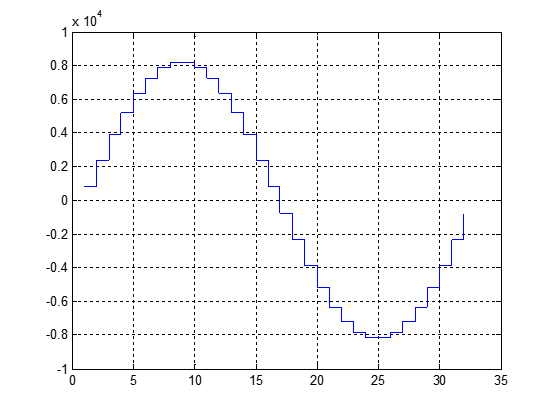

按照上面的理论,可以认为ROM表中存储的是正弦信号的平顶采样结果。如下图所示(一个全周期的ROM表,对称性满足1/4周期存储的要求)

上图的频谱在信号与系统中有提及,上述波形的形成方式可以认为是在乘以周期为T的冲击函数,之后卷积一个宽度为T的窗函数。对应可以求得其频域。(具体可参考平顶抽样)

频率控制字

频率控制字控制对上述的阶梯函数的采样,如果这样理解的话,就没有所谓的相位截取取ROM表的值的疑惑了。频谱图能够清晰的表现这一过程,然而由于blog表达不便,此处不做详细说明。

此处能够解释DDS产生的杂散。

4.Verilog实现

从设计设计上来说,Verilog和Matlab代码应该完全一致,包括代码编写的思路,以及命名都应该统一。但是下面的程序没有做到这一点,带改进。

`timescale 1ns / 1ps module DDS_10k(

input clk_10M,

input rst,

output[:] D_SIN,

output[:] D_COS

); parameter pinc='d4294967; //10k

reg[:] addr_temp='d0;

reg[:] addra,addrb;

reg mark_a,mark_b; always@(posedge(clk_10M)) //复位

begin

if(rst==)

addr_temp<='d0;

else

addr_temp<=addr_temp+pinc;

end always@(posedge(clk_10M)) //1/4周期控制

begin

case(addr_temp[:])

'b00:

begin

addra<=addr_temp[:];

mark_a<=;

addrb<=~addr_temp[:];

mark_b<=;

end

'b01:

begin

addra<=~addr_temp[:];

mark_a<=;

addrb<=addr_temp[:];

mark_b<=;

end

'b10:

begin

addra<=addr_temp[:];

mark_a<=;

addrb<=~addr_temp[:];

mark_b<=;

end

'b11:

begin

addra<=~addr_temp[:];

mark_a<=;

addrb<=addr_temp[:];

mark_b<=;

end

endcase

end //ROM表读取

ROM_SIN_1k18 rom_dds (

.clka(clk_10M), // input clka

.addra(addra), // input [9 : 0] addra

.douta(D_SIN[:]), // output [12 : 0] douta

.clkb(clk_10M), // input clkb

.addrb(addrb), // input [9 : 0] addrb

.doutb(D_COS[:]) // output [12 : 0] doutb

); reg sin_mark_temp;

reg cos_mark_temp;

assign D_SIN[]=sin_mark_temp;

assign D_COS[]=cos_mark_temp; //此处ROM没有添加register,因此输出和地址有一个周期的延时,故Mark也要有一周期延时

always@(posedge(clk_10M))

begin

sin_mark_temp<=mark_a;

cos_mark_temp<=mark_b;

end endmodule

ROM存储1/4周期正弦信号构造DDS的更多相关文章

- FPGA例化ROM存储表格

FPGA例化ROM存储表格 1.选择ROM 2.填写数据位宽和深度 3.加载ROM初始化信息,coe文件

- Python科学计算(两)——时域波形和正弦信号的频谱

Python科学计算(两)-- 时域和频域波形为正弦波形信号生成.计算和显示 # -*- coding: utf-8 -*- import numpy as np import matplotlib. ...

- Matlab 周期方波信号傅里叶级数展开

方波信号为: 傅里叶级数展开为: 程序运行结果: 程序代码: clear x = -6:0.01:6; T = 4; f = x; for N = 1:length(f) temp = rem(abs ...

- matlab 正弦信号产生

fs=2400;%设定采样频率N=1000; %采样的点数n=0:N-1;t=n/fs; %1/fs相当于隔多长时间才一个点f1=50;%设定争先信号频率xn=sin(2*pi*f1*t);figur ...

- Linux系统编程(24)——信号的生命周期

信号生命周期为从信号发送到信号处理函数的执行完毕. 对于一个完整的信号生命周期(从信号发送到相应的处理函数执行完毕)来说,可以分为三个重要的阶段,这三个阶段由四个重要事件来刻画:信号诞生:信号在进程中 ...

- MATLAB实现连续周期信号的频谱分析(正余弦波信号举例)

关于MATLAB实现连续信号的频谱分析,以正余弦波信号频谱分析为例分析如下: 1.含有频率f ,2f和3f的正弦波叠加信号,即: 其中,f =500Hz.试采用Matlab仿真软件对该信号进行频谱分析 ...

- MATLAB信号与系统分析(五)——连续时间信号的频谱分析

一.实验目的: 1.掌握傅立叶级数(FS),学会分析连续时间周期信号的频谱分析及MATLAB实现: 2.掌握傅立叶变换(FT),了解傅立叶变换的性质以及MATLAB实现. 二.利用符号运算求傅里叶级数 ...

- 傅立叶级数(Fourier Series)和周期现象

一.前言 如果你仔细观察,工作和生活中充满了周期现象:旁边linux driver工程师在调试audio driver的时候播放的1kHz的正弦信号,周末去公园游玩,游船推开水面的波纹,硬件工程师调试 ...

- MATLAB信号与系统分析(一)——连续时间信号与系统的时域分析

一.连续时间信号的表示: 1.向量表示法: 在MATLAB中,是用连续信号在等时间间隔点的样值来近似表示连续信号,当取样时间间隔足够小时,这些离散的样值就能较好地近似出连续信号. 对于连续时间信号f( ...

随机推荐

- js中 字符串与Unicode 字符值序列的相互转换

一. 字符串转Unicode 字符值序列 var str = "abcdef"; var codeArr = []; for(var i=0;i<str.length;i++ ...

- SQL 注入防御方法总结

SQL 注入是一类危害极大的攻击形式.虽然危害很大,但是防御却远远没有XSS那么困难. SQL 注入可以参见:https://en.wikipedia.org/wiki/SQL_injection S ...

- thumbnailator图片处理

一.简介 thumbnailator是一个用来对图片对象进行操作的Java类库.通过它我们可以很方面的使用代码的方式,对图片进行一些操作.如缩放,裁减,旋转,水印等.thumbnailator项目主页 ...

- 续Gulp使用入门-综合运用>使用Gulp构建一个项目

这是我的文件目录结构图 下面是我gulpfile.js的配置 'use strict' var gulp=require('gulp'); var gutil=require('gulp-util' ...

- hdu 2196 Computer 树形dp模板题

Computer Time Limit: 1000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others) Total S ...

- MAC、IDFA、IMEI正则表达式

一.安卓: MAC:接入网络的设备的序号,唯一值.用 16 进制数表示,由 0-9,A-F 组成,如:44:2A:60:71:CC:82 Uuid 正则表达式: ^([0-9a-fA-F]{2})(( ...

- 边工作边刷题:70天一遍leetcode: day 77

Paint House I/II 要点:这题要区分房子编号i和颜色编号k:目标是某个颜色,所以min的list是上一个房子编号中所有其他颜色+当前颜色的cost https://repl.it/Chw ...

- codeforces 711E E. ZS and The Birthday Paradox(数学+概率)

题目链接: E. ZS and The Birthday Paradox. time limit per test 2 seconds memory limit per test 256 megaby ...

- bzoj-2748 2748: [HAOI2012]音量调节(dp)

题目链接: 2748: [HAOI2012]音量调节 Time Limit: 3 Sec Memory Limit: 128 MB Description 一个吉他手准备参加一场演出.他不喜欢在演出 ...

- MySQL数据库学习笔记(四)----MySQL聚合函数、控制流程函数(含navicat软件的介绍)

[声明] 欢迎转载,但请保留文章原始出处→_→ 生命壹号:http://www.cnblogs.com/smyhvae/ 文章来源:http://www.cnblogs.com/smyhvae/p/4 ...