[转] 基本RS触发器

在触发器中,最简单的触发器是基本RS触发器,它由两个与-非门(或者两个或-非门)来组成。

图5.2.1(a)是由与-非门构成的基本RS触发器,由图看出,基本RS触发器有两个输入端( 和

和 )和两个输出端(

)和两个输出端( 和

和 ),门G1和G2的组成有对称性, G1的输出经过G2的传输后回送到G1的另一个输入端,G2的输出经过G1的传输后回送到G2的另一个输入端,正是有了这样的反馈通道才使其具有了存储特性,也有别于前面所讲到的组合逻辑电路。通常将它们的电路结构画成图5.2.1(b)的形式,与

),门G1和G2的组成有对称性, G1的输出经过G2的传输后回送到G1的另一个输入端,G2的输出经过G1的传输后回送到G2的另一个输入端,正是有了这样的反馈通道才使其具有了存储特性,也有别于前面所讲到的组合逻辑电路。通常将它们的电路结构画成图5.2.1(b)的形式,与 相连的输出端称为

相连的输出端称为 ,与

,与 相连的输出端称为

相连的输出端称为 。

。

定义输出端的状态: ,

, 时,为触发器的1状态;

时,为触发器的1状态; ,

, ,为触发器的0状态。触发器处与1状态或0状态时输出端都有互补性。下面具体分析两个输入端对输出端的影响情况。

,为触发器的0状态。触发器处与1状态或0状态时输出端都有互补性。下面具体分析两个输入端对输出端的影响情况。

(1)当 ,

, 时,

时, ,

, ,触发器为0状态;

,触发器为0状态;

(2)当 ,

, 时,

时, ,

, ,触发器为1状态;

,触发器为1状态;

(3)当 ,

, 时,触发器两个输出端的值不变,触发器保持为原来的状态;

时,触发器两个输出端的值不变,触发器保持为原来的状态;

(4)当 ,

, 时,

时, ,

, ,此时触发器的输出端既不是定义的1状态,也不是定义的0状态,破坏了

,此时触发器的输出端既不是定义的1状态,也不是定义的0状态,破坏了 和

和 的互补特性,实际使用时应该避免这种现象的产生。因为在

的互补特性,实际使用时应该避免这种现象的产生。因为在 和

和 的有效信号同时消失时,即

的有效信号同时消失时,即 和

和 同时从0变到1时,输出端的值不确定。

同时从0变到1时,输出端的值不确定。

下面分析当 和

和 同时从0转变到1时,输出端的情况。假设G1的传输时延小于G2的传输时延,在

同时从0转变到1时,输出端的情况。假设G1的传输时延小于G2的传输时延,在 由0变为1时,即G1的输出先变为0,其值反过来影响到G2的输出,使

由0变为1时,即G1的输出先变为0,其值反过来影响到G2的输出,使 的值仍然保持为1;另一种假设就是G2的传输时延小于G1的传输时延,在

的值仍然保持为1;另一种假设就是G2的传输时延小于G1的传输时延,在 由0变为1时,即G2的输出先变为0,其值反过来影响到G1的输出,使

由0变为1时,即G2的输出先变为0,其值反过来影响到G1的输出,使 的值仍然保持为1。用图5.2.2可以说明在

的值仍然保持为1。用图5.2.2可以说明在 和

和 同时从0变为1时,输出端逻辑值的不确定情况,从图中可以看出,在这种情况下,门电路传输时延小的门电路其输出端的值会发生变化,而门电路传输时延大的门电路逻辑门其输出端的值不会发生变化。

同时从0变为1时,输出端逻辑值的不确定情况,从图中可以看出,在这种情况下,门电路传输时延小的门电路其输出端的值会发生变化,而门电路传输时延大的门电路逻辑门其输出端的值不会发生变化。

由以上分析可知, 和

和 的低电平同时消失时,在门电路传输时延未知的情况下,输出端状态是不确定的。在通常使用RS触发器时,应该避免这种情况的出现,一般不要让

的低电平同时消失时,在门电路传输时延未知的情况下,输出端状态是不确定的。在通常使用RS触发器时,应该避免这种情况的出现,一般不要让 和

和 同时为0。所以,在正常工作的条件下,用式

同时为0。所以,在正常工作的条件下,用式 +

+ =1来约束两个输入端,称为约束条件。

=1来约束两个输入端,称为约束条件。

在正常工作时,输出端 和

和 具有互补的特性,

具有互补的特性, 是低电平使输出端

是低电平使输出端 为0,

为0, 也是低电平才使输出端

也是低电平才使输出端 为1。所以

为1。所以 是低电平有效置0(

是低电平有效置0( ),置0也称为触发器复位,

),置0也称为触发器复位, 端称为复位端。

端称为复位端。 是低电平有效置1(

是低电平有效置1( ),置1也称为触发器置位,

),置1也称为触发器置位, 端称为置位端。

端称为置位端。

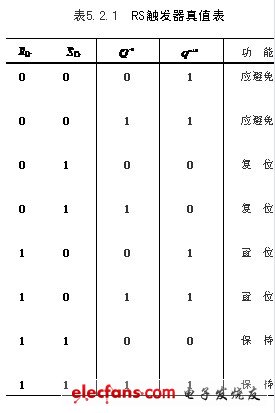

对于RS触发器输入和输出的逻辑关系,可以通过逻辑状态转移真值表来加以描述。如表5.2.1所示,真值表中考虑了触发器在 和

和 信号作用前的输出状态值,即触发器的初态

信号作用前的输出状态值,即触发器的初态 ,得到的新的状态记作

,得到的新的状态记作 。

。

表5.2.1可以写成逻辑状态转移表的形式,如表5.2.2的所示,亦称为逻辑状态转移表,还可以将其转换为卡诺图的形式,如图5.2.3所示。卡诺图中的“×”表示约束项,即约束条件 +

+ =1。

=1。

经过化简卡诺图后得到(5.2.1)式,这就是RS触发器的特性方程(也称为状态方程和或次态方程)。从特性方程中可以看出,输出端新的状态 与前一状态

与前一状态 有关,这是组合逻辑电路所不具有的特点。

有关,这是组合逻辑电路所不具有的特点。

图5.2.4为与-非门RS触发器状态转换图,图中“×”在此表示任意项,它用图形的方式描述了触发器状态间的转换情况。图5.2.5为与-非门RS触发器的逻辑符号。

例5.2.1 用与-非门组成的RS触发器中,已知输入端的波形如图5.2.6所示,试画出输出端 和

和 的电压波形图。

的电压波形图。

解: 在用与-非门组成的RS触发器中,输入端是低电平有效复位和置位,根据这一特性可以画出其输出波形。在图中必须注意 和

和 端同时出现了低电平,但是其低电平值不是同时消失的,所以输出端的值是可以确定的。

端同时出现了低电平,但是其低电平值不是同时消失的,所以输出端的值是可以确定的。

用或-非门也可以组成RS触发器,其电路结构和逻辑符号见图5.2.7(a)、(b),与前面与-非门组成的RS触发器相比,其输入端是高电平有效复位和置位。如果RS同时从高电平变到低电平时,输出的状态

是不确定的,所以其相应的约束条件为:RDSD=0。图5.2.7(c)是其卡诺图,利用约束条件化简得其特性方程为(5.2.2)式。

(5.2.2)

(5.2.2)

(原文地址:http://www.elecfans.com/book/story.php?id=621)

[转] 基本RS触发器的更多相关文章

- R-S触发器

下面是触发器的电路,这个电路上下对称,分别都是一个或门连着一个非门,特别之处在于,它们各自的输出又分别是对方的输入. 合上R,上面的或门输入时1.0,经过上面的非门,Q=0,Q不发光.Q的结果会被反馈 ...

- 数字电路技术之触发器(基本RS触发器)

一.触发器的知识 1.触发器是构成时序逻辑电路的基本逻辑部件. 2.[1]它有两个稳定的状态:0状态和1状态: [2]在不同的输入情况下,它可以被置成0状态或1状态: [3]当输入 ...

- SR触发器和JK触发器

SR触发器(电平触发器) 基本RS触发器的逻辑方程为:Q(n+1)=一S+RQ(n); 约束方程:R+S=1; 根据上述两个式子得到它的四种输入与输出的关系: 1.当R端有效(0),S端无效时(1), ...

- D触发器

普通的电路,以及常规的逻辑门都有一个共性,那就是输出直接依赖于输入,当输入消失的时候,输入也跟着不存在了.触发器不同,当它触发的时候,输出会发生变化.但是,当输入撤销之后,输出依然能够维持. 这就是说 ...

- 2.计算机组成-数字逻辑电路 门电路与半加器 异或运算半加器 全加器组成 全加器结构 反馈电路 振荡器 存储 D T 触发器 循环移位 计数器 寄存器 传输门电路 译码器 晶体管 sram rom 微处理 计算机

现代计算机的各个部件到底是如何通过逻辑电路构成的呢 半加器 我们说过了门电路 看似简单的三种门电路却是组成了整个逻辑电路的根基 真值表--其实就是根据输入输出状态枚举罗列出来的所有可能 比如有一台 ...

- 继电器是如何成为CPU的(1)

继电器是如何成为CPU的(1) ——<穿越计算机的迷雾>整理和总结 究竟是如何设计的电路,具有计算和控制的智力? 这一点也不高深.本系列文章从初中学的最简单的电路图说起,看看能不能从最初的 ...

- 09A-独立按键消抖实验01——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习状态机的设计思想并以此为基础实现按键消抖 2.单bit异步信号同步化以及边沿检测 3.在激励文件中学会使用随机数发生函数$random 4.仿真模 ...

- 电路相关知识--读<<继电器是如何成为CPU的>>

电路相关知识–读<<继电器是如何成为CPU的>> */--> *///--> *///--> 电路相关知识–读<<继电器是如何成为CPU的> ...

- Android课程---寄存器与存储器的区别

存储器在CPU外,一般指硬盘,U盘等可以在切断电源后保存资料的设备,容量一般比较大,缺点是读写速度都很慢,普通的机械硬盘读写速度一般是50MB/S左右.内存和寄存器就是为了解决存储器读写速度慢而产生的 ...

随机推荐

- 【java】jvm查看当前虚拟机堆大小限制

#############################################################jinfo -flag MaxHeapSize 6461#linux: jav ...

- php中120个内置函数

php中实现事件模式 https://yq.aliyun.com/ziliao/162660 <?php class Event{ private $events = []; public fu ...

- Cognos第三方用户认证(CustomJavaProvider)

关于Cognos第三方用户认证(CustomJavaProvider)的demo网上的例子很多,当然最权威的你可以从Cognos安装的SDK中去探索,本文不详细的说明代码,主要说一下认证的处理过程,以 ...

- USACO humble

用set构造,优先队列和堆也能够 /* ID:kevin_s1 PROG:humble LANG:C++ */ #include <iostream> #include <cstdi ...

- [置顶] Android之服务器编程

这个教程主要是讲解服务器编程的,如果你的应用需要和服务器通信,那就必须了解服务器编程(当然,也许你不需要了解,因为你只开发客户端),Android应用和服务器的通信可以使用Http + JSON来通信 ...

- ASP.NET MVC+Bootstrap 实现短信验证

短信验证大家都已经非常熟悉了,基本上每天都在接触手机短信的验证码,比方某宝,某东购物.站点注冊,网上银行等等,都要验证我们的手机号码真实性.这样做有什么优点呢. 曾经咱们在做站点的时候.为了提高用户注 ...

- 启动mysql出现1067错误

0. 打开mysql\bin\my.ini,查找[mysqld],在[mysqld]下面添加一行文字,skip-grant-tables 即组成 [mysqld] skip-grant-tables[ ...

- MySQL 忘记密码:skip-grant-tables

1.首先确认服务器出于安全的状态,也就是没有人能够任意地连接MySQL数据库. 因为在重新设置MySQL的root密码的期间,MySQL数据库完全出于没有密码保护的 状态下,其他的用户也可以任意地登录 ...

- Eventually Consistent(最终一致性)(转)

应该说搞分布式系统必读的文章了,转过来,这是2008年12月Werner revise过的版本,先贴上内容简介:分布式系统的CAP理论 CAP理论(data consistency, system a ...

- 【转】SQL2008的sa账户被禁用,其他账户无法连接的解决方法

或者你还有其它的sysadmin权限的账号,你可以用此账号登录,重置SA密码. 但是在以下情况下,怎么办呢? 1. SA密码丢失或者SA账号被禁用. 2. 你进行了一些安全操作,把BuiltinAdm ...