SPI总线 通俗易懂讲解——(转载)

SPI总线

MOTOROLA公司的SPI总线的基本信号线为3根传输线,即SI、SO、SCK。传输的速率由时钟信号SCK决定,SI为数据输入、SO为数据输出。采用SPI总线的系统如图8-27所示,它包含了一个主片和多个从片,主片通过发出片选信号-CS来控制对哪个从片进行通信,当某个从片的-CS信号有效时,能通过SI接收指令、数据,并通过SO发回数据。而未被选中的从片的SO端处于高阻状态。

主片在访问某一从片时,必须使该从片的片选信号有效;主片在SCK信号的同步下,通过SI线发出指令、地址信息;如需将数据输出,则接着写指令,由SCK同步在SI线上发出数据;如需读回数据,则接着读指令,由主片发出SCK,从片根据SCK的节拍通过SO发回数据。

因而对具有SPI接口的从片器件来讲,SCK、SI是输入信号,SO是输出信号。SCK用于主片和从片通信的同步。SI用于将信息传输到器件,输入的信息包括指令、地址和数据,指令、地址和数据的变化在SCK的低电平期间进行,并由SCK信号的上升沿锁存。SO用于将信息从器件传出,传出的信息包括状态和数据,信息在SCK信号的下降沿移出。

Microchip公司的25XX系列的串行E2PROM采用了SPI总线,该系列器件的性能如表8-2所示。

|

型号

|

25XX040

|

25XX080

|

25XX160

|

25XX320

|

|

容量

|

4K

(512 X 8bit)

|

8K

(1024 X 8bit)

|

16K

(4096 X 8bit)

|

32K

(4096 X 8bit)

|

|

地址信号

|

A0~A8

|

A0~A9

|

A0~A10

|

A0~A11

|

以25XX320为例,该器件是4K字节的E2PROM,结构如图8-28所示,接口信号为SCK、SI和SO,此外还具有-CS、-WP、-HOLD信号线。其中-CS为器件选中信号,当此信号为低电平时器件被选中,高电平时器件处于等待状态。

与并行接口电路不同的是,在并行接口电路中对器件进行操作的控制信号,在串行接口电路中只能用指令实现,25XX320的操作指令有数据读指令、写操作的允许和禁止指令、写数据指令和状态寄存器的读写指令。在器件的内部有一个8位的指令寄存器,在SCK的上升沿,通过SI信号线,指令输入到上述寄存器并被执行。

表8-3 25系列串行存储器的指令

|

指令名称

|

指令格式

|

描述

|

|

READ

|

00000011

|

从选定的地址开始读存储器数据

|

|

WRITE

|

00000010

|

从选定的地址开始写存储器数据

|

|

WRDI

|

00000100

|

禁止写操作

|

|

WREN

|

00000110

|

允许写操作

|

|

RDSR

|

00000101

|

读状态寄存器

|

|

WRSR

|

00000001

|

写状态寄存器

|

器件的读操作时序如图8-29所示。当-CS信号有效时,在SCK信号的同步下,8位的读指令送入器件,接着送入16位地址(由于25XX320只使用地址信号A0~A11,地址的高4位无效)。在读指令和地址发出后,SCK继续发出时钟信号,此时存储在该地址的数据由SCK控制从SO引脚移出。在每个数据移出后,内部的地址指针自动加1,如继续对器件发送SCK信号,可读出下一个数据。当地址指针计到0FFFH之后,将回到0000H。读操作的结束由-CS信号变高实现。

25XX系列的串行EEPROM的写操作通过写允许及禁止指令控制,写操作必须在器件处于写允许状态时进行。

写允许及禁止指令均为8位的指令,指令的操作过程为:将-CS信号置为低电平,在SCK信号的作用下,通过SI引脚输入上述指令,在8位的指令送入器件之后,将-CS信号置为高电平,使器件锁存于写允许或写禁止状态。如在输入写允许指令后未将-CS信号置为高电平,则写允许状态未锁存,此时如直接进行写操作,数据将不能写入存储器。在上电、写禁止指令、写状态寄存器指令、写数据指令执行之后,器件的写允许状态将被复位,即处于写禁止状态。

写操作通常在写允许指令之后进行,其时序如图8-30所示。在写允许状态锁存后,将-CS变高;再将-CS变低,在SCK的同步下输入写操作指令并送入16位地址,紧接着发送需写入的数据,写入的数据一次最多可达32个,但必须保证在同一页内。一页数据的地址从XXXXXXXX

XXX0 0000 开始,到XXXX XXXX XXX1 1111结束,当内部的地址指针计数器达到XXXX

XXXX XXX11111后,继续发送时钟信号将使地址计数器回复到该页的第一个地址,即XXXX XXXX XXX0 0000H。

为了使数据有效写入,-CS信号只能在写入数据的最后一个字节的最低位写入后变高。如-CS信号在其他时间变高,将无法保证数据的完整写入。在写操作的过程中,能通过读状态指令将状态寄存器的内容读回,当写操作完成后,写允许锁存状态将被复位。

优缺点

SPI接口具有如下

优点:

1) 支持全双工操作;

2) 操作简单;

3) 数据传输速率较高。

缺点:

1) 需要占用主机较多的口线(每个从机都需要一根片选线);

2) 只支持单个主机。

3) 没有指定的流控制,没有应答机制确认是否接收到数据。

如果还是看不懂,那就再通俗点。

SPI总线协议介绍

一、技术性能

SPI接口是Motorola

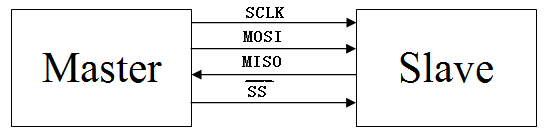

首先提出的全双工三线同步串行外围接口,采用主从模式(MasterSlave)架构;支持多slave模式应用,一般仅支持单Master。时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSBfirst);SPI接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。总线结构如下图所示。

二、接口定义

SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

(1)MOSI:主器件数据输出,从器件数据输入

(2)MISO:主器件数据输入,从器件数据输出

(3)SCLK:时钟信号,由主器件产生

(4)/SS:从器件使能信号,由主器件控制

三、内部结构

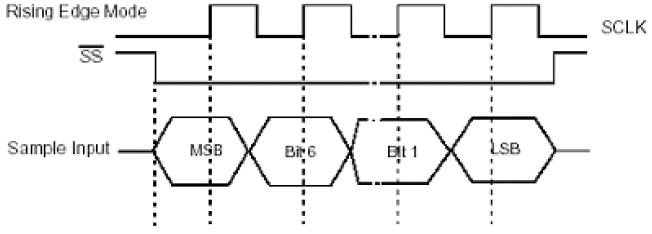

四、 时钟极性和时钟相位

在SPI操作中,最重要的两项设置就是时钟极性(CPOL或UCCKPL)和时钟相位(CPHA或UCCKPH)。时钟极性设置时钟空闲时的电平,时钟相位设置读取数据和发送数据的时钟沿。

主机和从机的发送数据是同时完成的,两者的接收数据也是同时完成的。所以为了保证主从机正确通信,应使得它们的SPI具有相同的时钟极性和时钟相位。

SPI接口时钟配置心得:在主设备这边配置SPI接口时钟的时候一定要弄清楚从设备的时钟要求,因为主设备这边的时钟极性和相位都是以从设备为基准的。因此在时钟极性的配置上一定要搞清楚从设备是在时钟的上升沿还是下降沿接收数据,是在时钟的下降沿还是上升沿输出数据。

五、传输时序

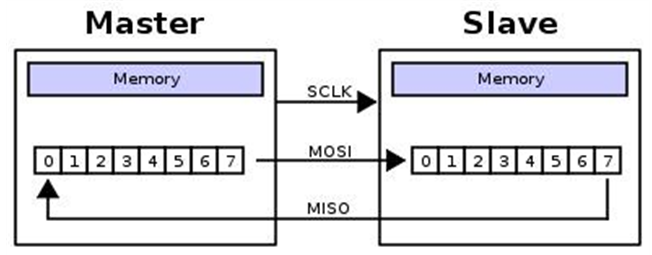

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。如下图所示,在SCLK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。

五、数据传输

在一个SPI时钟周期内,会完成如下操作:

1)主机通过MOSI线发送1位数据,从机通过该线读取这1位数据;

2)从机通过MISO线发送1位数据,主机通过该线读取这1位数据。

这是通过移位寄存器来实现的。如下图所示,主机和从机各有一个移位寄存器,且二者连接成环。随着时钟脉冲,数据按照从高位到低位的方式依次移出主机寄存器和从机寄存器,并且依次移入从机寄存器和主机寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

SPI总线 通俗易懂讲解——(转载)的更多相关文章

- 【转载】SPI总线和I2C总线的异同点

来源:https://blog.csdn.net/lishun1422840684/article/details/77776763 总结的简单.明了.适用! 一:SPI接口的全称是"Ser ...

- STM32学习笔记(八) SPI总线(操作外部flash)

1. SPI总线简介 SPI全称串行外设接口,是一种高速,全双工,同步的外设总线:它工作在主从方式,常规需要至少4根线才能够正常工作.SPI作为基本的外设接口,在FLASH,EPPROM和一些数字通讯 ...

- SPI总线通信电路设计

数据带宽=(总线频率×数据位宽)÷8 B表示带宽,F表示存储器时钟频率,D表示存储器数据总线位数,则带宽为: B(峰值带宽)=F(时钟频率MHz)×D(总线位数bit)/8 例如,PC-100的SDR ...

- Linux SPI总线和设备驱动架构之四:SPI数据传输的队列化

我们知道,SPI数据传输可以有两种方式:同步方式和异步方式.所谓同步方式是指数据传输的发起者必须等待本次传输的结束,期间不能做其它事情,用代码来解释就是,调用传输的函数后,直到数据传输完成,函数才会返 ...

- Linux SPI总线和设备驱动架构之三:SPI控制器驱动

通过第一篇文章,我们已经知道,整个SPI驱动架构可以分为协议驱动.通用接口层和控制器驱动三大部分.其中,控制器驱动负责最底层的数据收发工作,为了完成数据的收发工作,控制器驱动需要完成以下这些功能:1. ...

- Linux SPI总线和设备驱动架构之二:SPI通用接口层

通过上一篇文章的介绍,我们知道,SPI通用接口层用于把具体SPI设备的协议驱动和SPI控制器驱动联接在一起,通用接口层除了为协议驱动和控制器驱动提供一系列的标准接口API,同时还为这些接口API定义了 ...

- Linux SPI总线和设备驱动架构之一:系统概述

SPI是"Serial Peripheral Interface" 的缩写,是一种四线制的同步串行通信接口,用来连接微控制器.传感器.存储设备,SPI设备分为主设备和从设备两种,用 ...

- Linux SPI总线和设备驱动架构之一:系统概述【转】

转自:http://blog.csdn.net/droidphone/article/details/23367051/ 版权声明:本文为博主原创文章,未经博主允许不得转载. 目录(?)[-] 硬 ...

- SPI总线的原理与Verilog实现

转载地址:https://www.cnblogs.com/liujinggang/p/9609739.html 一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件 ...

随机推荐

- OAuth2 Token 一定要放在请求头中吗?

Token 一定要放在请求头中吗? 答案肯定是否定的,本文将从源码的角度来分享一下 spring security oauth2 的解析过程,及其扩展点的应用场景. Token 解析过程说明 当我们使 ...

- baystack(ret2one_gadget)

babystack 首先检查一下保护 全保护开启,我们IDA分析一下. main函数很简单,首先第一个read明显存在漏洞,如果不是以 \n 结尾会存在栈中地址的泄漏. payload = 'A'*0 ...

- 强大的工具(一):Capslock+ 2.x版本

2020.07.09 更新 作者更新了3.x版本,因此更新了3.x版本的博客,可以戳这里. 本篇文章介绍的是2.x版本. 1 Capslock+简介 Capslock+利用了键盘少用的Capslock ...

- Java文档注释全攻略

注释:注释起到对代码标注和解释的作用,如果你去看看JDK源码,会发现他们有许多的注释,而且注释是比代码还要多的,可见为代码添加注释是非常重要的,写好注释能让别人更加容易看懂你的代码,注释可以分为以下三 ...

- 一文读懂eBPF/XDP

XDP概述 XDP是Linux网络路径上内核集成的数据包处理器,具有安全.可编程.高性能的特点.当网卡驱动程序收到数据包时,该处理器执行BPF程序.XDP可以在数据包进入协议栈之前就进行处理,因此具有 ...

- 支持移远EC600S的SmartDtu平台,基于QuecPython

前言 本文的主要目的是说明青石SmartDtu到底做了哪些工作?我们在移远硬件平台EC600S上做了哪些支持?为什么说这套平台是硬件开发者的福音?我们的初衷是解放广大硬件开发者的双手,提供一套成熟的嵌 ...

- Windows中的共享文件和文件服务器

目录 共享文件的设置 默认共享 关闭默认共享 关闭共享服务 共享文件夹权限 文件服务器资源管理器的搭建 文件共享是指主动地在网络上共享自己的计算机文件.一般文件共享使用P2P模式,文件本身存在用户本人 ...

- Java线程的6种状态

6种状态分别是: NEW.RUNNABLE.TERMINATED.WAITING.TIMED_WAITING.BLOCKED NEW:线程创建完毕 RUNNABLE:线程运行中,又分为READY + ...

- 19.Quick QML-GroupBox自定义

GroupBox用来将子类的部件显示在其边框内部,并且一般默认左上有一个标题.GroupBox不提供自己的布局.所以需要我们自己通过ColumnLayout或者其他布局方式来进行布局.GroupBox ...

- GitBash管理代码

一.Git是什么? Git是目前世界上最先进的分布式版本控制系统. 1.Git和SVN的区别 SVN是集中式版本控制系统,版本库是集中放在中央服务器的,而干活的时候,用的都是自己的电脑,所以首先要从中 ...