FPGA设计思想(持续更新)

一、 流水线设计

将原本一个时钟周期完成的较大的组合逻辑通过合理的切割后分由多个时钟周期完成。该部分逻辑运行的时钟频率会有明显对的提升,提高系统的性能用面积换速度

一个流水线设计需要4个步骤完成一个数据的处理过程,那么从有数据输入的第一个时钟周期开始,直到第4个时钟周期处理完第一个数据,但在以后的每一个时钟周期都会有处理完成的数据输出,流水线设计在开始处理时需要一定的处理时间,但以后就会不断的输出数据,从而大大提高处理速度。(面积换速度)如果不采用流水线设计,那么处理一个数据就需要4个时钟周期,而采用流水线设计则能够提高将近4倍的处理速度

二、 跨时钟域处理

有三种方法

- 打两拍

- 异步双口RAM

- 格雷码转换

1. 打两拍方法

在进行uart串口通信的学习的过程中,遇到一个不理解的问题,在接收模块中,小梅哥采取的设计方式是接收进行一步同步化处理,那么为什么要进行同步化处理呢?串口通信的设计,接收的波特率一般是发送波特率的16倍,单bit传输,我的理解是,在发送波特率下的串口数据传输到接收波特率下时,这个过程是跨时钟的,对于小工程而言,不进行同步处理貌似没有什么关系,但是当工程对精度的要求比较强,外界干扰比较大的情况下,我们就必须进行同步化处理,下面我将学习第一种针对单bit的跨时钟域处理方法:打两拍。打两拍的方式,其实就是定义两级寄存器对数据进行延拍。

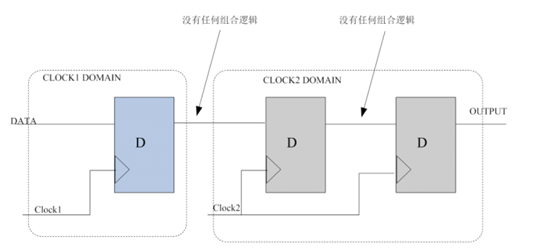

如上图,第一个时钟域将数据发送过来后,在第二个时钟域里用两个D触发器把接收数据进行延拍,中间没有任何组合逻辑。

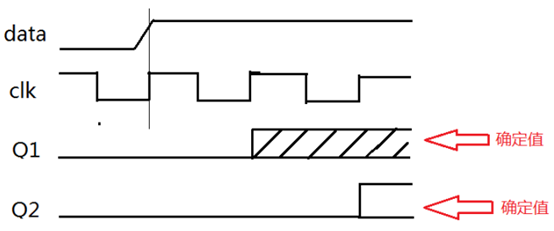

为什么是进行两级延拍呢?从上面的时序图可以看出,data是第一个时钟域的数据,Q1,Q2是第二个时钟域的触发器,在同一个clk时钟下,假设当clk的上升沿来临时,刚好采集到的数据是data的跳变沿(因为数据在有0变为1的时候,显然不是垂直上去的,它有一个建立时间,所以clk的上升沿采集到跳变沿的情况是完全有可能的),这样的话Q1接收的数据会处于亚稳态,但是我们至少可以保证,在clk下一个上升沿,data是稳定的,Q1基本上可以满足第二级寄存器的保持时间和建立时间的要求,出现亚稳态的几率会得到很大的改善。如果多加寄存器进行延拍,只是对Q2的数据进行了延拍,并没有什么意义,所以,我们选择进行两级延拍来处理单bit数据的跨时钟域处理。

三、 一个让我纠结了几个月问题

一个让我纠结了几个月问题

Altera的板子按键按下去时0.不按下去是1,

Altera的板子按键按下去时0.不按下去是1,

Altera的板子按键按下去时0.不按下去是1,

重要的纠结说三遍

Xilinx的板子按下去时1,不按是0

FPGA设计思想(持续更新)的更多相关文章

- FPGA设计思想与技巧(转载)

题记:这个笔记不是特权同学自己整理的,特权同学只是对这个笔记做了一下完善,也忘了是从那DOWNLOAD来的,首先对整理者表示感谢.这些知识点确实都很实用,这些设计思想或者也可以说是经验吧,是很值得每一 ...

- 09A-独立按键消抖实验01——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习状态机的设计思想并以此为基础实现按键消抖 2.单bit异步信号同步化以及边沿检测 3.在激励文件中学会使用随机数发生函数$random 4.仿真模 ...

- 【 js 基础 】【 源码学习 】源码设计 (持续更新)

学习源码,除了学习对一些方法的更加聪明的代码实现,同时也要学习源码的设计,把握整体的架构.(推荐对源码有一定熟悉了之后,再看这篇文章) 目录结构:第一部分:zepto 设计分析第二部分:undersc ...

- 08-FPGA状态机设计实例——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:1.学习状态机的相关概念 2.理解一段式.两段式以及三段式状态机的区别以及优缺点 实验平台:芯航线FPGA核心板 实验原理: 状态机全称是有限状态机(fin ...

- 02-FPGA设计流程介绍——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献 课程目标: 1.了解并学会FPGA开发设计的整体流程 2.设计一个二选一选择器并进行功能仿真.时序仿真以及板级验证 实验平台:芯航线FPGA开发板.杜邦线 实验内容: 良 ...

- 10-8位7段数码管驱动实验——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.实现FPGA驱动数码管动态显示: 2.使用In system sources and probes editor工具,输入需要显示在数码管上的的数据, ...

- 09B-独立按键消抖实验02——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习按键的设计 2.用模块化设计的方式实现每次按下按键0,4个LED显示状态以二进制加法格式加1,每次按下按键1,4个LED显示状态以二进制加法格式减 ...

- 07-阻塞赋值与非阻塞赋值原理分析——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:掌握阻塞赋值与非阻塞赋值的区别 实验平台:无 实验原理: 阻塞赋值,操作符为"=","阻塞"是指在进程语句( ...

- 05-IP核应用之计数器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯顿队长精心奉献 实验目的:了解FPGA的IP核相关知识并以计数器IP核为例学会基本IP使用的流程 实验平台:无 实验原理: IP核(Intellectual Propert ...

随机推荐

- [Java自学第二天]

Java封装性思想的初步理解 从项目需求的角度出发,建立各个模块化的类,各个模块暂时不需要具体的方法描述,只需要各个模块的理想到位. 以银行项目为例 初步设想需要三个模块:银行(Bank类).客户(C ...

- bootstrap loadStep流程节点动态显示

<!DOCTYPE html PUBLIC "-//W3C//DTD HTML 4.01 Transitional//EN" "http://www.w3.org/ ...

- 03(3) 基于GMM-HMM的SR基础

1.GMM-HMM的训练 1)训练GSM-HMM (1)确定HMM拓扑结构 (2)初始化HMM模型参数 (3)在所有的utterances中计算所需的统计量 (4)使用公式更新模型参数 (5)不收敛, ...

- EMMC与RAND的区别

作者:Younger Liu, 本作品采用知识共享署名-非商业性使用-相同方式共享 3.0 未本地化版本许可协议进行许可. EMMC与RAND的区别 说到两者的区别,必须从flash的发展历程说起,因 ...

- 全易通人事考勤工资验厂管理系统软件创建连接SQL2000数据库的操作方法和说明

全易通人事考勤工资验厂管理系统软件创建连接SQL2000数据库的操作方法和说明.全易通人事考勤工资验厂管理系统软件,有2种数据库,一个是ACCESS,另一个是SQL.不过由于ACCESS数据库比较小, ...

- day_1 练习2

#!/usr/bin/env python# -*- coding:utf-8 -*-'''b. 功能要求: v = 2000 要求用户输入总资产,例如:2000 显示商品列表,让用户根据序号选择商品 ...

- zabbix_server表面启动成功,但是没有进程

[root@iZ25m1box8cZ zabbix]# /etc/init.d/zabbix_server start Starting zabbix_server (via systemctl): ...

- Python变量运算字符串等

一,作用域 操作 name = 'liuyueming' if 1==1:... print name... liuyueming 两次回车执行 修改代码 >>> if 1==1:. ...

- java之反射

初学反射,也是第二次写博客了把,就简单记录一下. Reflection(反射)是被视为动态语言的关键,反射机制允许程序在执行期借助于Reflection API取得任何类的内部信息,并能直接操作任意对 ...

- [ios]quartz2d画板功功能实现核心代码

//触摸开始 -(void)touchesBegan:(NSSet<UITouch *> *)touches withEvent:(UIEvent *)event{ // 1,获取对 ...