【黑金原创教程】【TimeQuest】【第三章】TimeQuest 扫盲文

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢!

黑金动力社区2013年原创教程连载计划:

http://www.cnblogs.com/alinx/p/3362790.html

《FPGA那些事儿--TimeQuest 静态时序分析》REV3.0 PDF下载地址:

http://www.heijin.org/forum.php?mod=viewthread&tid=22445&extra=page%3D1

第三章:TimeQuest 扫盲文

3.1 余量的概念

3.2 延迟因数:内部延迟因数

3.3 延迟因数:外部延迟因数

3.4 第一层与第二层时间要求

3.5 山寨TimeQuest模型

3.6 约束命令和约束行为

总结

第三章:TimeQuest扫盲文

3.1余量的概念

笔者常常在思考,虽说TimeQuest是一个分析物理时序是否合格的数学工具,但是TimeQuest真正意义上是在针对什么?这是一个很有趣的问题 ,而TimeQuest有一个关键字,就是“约束”英文是“Constraint”。

“约束”如果用傻瓜的话来解释,就是告诉TimeQuest“应该干甚么或者注意甚么”,然而其中的“甚么”又是“甚么”?这绝不是在鸡蛋里挑骨头的问题。如果不把“这个什么”搞清楚,我们就不能完全理解 TimeQuest到底为了什么目的而问世?根据笔者的理解“这个什么”就是延迟因数,亦即“TimeQuest是一个针对各种延迟因数作出约束的静态时序分析工具”。

有一个问题笔者一直无法释怀,当Modelsim仿真HDL模块之际,如果考虑延迟信息,时序就会出现物理延迟,换之在Modelsim界面上出现的波形,事实上也是静态时序的一种,不过Modelsim只能看个大概而已,而不能做出实际的分析。所以笔者一直认为,Modelsim既然要仿真就仿真理想时序而不是物理时序。所以说,物理时序分析的工作我们就交给TimeQuest去干。

理想时序是不存在延迟因数的时序,而物理时序是充满延迟因数的时序;理想时序是HDL产生的行为,而物理时序硬模型产生的行为。理想时序可以用 Modelsim来仿真,而物理时序可以用TimeQuest来分析。

好了!终于搓到重点了,笔者曾讲过:“Verilog HDL是关心理想时序,而TimeQuest是关心物理时序”。《整合篇》未完成之前,笔者认为道:“理想时序和物理时序是两个世界的家伙”。换之,《整合篇》完成之后,笔者认为道:“理想时序和物理时序可以用黏糊概念联系起来”。

让我们先来聊聊黏糊概念吧:

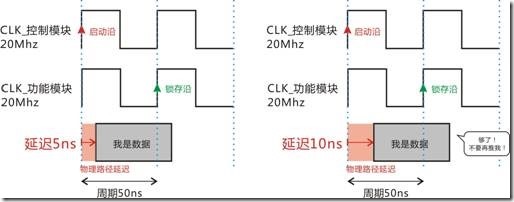

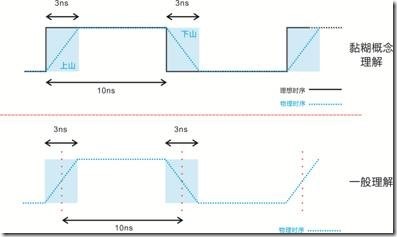

图3.1.1 物理时序的推向概念。

图3.1.1所示是物理时序的推向概念,数据被5ns/10ns延迟向右推挤以后就失去对齐性,而推向的距离就是延迟值。

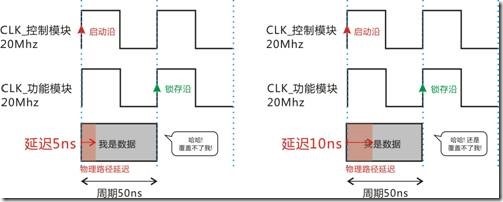

图3.1.2 理想时序的覆盖概念。

图3.1.2所示是理想时序的覆盖概念,数据和时间沿之间没有失去对齐性,然而延迟实数会根据数值覆盖数据。黏糊概念有着一个逻辑,假设同学带足1万块出远门,只要1万块消费不到零值,这趟远门是开心的。这种比喻就好比一块有10ns周期的数据,只要10ns的容量不完全被延迟覆盖,这块数据就不会失去有效性。

黏糊概念和保险余量,建立余量还有保持余量有许多相似的地方,不过黏糊概念是用图形表达,而保险余量,建立余量还有保持余量是用数值来表达。笔者曾一度认为,TimeQuest的延迟取值是按实际的物理延迟,不过事实恰恰相反,TimeQuest对延迟取值是夸张的表现,这话何解呢?

假设有一条路径的物理延迟是10ns,如果是worst-case 网表TimeQuest就会报18ns,如果是best-case 网表TimeQuest就会报12ns。很明显,18ns还有12ns的报值比起实际的10ns多出8ns还有2ns,其中这8ns和2ns的差别就是保险余量。

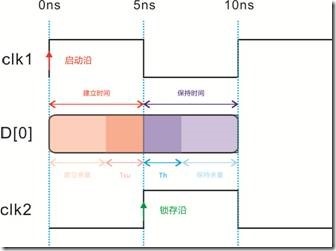

图3.1.3 一块数据的有效性。

假设一块数据有10ns的周期,而锁存沿正好在5ns的位置锁存数据。根据理论而言,一块数据的有效性主要分为建立时间与保持时间。Tsu是寄存器在锁存数据之前需要的最小建立时间(热生时间),换之Th是寄存器在锁存数据之后需要的最小保持时间(确保时间)。然而建立时间减掉Tsu就是建立余量,而保持时间减掉Th就是保持余量。(如图3.1.3所示)。

建立余量是用来评估数据有效的建立时间,只要建立余量一天不被吃光,这块数据的建立是有效的。保持余量是用来评估数据有效的保持时间,只要保持余量一天不被吃光,这块数据的保持是有效的。

所以说,保险余量,建立余量还有保持余量越多,设计就越安全。这感觉就好比读者出远门有1万块的金钱余量。不过保险余量与建立余量还有保持余量是不同层次的概念余量。保险余量的感觉就好比读者向妈妈要钱买玩具。

妈妈问:“玩具要多少钱?”,假设玩具的成本是10元,不过根据不同的卖家价钱也有可能是18元或者20元 ... 于是,贪心的读者便狮子夸大口说:“玩具要50元”。只要读者向妈妈要钱越多,妈妈对读者的信任就会越来越少。换一个角度来思考的话,10元的成本就是实际的延迟,不同卖家的价钱就是根据环境因数造成的预测延迟,而读者开口的50元就是保险余量,至于妈妈对读者的信任就是性能限制。

50元就像worst-case网表(硬模型),30元就好比best-case 网表(硬模型)。有50元虽然买玩具更安全,但是妈妈越不信任读者,换之30元比起50元虽然损失一些安全性,但是妈妈更加信任读者。以此类推,假设玩具店A售价是32元,只有30元保险余量而已的best-case当然买不起的玩具店A的玩具。换之50源的worst-case却买得起。

再假设,玩具店B售价是15元,30元的best-case网表或者50元的worst-case网表必定买得起玩具店B的玩具。不过读者千万不要太贪心骗妈妈成本只有10元的玩具售价是100元啊,不然的话妈妈会永远对你失去信心。

网表质量中也有一个关键的概念,亦即性能限制 ... 假设路径A有10ns的延迟,而这个10ns的延迟又叫成本延迟,是实际的路径延迟取值。不过TimeQuest声明的网表往往都会高出成本延迟,如worts-case网表会使路径A取值为50ns,又或者best-case网表会使路径A取值为20ns。

TimeQuest有一个评估值,称为Fmax。Fmax是用来评估节点的最高频率。每当网表质量越低,节点的延迟取值就会越高, Fmax也随之会越低。如果Fmax越低fpga就不能发挥实际的速度和性能,因此我们可以这样说:网表质量越低,保险余量越大,Fmax评估越低,性能限制也越高。

3.2延迟因数:内部延迟因数

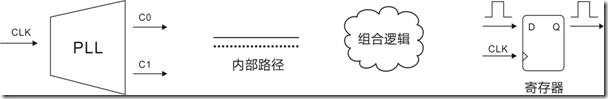

图3.2.1 延迟因数。

延迟因数一般上可以分为两种,亦即内部延迟因数和外部延迟因数,如图3.2.1所示。

图3.2.2 内部延迟因素。

不过TimeQuest比较在意的内部延迟因数有图3.2.2所示,其中是pll,内部路径,组合逻辑还有寄存器特性。不管哪一种内部延迟因数,它们都有一个共同点,亦即TimeQuest会自动知晓它们的延迟取值。此外,根据不同质量网表,延迟取值也会有所不同worst-case 网表的延迟取值比best-case网表的延迟取值当然多出不少。

PLL事实上就是一种不开又不关的内部延迟因数,虽然TimeQuest会认识它,但是TimeQuest不会完全公开它;内部路径可说是最普遍的内部延迟因数,其中data path还有clock path都会出现它的身影;组合逻辑可说是内部延迟因数中最臃肿的家伙;寄存器特性算是不怎么起眼的内部延迟因数。

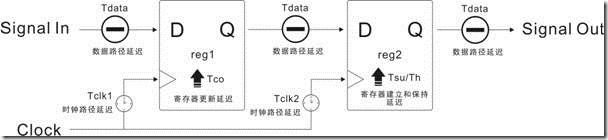

图3.2.3 某对节点的内部延迟。

图3.2.3是某对节点的物理情形,其中充满许多内部延迟因数,Tdata可以是路径延迟或者组合逻辑;Tclk1与Tclk2就是路径延迟;而Tco/Tsu/Th就是内部延迟因数的寄存性特性。不过很遗憾的是图3.2.3没有pll的声影,没关系 ... 笔者会另行举例的。

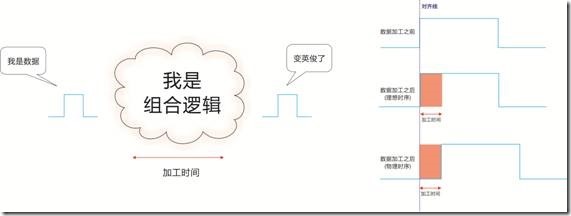

图3.2.4 组合逻辑加工数据信号。

要明白 pll 之前,读者必须组合罗加工数据的基本概念,如图3.2.4所示,有一块数据经过组合逻辑以后就变英俊了,而数据便英俊的过程如右图所示。在理想时序下,加工时间以及组合逻辑的延迟会将部分数据覆盖掉,换之 ... 物理时序的情况下,加工时间会向右推挤数据。

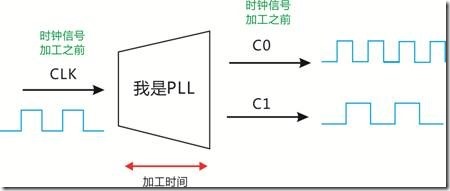

图3.2.5 PLL加工时钟信号。

pll与一般的组合逻辑区别的地方就在于,组合逻辑加工数据信号,而pll则加工时钟信号。如图3.2.5所示,clk是加工之前的时钟信号,而c0与c1是加工之后的时钟信号,其中pll也有加工时间亦即pll延迟。

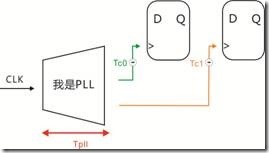

图3.2.6 PLL给两个寄存器各别提供 C0 和 C1的时钟信号。

我们假设C0和C1都有供源对象,其中时钟信号C0和C1经过的路径多少也有延迟,其中又名为Tc0和Tc1,如图3.2.6所示。

图3.2.7 PLL的理想时序和物理时序。

仿真过 pll的同学当然知道,如果仿真没有加入延迟信息,pll就会产生左图的理想时序 ... 换之,如果仿真加入延迟因数就会产生右图的物理时序。其中Tpll作为时钟信号c0和c1的起跑线。TimeQuest在分析pll的时候会特别关心Tc0和Tc1时钟路径。让笔者说说一些题外话,左图的pll会产生的理想时序,期间pll和其他组合逻辑一样,亦即触发即时事件。

求得建立余量的公式是 :

保持余量 = 数据锁存时间 - 数据抵达时间

Setup Slack = Data Required Time - Data Arrival Time

数据抵达时间 Data Arrival Time = 启动沿 + Tclk1 + Tco + Tdata

数据获取时间 Data Required Time = 锁存沿 + Tclk2 - Tsu

= 理想建立关系值 + Tclk2 - Tsu

求得保持余量的公式是:(用头脑的话)

保持余量 = 数据保持时间 - 数据获取时间

Hold Slack = Data Hold Time - Data Required TIme

数据保持时间 Data Hold Time = 启动沿 + Tclk1 + Tco + Tdata + 数据周期时间

数据获取时间 Data Required Time = 锁存沿 + Tclk2 + Th

求得保持余量的公式是:(用屁股的话)

保持余量 = 数据抵达时间 - 数据获取时间

Hold Slack = Data Arrival Time - Data Required Time

数据抵达时间 Data Arrival Time = 启动沿 + Tclk1 + Tco + Tdata

数据获取时间 Data Required Time = 锁存沿 + Tclk2 + Th

= 理想保持关系值 + Tclk2 + Th

上面有三段公式,笔者想必读者不会觉得陌生吧?其中在公式出现的 Tco/Th/Tsu就是内部的寄存器特性。嘛 ... 有关内部延迟因数,寄存器特性的作用极微甚小,不足影响保持余量和建立余量,而寄存器特性在物理时序中它们都会完全忽略掉。

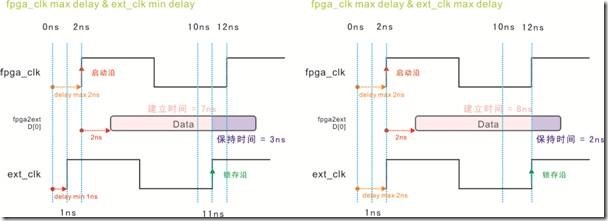

3.3延迟因数:外部延迟因数

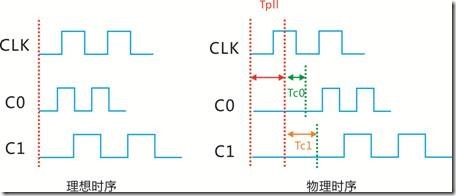

图3.3.1 各种外部延迟因数。

图3.3.1是各外部延迟因数,其中引脚的电容性会引起tRise与tFall延迟,而外部路径是最妙的延迟因数,最后还有外部IC的寄存器特性。

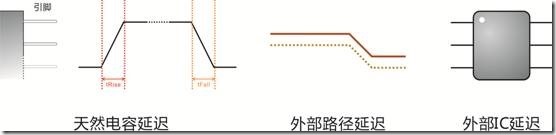

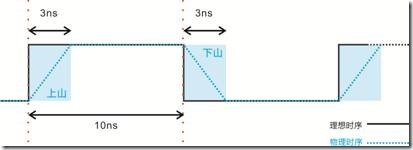

图3.3.2 理想时序与物理时序。

器件引脚存有电容性是小孩都知道的常识,而引脚的电容性必定会产生tRise与tFall延迟,不过不是每本一本器件手册都会举例tRise与tFall的具体时间。在器件书册没有举例的情况下,我们还必须手动将电容性转换tRise还有tFall的具体时间。

如图3.3.2所示,在理想时序下是不存在什么 tRise或者tFall,反之物理时序就会出现tRise与tFall延迟。根据黏糊概念而言,tRise和tFall好比寄生虫,寄生在数据的身体里边。同学们很可能觉得笔者这样形容 tRise 和 tFall有点不正确 ... 不相信笔者也不打紧,让我们再看其他例子。

图3.3.3 黏糊概念的理解和一般理解的比较。

图3.3.3的上图是黏糊概念如何理解 tRise与tFall,而下图是一般概念如何理解tRise与tFall。事实上,上图和下图有着等价的关系,不过在理解和编辑上 ... 黏糊概念比起一般理解有更多优势。

tRise与tFall,原本不是TimeQuest的正规问题,这不过是笔者犯贱而已,才会兴致勃勃去研究它。事实上,只要用黏糊概念再加上相关的约束命令,tRise与tFall也可以约束的。

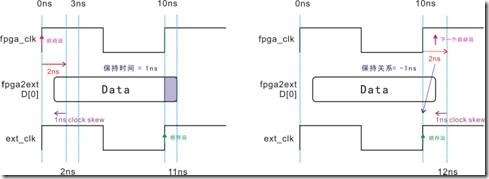

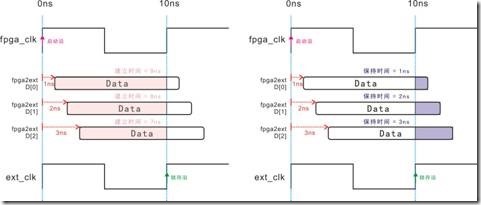

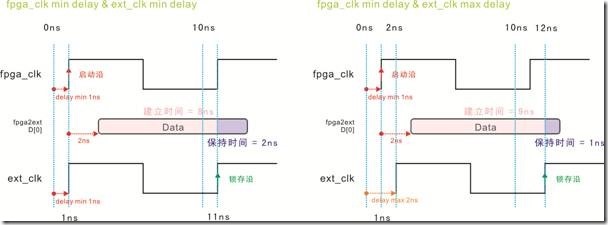

图3.3.4 单位宽数据的例子。

图3.3.5 多位宽宽数据的例子。

外部路径算是学习TimeQuest最关键的部分。TimeQuest在认识外部路径的时候,会区分数据路径和时钟路劲。TimeQuest在认识数据路径的时候,又会根据数据的位宽进一步区分认识,如图3.3.4和图3.3.5所示。为什么TimeQuest 要那么麻烦进一步区分数据的单位位宽和多位宽?事实上这是与约束命令的行为有关。

图3.3.6 时间抖动产生不同可能性的时序。

至于外部时钟路径更妙了 ... 根据理论而言,外部的时钟源比起内部的时钟源更容易产生时间抖动,而时间抖动会给外部时钟路径产生不同延迟,也因此产生多可能性的时序图,如图3.3.6所示。笔者在研究时钟抖动的时候吃过不少苦头,而TimeQuest也用了一大半的约束命令针对外部时钟路径。从这观点来看,TimeQuest有多重视外部时钟路径。

此外,外部路径还有一个非常重要的参数,亦即介电参数 ... 不同原材料的PCB版都有不同程度的介电参数。介电参数就像是高速公路的原材料,如黑油(沥青路),沙地,石砖等。介电参数越高就表示该高速公路的表面越不平坦,信号在上面行走时,就会产生越多的延迟。

而如何将路径的长度乘上介电参数再换算延迟时间,笔者就不打算介绍了 ... 换之有现成的转换软件可以为我们偷懒,呵呵呵!

assign Q = rQ;

上面一段代码是HDL经典的描述行为,亦即用寄存器rQ驱动Q输出口。如果以此类推,外部IC的输出口,或者输入口一定也是由寄存器驱动。换言之,外部IC也定存在寄存器特性,不是吗?IC的寄存器特性可以在相关的器件手册上查到。

3.4第一层与第二层时间要求

第一层时间要求和第二层时间是整合时序衍下的概念,这概念的产生主要是为HDL可以“照顾”物理时序,单用文字来描述会非常抽象 ... 就让笔者用例子来讲解吧。

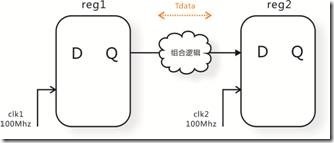

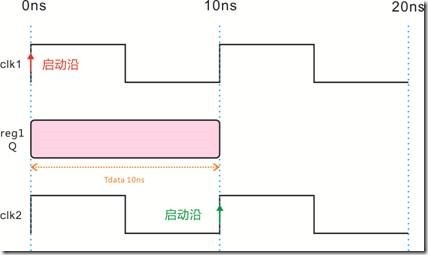

图3.4.1 两个寄存器夹着一个组合逻辑。

图3.4.1是一个典型的TimeQuest模型,亦即两个寄存器夹着一个组合逻辑 ... reg1和reg2同样使用的100Mhz的时钟信号,而它们之间夹着的组合逻辑,有Tdata别名的延迟压力,我们也可以看成数据加工时间。首先我们必须知道,对于100Mhz的时钟信号而言,1个时钟的周期时间是10ns,如果HDL设计基于这个10ns周期的时钟信号,那么这个10ns是HDL最小的时间。此外我们也必须知道,HDL只有能力产生理想时序。

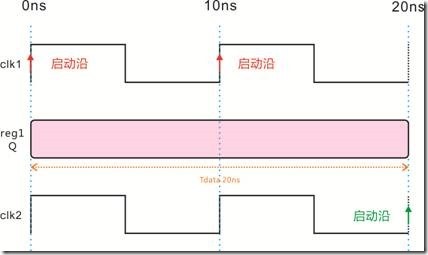

图3.4.2 HDL可以照顾又可以涉及的第一层时间要求。

举个例子,假设读者想要生产面包,生成一块面包需要的最小时间也称为空时间或者加工时间;换之,制作面包的原材料又称供源。这个比喻好似图3.4.2的情况,如图3.4.2所示 ... 我们先假设Tdata 有10ns延迟压力,亦即浅红色的矩形。而启动沿的数量就是空时钟,在这里有1个启动沿,亦即给足1个空时钟或者10ns的加工时间。

然而reg1-Q的数据长度就是供源,亦即空白矩形,换言之reg1-Q给足1个时钟,或者10ns的供源。好了,重点来了 ... 上述说过HDL的最小时间是10ns,而Tdata的延迟压力恰恰好是10ns。简单说,reg1只要驱动组合逻辑1个时钟,期间什么也不做,而HDL可以这样表示:

case(i)

0: //r1Q是驱动组合逻辑的寄存器

begin r1Q <= 1'b1; i <= i + 1'b1; end

...

endcase

.csharpcode, .csharpcode pre

{

font-size: small;

color: black;

font-family: consolas, "Courier New", courier, monospace;

background-color: #ffffff;

/*white-space: pre;*/

}

.csharpcode pre { margin: 0em; }

.csharpcode .rem { color: #008000; }

.csharpcode .kwrd { color: #0000ff; }

.csharpcode .str { color: #006080; }

.csharpcode .op { color: #0000c0; }

.csharpcode .preproc { color: #cc6633; }

.csharpcode .asp { background-color: #ffff00; }

.csharpcode .html { color: #800000; }

.csharpcode .attr { color: #ff0000; }

.csharpcode .alt

{

background-color: #f4f4f4;

width: 100%;

margin: 0em;

}

.csharpcode .lnum { color: #606060; }

为了稳定驱动,r1Q可以多供源一个时钟:

case(i)

0,1: // 第一层时间要求多供源一个时钟

begin r1Q <= 1'b1; i <= i + 1'b1; end

...

endcase

.csharpcode, .csharpcode pre

{

font-size: small;

color: black;

font-family: consolas, "Courier New", courier, monospace;

background-color: #ffffff;

/*white-space: pre;*/

}

.csharpcode pre { margin: 0em; }

.csharpcode .rem { color: #008000; }

.csharpcode .kwrd { color: #0000ff; }

.csharpcode .str { color: #006080; }

.csharpcode .op { color: #0000c0; }

.csharpcode .preproc { color: #cc6633; }

.csharpcode .asp { background-color: #ffff00; }

.csharpcode .html { color: #800000; }

.csharpcode .attr { color: #ff0000; }

.csharpcode .alt

{

background-color: #f4f4f4;

width: 100%;

margin: 0em;

}

.csharpcode .lnum { color: #606060; }

上述代码中的步骤0, r1Q赋值1'b1一个时钟。在此我们可以这样说,HDL不仅可以照顾到Tdata的10ns时间要求,也可以设计到它。因此Tdata可以断定为第一层时间要求。

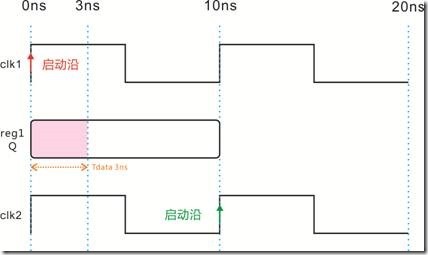

图3.4.3 HDL可以照顾不过不可以涉及到的第二层时间要求。

我们再假设tData有3ns的延迟压力,根据黏糊概念这个3ns的延迟压力会覆盖掉数据的一部分,如图3.4.3所示 ... 启动沿的数量只有一个,亦即给足1个空时钟或者10ns的加工时间。此外,空白矩形有10ns的长度。基本上,HDL对3ns的物理延迟实在无能为力,余下HDL能尽力的事情就是确保给足1个空时钟,此外reg-Q也必须给足供源1个时钟,HDL可以这样表示:

case(i)

0: //r1Q是驱动组合逻辑的寄存器

begin r1Q <= 1'b1; i <= i + 1'b1; end

...

endcase

.csharpcode, .csharpcode pre

{

font-size: small;

color: black;

font-family: consolas, "Courier New", courier, monospace;

background-color: #ffffff;

/*white-space: pre;*/

}

.csharpcode pre { margin: 0em; }

.csharpcode .rem { color: #008000; }

.csharpcode .kwrd { color: #0000ff; }

.csharpcode .str { color: #006080; }

.csharpcode .op { color: #0000c0; }

.csharpcode .preproc { color: #cc6633; }

.csharpcode .asp { background-color: #ffff00; }

.csharpcode .html { color: #800000; }

.csharpcode .attr { color: #ff0000; }

.csharpcode .alt

{

background-color: #f4f4f4;

width: 100%;

margin: 0em;

}

.csharpcode .lnum { color: #606060; }

上述代码中的步骤0给足1个空时钟至于,r1Q赋值1'b1也长达一个时钟。因此我们可以这样说,HDL只可以照顾到 Tdata的3ns时间要求,可是却涉及不了,因此Tdata可以断定为第二层时间。

case(i)

0,1: // 第二层时间要求多供源一个时钟

begin r1Q <= 1'b1; i <= i + 1'b1; end

...

endcase

.csharpcode, .csharpcode pre

{

font-size: small;

color: black;

font-family: consolas, "Courier New", courier, monospace;

background-color: #ffffff;

/*white-space: pre;*/

}

.csharpcode pre { margin: 0em; }

.csharpcode .rem { color: #008000; }

.csharpcode .kwrd { color: #0000ff; }

.csharpcode .str { color: #006080; }

.csharpcode .op { color: #0000c0; }

.csharpcode .preproc { color: #cc6633; }

.csharpcode .asp { background-color: #ffff00; }

.csharpcode .html { color: #800000; }

.csharpcode .attr { color: #ff0000; }

.csharpcode .alt

{

background-color: #f4f4f4;

width: 100%;

margin: 0em;

}

.csharpcode .lnum { color: #606060; }

虽然rQ1多供源一个时钟可以解决第二层时间要求,如上所示。话虽那么说 ,一般拥有第二层要求的时序都是条件都非常苛刻,随便多供源一个时间可能会使延迟传输,又或者造就信号不同步。除此之外,第二层时间要求往往又多又小,如果为所有第二层时间多供源一个时钟,即不是要耗费打量宝贵的时间与资源呢?

如果HDL遇到第二层时间,它该怎么办?很简单,HDL只要尽量产生理想时序即可,用黏糊概念来说,只要延迟压力不要覆盖全部数据就行了。余下的工作就交给TimeQuest等静态时序分析工具分析看看,第二层时间要求到底会不会破坏数据的有效性,又或者检测供源是否足够?

如何明白第一层或者第二层时间要求的关键地方 ... 读者必需从HDL的角度去思考各种时间要求。假设我们要用HDL产生1Mhz的SPI时序,这时候如果fpga有100Mhz的时钟频率 .... 100Mhz的频率使HDL有10ns最小时间,换之要用10ns产生1Mhz的SPI时序是非常有余,许多小地方都可以涉及到。

当HDL完成软模型的设计,而且软模型也总和成为硬模型,想必硬模型的内部一定有许多10ns最小时间无法涉及时间要求,这时候我们就要使用TimeQuest等工具去分析他们。除了硬模型里边的时间要求以外,一些高速器件的驱动如 SDRAM,第二层时间要求也会出现外边。

图3.4.4 HDL可以照顾又可以涉及的第一层时间要求(多时钟)。

除了单时钟的第一层与第二层时间要求以外,同样也有多时钟的第一层与第二层时间要求。如图3.4.4所示,有2个启动沿亦即给足2个空时钟,reg1-Q的空白矩形又20ns的长度,亦即供源有20ns,然而2个空时钟和20ns的供源不仅照顾到20ns的Tdata,而且又涉及其中,因此我们可以断定20ns延迟的Tdata视为第一层时间。

HDL可以这样表示:

case(i)

0,1,2: // 第一层时间要求多供源一个时钟

begin r1Q <= 1'b1; i <= i + 1'b1; end

...

endcase

.csharpcode, .csharpcode pre

{

font-size: small;

color: black;

font-family: consolas, "Courier New", courier, monospace;

background-color: #ffffff;

/*white-space: pre;*/

}

.csharpcode pre { margin: 0em; }

.csharpcode .rem { color: #008000; }

.csharpcode .kwrd { color: #0000ff; }

.csharpcode .str { color: #006080; }

.csharpcode .op { color: #0000c0; }

.csharpcode .preproc { color: #cc6633; }

.csharpcode .asp { background-color: #ffff00; }

.csharpcode .html { color: #800000; }

.csharpcode .attr { color: #ff0000; }

.csharpcode .alt

{

background-color: #f4f4f4;

width: 100%;

margin: 0em;

}

.csharpcode .lnum { color: #606060; }

图3.4.5 HDL可以照顾不过不可以涉及的第二层时间要求(多时钟)。

图3.4.5是HDL可以照顾但是却涉及不了的第二层时间要求,其中有2个启动沿亦即有2个空时钟,而reg1-Q也有20ns的长度,不过Tdata却只覆盖15ns的部分而已。这种情况下我们可以说,2个空时钟和20ns的供源虽然已经给足,但是却涉及不了,因此断定15ns延迟的Tdata为第二层时间要求。

HDL可以这样表示:

case(i)

0,1: // 第二层时间要求

begin r1Q <= 1'b1; i <= i + 1'b1; end

...

endcase

.csharpcode, .csharpcode pre

{

font-size: small;

color: black;

font-family: consolas, "Courier New", courier, monospace;

background-color: #ffffff;

/*white-space: pre;*/

}

.csharpcode pre { margin: 0em; }

.csharpcode .rem { color: #008000; }

.csharpcode .kwrd { color: #0000ff; }

.csharpcode .str { color: #006080; }

.csharpcode .op { color: #0000c0; }

.csharpcode .preproc { color: #cc6633; }

.csharpcode .asp { background-color: #ffff00; }

.csharpcode .html { color: #800000; }

.csharpcode .attr { color: #ff0000; }

.csharpcode .alt

{

background-color: #f4f4f4;

width: 100%;

margin: 0em;

}

.csharpcode .lnum { color: #606060; }

如果多时钟的第一层或者第二层时间要求发生在时序产生或者驱动器件的话,我们可以使用黏糊概念将就而过。相反的,如果多时钟的第二层时间要求发生在硬模型里边的话,故事的说法就不一样了...

我们知道TimeQuest是一个笨蛋,在默认的情况下TimeQuest模型都是以单时钟作为基准去分析节点是否合格。有时我们会遇见如图3.4.5的情形,这时候我们就要使用相关的约束命令告诉TimeQuest“某对节点是用N个时钟工作”。如此一来,TimeQuest就会知道某对节点是使用N个时间工作。

不过,到底是什么情形会使第二层时间要求发生在硬模型的里面?答案很简单,那就是组合逻辑的应用。《整合篇》曾讨论过即时建模,那是建立大组合逻辑的方法,大组合逻辑所需的加工时间往往超过HDL本身的最小时间。

最后我们可以这样总结:

HDL涉及不了的时间要求交给 TimeQuest 去做,不过在此之前HDL 必须尽量做好“理想时序”的部分,最后“物理时序”的部分则交给 TimeQuest去分析和涉及。

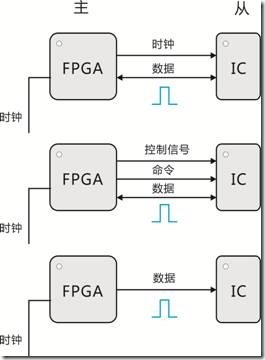

3.5山寨TimeQuest模型

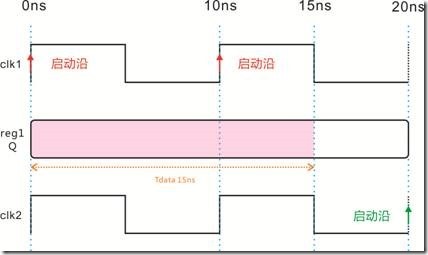

在第一章笔者曾说过,TimeQuest模型的基本结构是由一对节点组成,不过节点是没有个性的东西,如果节点放在fpga内部,它就会成为寄存器,又称TimeQuest内部模型。换之如果节点放在fpga外部,它就成为fpga和外部器件(ic),又称TimeQuest外部模型。

图3.5.1 TimeQuest模型(内部模型),山寨TimeQuest模型(外部模型)。

所谓山寨TimeQuest模型是指,TimeQuest模型是否可以在外部成立。换句话说,外部fpga和外部器件又如何成立一对寄存器,而寄存器之间的延迟因数又是什么?如图3.5.1所示,默认的TimeQuest又指内部模型,而山寨的TimeQuest模型又指外部模型。内部模型的节点变成源寄存器和目的寄存器,而外部模型的节点变成fpga和ic。

笔者曾思考过,TimeQuest模型虽有内外之分,可是却有相同概念?原因很简单,TimeQuest的设计者和笔者一样都是懒人 ... 呵呵!开玩笑而已。他们这样做的目的是“同用思路”,换言之:一套可以应用在内部模型的分析方法,同样也可以应用在外部模型。

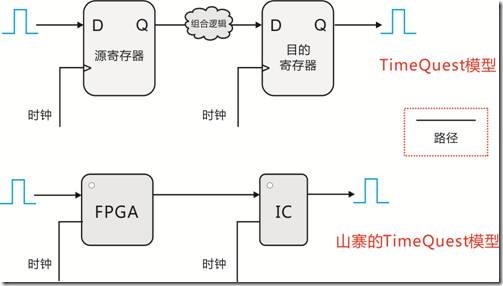

图3.5.2 无法山寨TimeQuest模型的情况。

不过外部模型不一定是山寨成功,如图3.5.2所示,如果主机fpga给从机ic驱动时钟信号和数据。结果而言TimeQuest模型一定会山寨失败,这种情形有spi,iic,ps/2时序等。此外,没有时钟信号,而有控制信号或者控制命令之间的数据传输也会让TimeQuest模型上寨失败,这种情形有静态ram,传统lcd驱动等。还有一种情形就是单纯的数据传输,也会无法山寨成功TimeQuest模型,这种情形有uart和vga时序等。

读者可能会问:“如果外部模型山寨失败的话,那么外部延迟因数又如何约束呢?”这是一个多疑的问题,TimeQuest只是一匹只懂在模型里打滚的笨蛋而已,如果模型无法成立TimeQuest就会无用武之地。此时,我们也只能做好内部模型的分析即可 ... 外边就交个人品和运气。

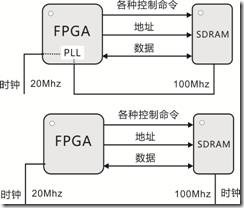

图3.5.3 FPGA和SDRAM的外部模型。

外部模型可以成功山寨的经典例子就是sdram,如图3.5.3所示。fpga与sdram之所以可以成功山寨TimeQuest模型是因为fpga与sdram都独自的时钟。上图的20Mhz时钟信号经过fpga内部的pll以后,成为100Mhz再供源sdram ... 这种情形的 sdram时钟不是图3.5.2所示的驱动时钟,而是供源时钟。

上图和下图有着等价的关系。在实际的环境里,为了运动sdram而外加载100Mhz的时钟信号是不环保的行为,为了地球 sdram必须向fpga借助时钟信号,这个借助的时钟信号也称为供源时钟。对供源时钟而言TimeQuest非常重视它,此外也有相关的约束命令分别针对供源时钟。供源时钟有3种种类,直接供源,寄存器供源,还有pll供源,而图3.5.3的上图就是pll供源。

同学们知道内部模型与外部模型的具体区别吗?内部模型与外部模型的区别就在于知道与不知道,自动与手动。所谓知道与不知道是指,有关内部模型的各种延迟信息TimeQuest可以通过综合器取得。换之,外部模型的延迟信息必须人为劳动,透过相关的约束命令告诉TimeQuest才行,这就是所谓的自动和手动。

3.6约束命令和约束行为

学习约束命令是学习TimeQuest的关键,然而如何理解约束命令的约束行为才能掌握约束命令。约束命令顾名思义就是命令的存在,主要是人类和TimeQuest沟通的工具。而约束行为是约束命令的执行过程。

笔者曾说过TimeQuest就好比网表(硬模型)的仿真软件,约束命令也有各种各样的行为,如第二章所学过的 create_clock 就是建立时钟刺激的约束命令。很遗憾的是,比起约束行为的解释官方更加重视约束命令的使用方法。在研究各种命令的约束行为之际,笔者可吃过不少苦头,呵呵。

此外,笔者也浏览过许多相关的TimeQuest解释,说实在笔者只能用一句“残念”来感叹。先不管约束命令的使用方法对错与否?说实在,使用者到底明不明白自己在使用什么才是笔者最关心的地方。这种情形就好比小孩子玩枪械却不懂枪械的危险。

笔者有一个想法必须交代清楚,据笔者所知 ... 笔者认为约束命令的功用,就是再现分析环境而已,而不是干扰硬模型的实际内容。笔者相信,支持这种解释和反对这种解释的朋友有不相参半 ... 约束命令究竟能不能干扰硬模型的内容?这种问题,只能见仁见智,因为没有绝对的答案。但是换作笔者,笔者宁愿相信TimeQuest只是硬模型的“模拟器”而已,就像Modelsim角色一样。

sdc文件有如vt文件,约束命令好比验证语言 ... 不过Modelsim仿真对象是软模型,而TimeQuest的分析对象是硬模型。Modelsim只用产生理想时序,看看模块的行为是否达到预期的效果。换之TimeQuest只用分析物理时序,看看综合结果是否造就时序违规,或者硬模型能不能在特定的环境下很好运行。

一言盖过,如何使用约束命令不是笔者在乎的地方,而约束命令的行为才是笔者感兴趣的地方。因为笔者相信,通过了解约束行为更能了解TimeQuest和掌握它。

总结:

第三章只是扫盲文而已,不过同学们不要小看扫盲的作用 ... 扫盲文可以给个大体的概念,让读者在接下来的学习用不着像无头苍蝇无头乱飞之余;又可以让读者可以知晓学习的方向。虽然扫盲文的没有仔细的精度,不过扫盲文的作用几乎举足轻重,至于读者信不信就见仁见智了。

从第三章的一开始我们先讨论各种余量的概念。建立余量和保持余量是和TimeQuest模型有关,而保险余量是和网表质量有关。不过,保险余量只是笔者自取的名字而已,与官方无关。黏糊概念是图形表达余量,而建立余量与保持余量是数值表达余量,而保险余量只是概念表达余量。

造成时序违规的凶手就是“延迟因数”,延迟因数有可以分为内部延迟因数愈外部延迟因数。常见的内部延迟因数有:pll,路径(数据路径与时钟路径),还有寄存器特性;而常见的外部延迟因数有:引脚电容性(tRise与tFall),外部走线,还有ic的寄存器特性。

内部延迟因数几乎可以被TimeQuest认知,所以也没有什么好谈的;换之,外部延迟因数TimeQuest却完全不认识。TimeQuest模型也有内部与外部之分,内部模型充满内部延迟因数而外部模型充满外部延迟因数。

就是因为内部延迟因数TimeQuest它什么都知道的关系,所以TimeQuest会自动认识,也用不着认为告诉它相关的延迟信息。反之外部延迟因数就是因为TimeQuest它什么都不知道,结果我们必须手动透过相关的约束命令,再告诉它相关的外部延迟信息。

虽然第三章的内容还插上不相关的第一层和第二层的时间要求概念,不过笔者认为有必要认识一下,如果读者是纯TimeQuest用者,笔者就不勉强明白。反之如果想把HDL与TimeQuest联系起来,明白它们是关键的地方。第一层与第二层时间要求是整合思想下的产物,它们也是黏糊概念的兄弟。

一般上,如果HDL最小时间可以照顾和涉及某个时间要求,称为第一层。换之,如果HDL最小时间只能照顾却无法涉及那个时间要求,就称为第二层。HDL所谓的照顾就是产生理想的时序,而所谓的涉及就是空时间和供源完全相符时间要求。可以照顾却涉及不了的时间要求,只能交给TimeQuest去分析。此外时间要求也分为单个时钟和多个时钟。

最后我们也小谈一下TimeQuest模型的山寨行为,实际上不是要TimeQuest模型去模仿什么 ... 而是分析TimeQuest模型到底能不能在外部成立,典型的外部模型就是fpga与sdram。此外我们也谈到约束命令与约束行为的相关问题,充其量这也是笔者的多疑而已,谈不上什么问题 ... 读者能不能接受就见仁见智了。

【黑金原创教程】【TimeQuest】【第三章】TimeQuest 扫盲文的更多相关文章

- 【黑金原创教程】 FPGA那些事儿 SignalTap II 调试技巧

简介工具篇系列的第三本教程,讲述各种与SignalTap II 有关的调试技巧. 目录[黑金原创教程] FPGA那些事儿<工具篇III>:File01 - 上线调试与下线调试[黑金原创教程 ...

- D3.js的v5版本入门教程(第三章)—— 选择元素和绑定数据

D3.js的v5版本入门教程(第三章) 在D3.js中,选择元素和绑定元素是最基本的内容,也是很重要的内容,等你看完整个教程后你会发现,这些D3.js教程都是在选择元素和绑定元素的基础上展开后续工作的 ...

- 【黑金原创教程】 FPGA那些事儿《概念篇》

简介一本讲述非软硬片上系统的书,另外还是低级建模的使用手册. 目录[黑金原创教程] FPGA那些事儿<概念篇>:File01 - 结构的玩笑[黑金原创教程] FPGA那些事儿<概念篇 ...

- ArcGIS for Desktop入门教程_第三章_Desktop软件安装 - ArcGIS知乎-新一代ArcGIS问答社区

原文:ArcGIS for Desktop入门教程_第三章_Desktop软件安装 - ArcGIS知乎-新一代ArcGIS问答社区 1 软件安装 1.1 安装前准备 请确认已经收到来自Esri中国( ...

- 【黑金原创教程】【TimeQuest】【第一章】TimeQuest 静态时序分析模型的概念

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/ ...

- 【黑金原创教程】【TimeQuest】【第二章】TimeQuest模型角色,网表概念,时序报告

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- 【黑金原创教程】【TimeQuest】【第四章】内部延迟与其他

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- 【黑金原创教程】【TimeQuest】【第五章】网表质量与外部模型

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- 【黑金原创教程】【TimeQuest】【第七章】供源时钟与其他

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

随机推荐

- 使用maven开发OSGI样例

一:创建maven项目,在pom.xml里面增加例如以下依赖 <dependency> <groupId>org.osgi</groupId> <artifa ...

- hdu 1022 Train Problem I(栈的应用+STL)

Train Problem I Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 65536/32768 K (Java/Others) ...

- Atitit.软件GUI按钮与仪表盘(01)--js区-----js格式化的使用

Atitit.软件GUI按钮与仪表盘(01)--js区-----js格式化的使用 1. Chrome36( recomm) DEV TOOL>SOURCE> DSWEIHAMYAR &q ...

- spring 学习资料备份

易百教程 https://www.yiibai.com/spring/spring-autowiring-by-name.html

- Centos Java 从1.7升级为1.8

查看安装的sdk版本 yum list installed |grep java 卸载JDK相关文件输入和tzdata-java输入 yum -y remove java-1.7.0-openjdk* ...

- 基础地图Android SDK

开发者可利用SDK提供的接口,使用百度为您提供的基础地图数据.目前百度地图SDK所提供的地图等级为3-21级,所包含的信息有建筑物.道路.河流.学校.公园等内容. V3.7.0起,地图支持缩放至21级 ...

- URL与URI

1.URI是统一资源标识符,是一个用于标识某一互联网资源名称的字符串. 该种标识允许用户对任何(包括本地和互联网)的资源通过特定的协议进行交互操作.URI由包括确定语法和相关协议的方案所定义.由是三个 ...

- Shape Control for .NET

Shape Control for .NET Yang Kok Wah, 23 Mar 2017 CPOL 4.83 (155 votes) Rate this: vote 1vote 2v ...

- JS学习笔记(5)--一道返回整数数组的面试题(经验之谈)

说明: 1. 微信文章里看到的,作者是马超 网易高级前端技术经理,原文在网上搜不到,微信里可以搜“为什么你的前端工作经验不值钱?”,里面写着“转载自网易实践者社区”.(妈蛋,第二天网上就有了http: ...

- Okra框架(二) 搭建Socket服务器

本文将介绍使用Okra框架帮助开发者快速搭建高性能应用程序Socket服务端. 博主接触的网络游戏(包含但不限于网页, 手机)的服务端通信使用的协议基本上就Socket,Http或是WebSocket ...