13. DMA

1. DMA简介

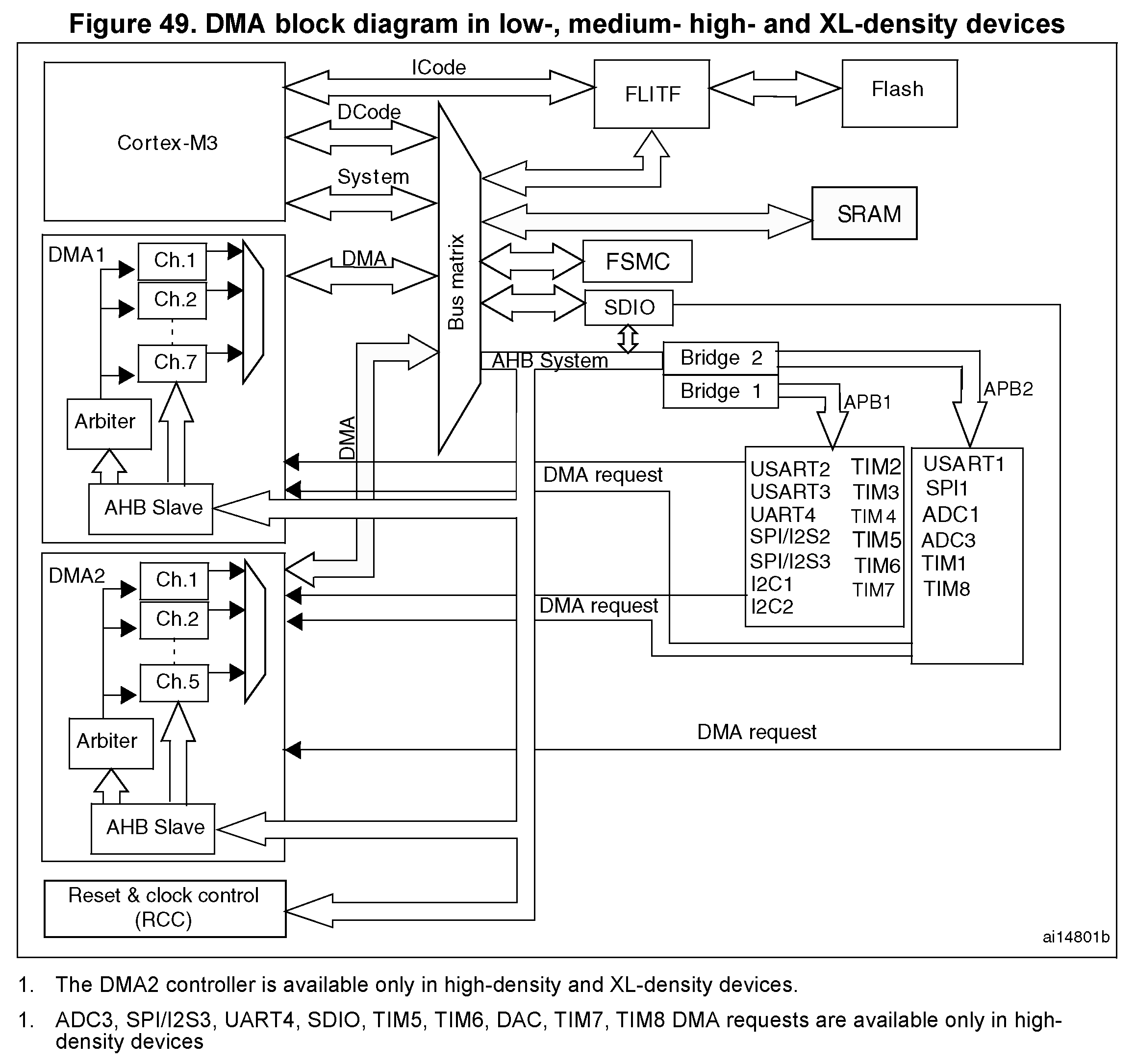

直接存储器存取(Dma)是为了提供高速数据传输外围设备和内存以及内存到内存。数据可以通过dma快速移动。没有任何CPU操作。这使得CPU资源可以用于其他操作。

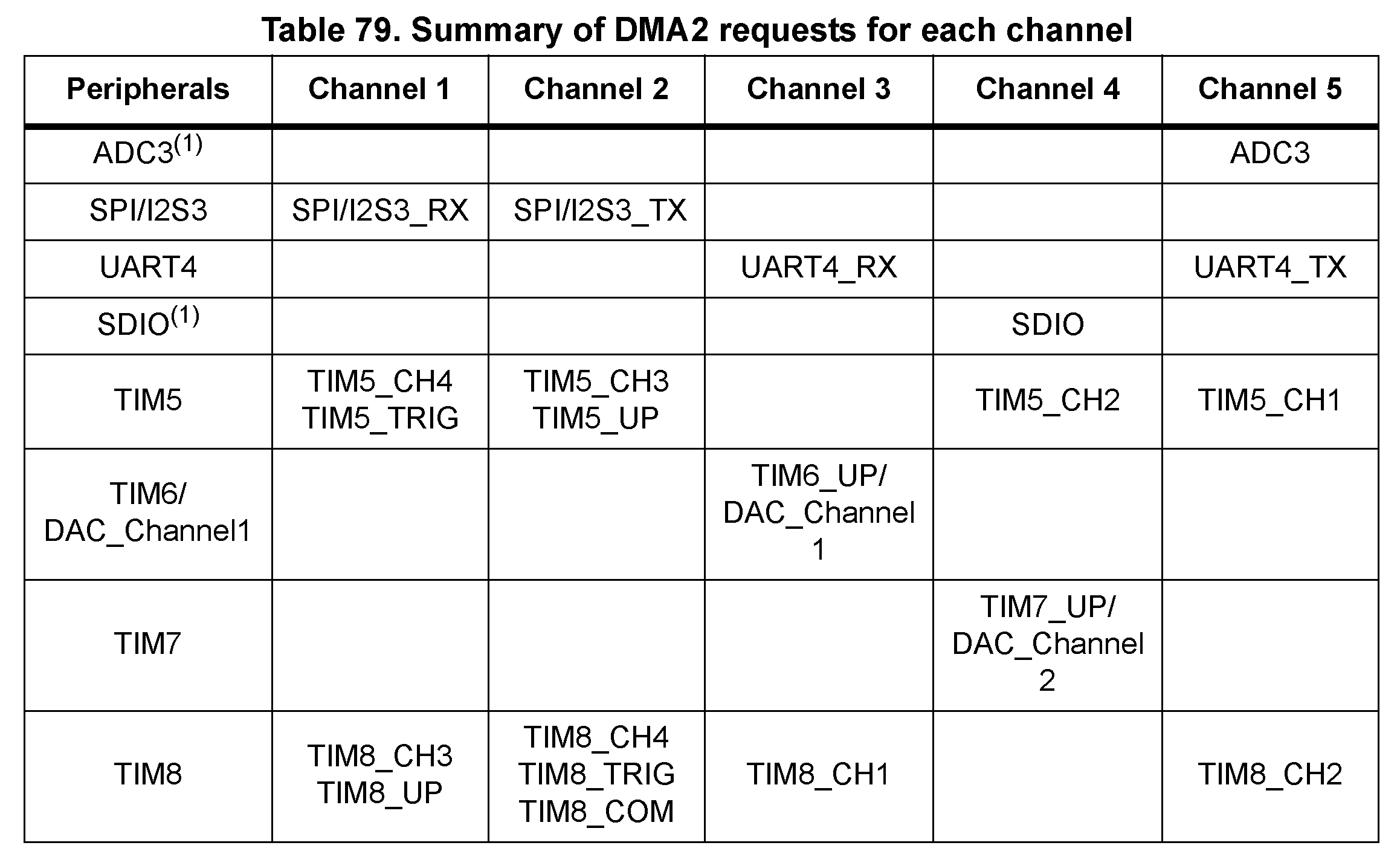

这两个DMA控制器总共有12个通道(DMA 1的7个通道和DMA 2的5个通道),每个通道都有。专用于管理来自一个或多个外围设备的内存访问请求。它有一个用于处理DMA请求之间优先级的仲裁器。

2. DMA 主要特点

- 12个可独立配置的通道(请求):7个用于DMA 1,5个用于DMA 2

- 12个通道中的每个通道都连接到专用硬件DMA请求和软件每个通道也支持触发器。此配置由软件完成。

- 来自一个DMA通道的请求之间的优先级是软件可编程的(包括非常高、高、中、低的4个级别)或在平等情况下的硬件。(请求1优先于请求2等)

- 独立的源和目标传输大小(字节,半字,字),模拟包装和拆包。源/目标地址必须根据数据大小对齐。

- 支持循环缓冲区管理

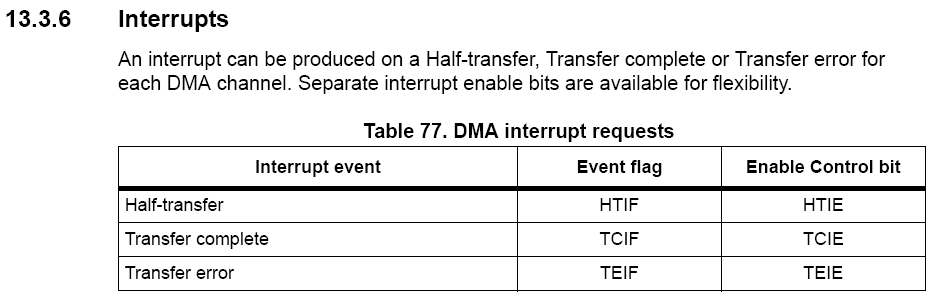

- 3个事件标志(DMA半传输、DMA传输完成和DMA传输错误)逻辑连接在单个中断请求中的每个通道

- 内存到内存传输

- 外设对内存和内存到外围,以及外围到外围的传输

- 可访问作为源和目的地的Flash、SRAM、APB1、APB2和AHB外围设备

- 要传输的可编程数据数:最多可达65536

3. DMA 功能描述

DMA控制器通过与Cortex®-M3核心共享系统总线来执行直接内存传输。

当cpu和dma针对同一个目标(内存或(外围),dma请求可能会在某些总线时间内停止cpu对系统总线的访问。

总线矩阵实现循环调度,从而保证CPU可用至少一半的系统总线带宽(包括内存和外设)。

3.1 DMA事务

事件发生后,外设向DMA控制器发送请求信号。DMA控制器根据信道优先级为请求提供服务。DMA控制器一访问外围设备,DMA控制器就会向外设发送确认信息。外设一旦从DMA控制器获得确认信息,就会释放其请求。一旦请求被外围设备取消,DMA控制器就会释放确认。如果有更多的请求,外围设备可以启动下一个事务。

总之,每个DMA传输包括三个操作:

- 从外围数据寄存器或通过内部当前外围/存储器地址寄存器寻址的存储器中的位置加载数据。用于第一次传输的起始地址是在DMA_CPARx或DMA_CMARx寄存器中编程的基本外围/内存地址。

- 存储加载到外围数据寄存器或通过内部当前外设/存储器地址寄存器寻址的存储器中的数据。用于第一次传输的起始地址是在DMA_CPARx或DMA_CMARx寄存器中编程的基本外围/内存地址。

- DMA_CNDTRx寄存器的后递减,其中包含仍需执行的事务数。

3.3 DMA信道

每个信道可以处理位于固定地址和存储器地址的外围寄存器之间的DMA传输。要传输的数据量(高达65535)是可编程的。包含要传输的数据项数量的寄存器在每个事务之后减少。

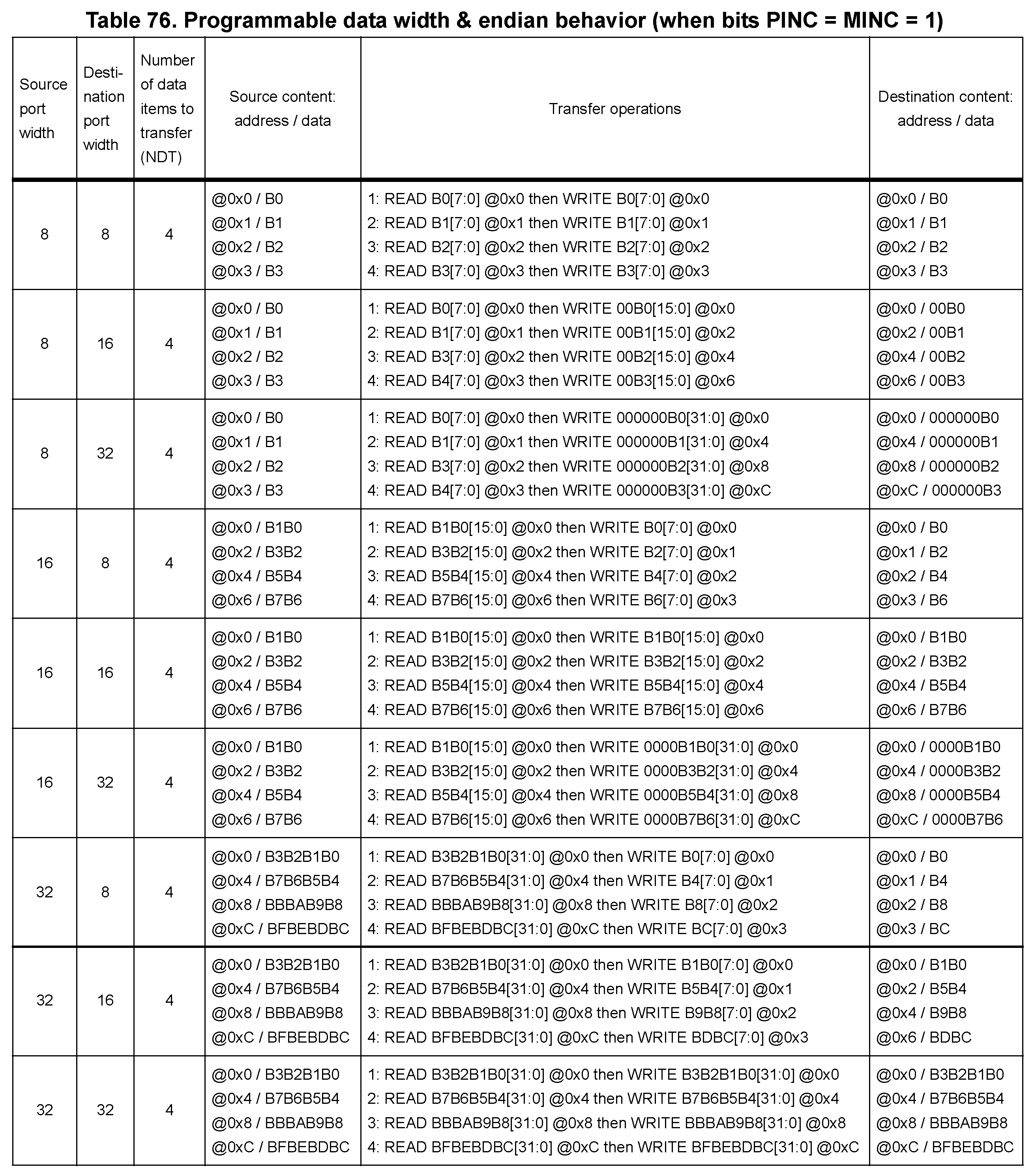

可编程数据大小

外设和存储器的传输数据大小通过DMA_CCRx寄存器中的PSIZE和MSIZE位完全可编程。

指针增量

外设和内存指针可以根据DMA_CCRx寄存器中的PINC和MINC位在每个事务后自动递增。如果启用了增量模式,则下一次传输的地址将是上一次传输的地址,根据所选数据大小而递增1、2或4。第一个传输地址是在DMA_CPARx/DMA_CMARx寄存器中编程的地址。在传输操作期间,这些寄存器保留最初编程的值。软件无法访问当前传输地址(在当前内部外围/内存地址寄存器中)。

如果信道配置为非循环模式,则在最后一次传输之后(即一旦要传输的数据项数达到零时)不提供DMA请求。为了重新加载要传输到DMA_CNDTRx寄存器中的新数据项,必须禁用DMA通道。

说明:

如果DMA通道被禁用,DMA寄存器不会被重置。DMA通道寄存器(DMA_CCRx、DMA_CPARX和DMA_CMARx)保留在通道配置阶段编程的初始值。

在循环模式中,在上次传输之后,DMA_CNDTRX寄存器会自动重新加载初始编程值。当前内部地址寄存器从DMA_CPARX/DMA_CMARx寄存器中重新加载基址值。

信道配置过程

应该按照以下顺序配置DMA通道(其中x是信道号)。

- 在 DMA_CPARx 寄存器中设置外设寄存器地址。

- 在 DMA_CMARx 寄存器中设置内存地址。数据将在外围事件之后写入或从该存储器中读取。

- 配置要在DMA_CNDTRX寄存器中传输的数据总数。在每个外围事件之后,该值将递减。

- 使用DMA_CCRx寄存器中的 PL[1:0] 位配置通道优先级

- 配置数据传送方向、循环模式、外围设备和内存增加模式、外设和内存数据大小,以及在半传输或者满传输后中断DMA_CCRX寄存器

- 通过在DMA_CCRx寄存器中设置启用位来激活通道。

一旦通道被启用,它就可以从连接在通道上的外围设备中处理任何DMA请求。一旦传输了一半的字节,就会设置半传输标志(HTIF),如果设置了半传输中断启用位(HTIE),则会产生中断。在传输结束时,设置传输完全标志(TCIF),如果设置了传输完全中断启用位(TCIE),则产生中断。

循环模式

循环模式可用于处理循环缓冲器和连续数据流(例如adc扫描模式)。可以使用DMA_CCRx寄存器中的CIRC位启用此特性。当循环模式被激活时,要传输的数据的数量会用在信道配置阶段编程的初始值自动重新加载,并且DMA请求继续被处理。

内存到内存模式

DMA通道也可以工作,而不被来自外围设备的请求触发。这种模式称为内存到内存模式。如果在DMA_CCRx寄存器中设置了MEM2MEM位,则该信道通过在DMA_CCRx寄存器中设置使能位(En),在软件启用后立即启动传输。当DMA_CNDTRx寄存器达到零时,传输停止。内存到内存模式不能与循环模式同时使用。

3.4 可编程数据宽度、数据对齐

当PSIZE和MSIZE不相等时,DMA执行一些数据对齐,如表76所述。

寻址不支持字节或半字写入的AHB外围设备操作:

当DMA启动AHB字节或半字写入操作时,数据将复制到没使用的HWDATA[31:0]总线。

因此,当使用的AHB从外围设备不支持字节或半字写入操作(当外设不使用HSIZE时)并且不生成任何错误时,DMA写入32 HWDATA位,如下所示:

- 为了编写半字“0xABCD”,DMA使用HSIZE=HalfWord将HWDATA总线设置为“0xABCDABCD”。

- 为了编写字节“0xAB”,DMA使用HSIZE=Byte将HWDATA总线设置为“0xABABABAB”

假设AHB/APB桥是不考虑HSIZE数据的AHB 32位从外围设备,它将以下列方式将任何AHB字节或半字操作转换为32位APB操作:

- 将数据“0xB0”写入0x0(或0x1、0x2或0x3)的AHB字节写入操作将转换为数据“0xb0b0b0b0”到0x0的APB字写操作

- 数据“0xb1b0”到0x0(或0x2)的AHB半字写操作将转换为数据“0xB1B0B1B0”到0x0的APB字写操作

例如,如果要编写apb备份寄存器(与32位地址边界对齐的16位寄存器),则必须将内存源大小(MSIZE)配置为“16位”,将外围目标大小(PSIZE)配置为“32位”。

3.5 错误管理

DMA传输错误可以通过从保留地址空间读取或写入而产生。当DMA读或写访问期间发生DMA传输错误时,故障信道通过相应信道配置寄存器(DMA_CCRx)中的en位的硬件自动禁用。在DMA_IFR寄存器中设置信道的传输错误中断标志(TEIF),如果在DMA_CCRx寄存器中设置传输错误中断启用位(TEIE),则产生中断。

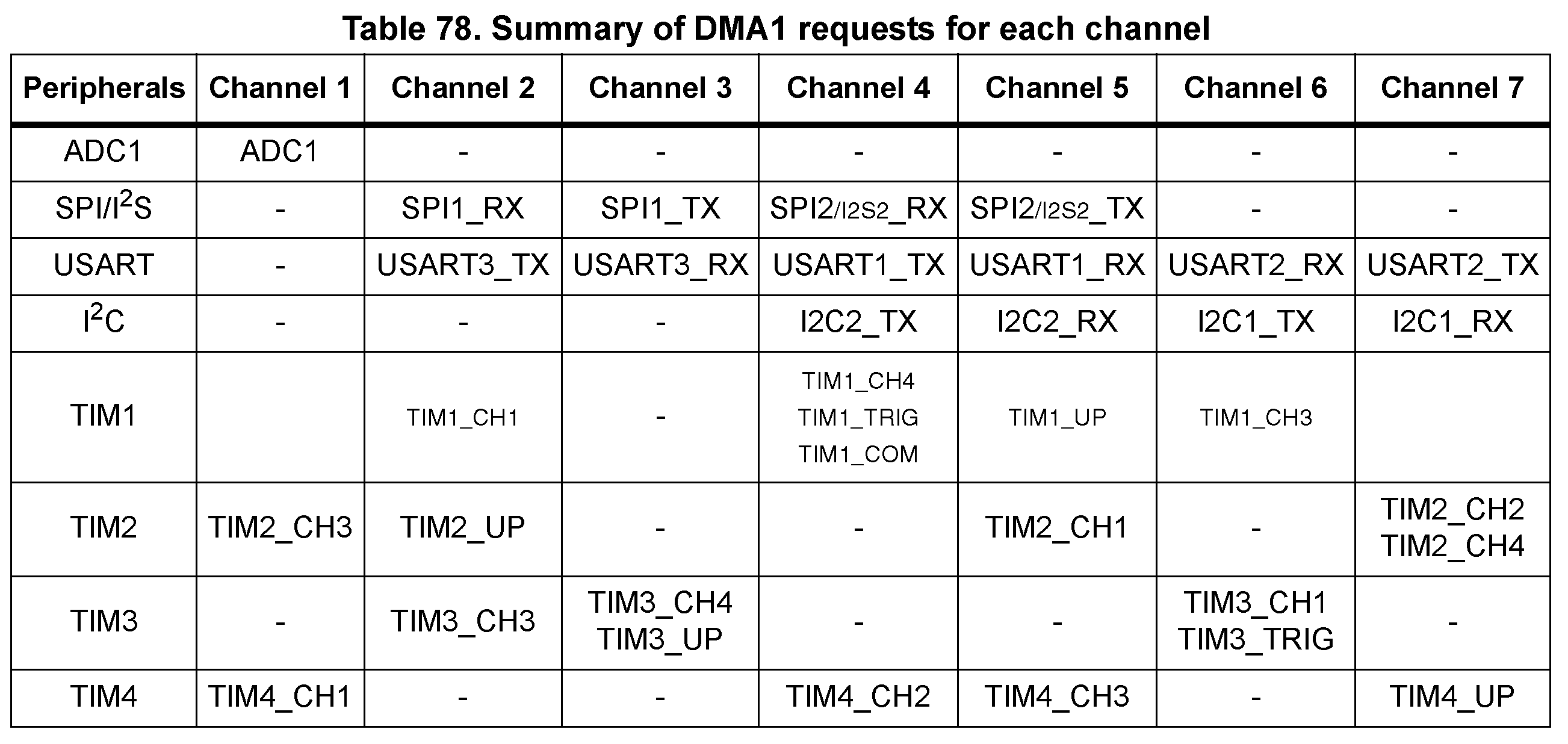

3.7 DMA request mapping

4 DMA registers

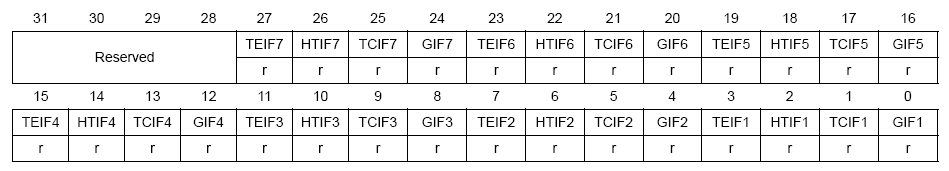

4.1 DMA interrupt status register (DMA_ISR)

TEIFx: Channel x transfer error flag (x = 1 ..7) This bit is set by hardware. It is cleared by software writing 1 to the corresponding bit in the DMA_IFCR register.

0: No transfer error (TE) on channel x

1: A transfer error (TE) occurred on channel x

HTIFx: Channel x half transfer flag (x = 1 ..7) This bit is set by hardware. It is cleared by software writing 1 to the corresponding bit in the DMA_IFCR register.

0: No half transfer (HT) event on channel x

1: A half transfer (HT) event occurred on channel x

TCIFx: Channel x transfer complete flag (x = 1 ..7) This bit is set by hardware. It is cleared by software writing 1 to the corresponding bit in the DMA_IFCR register.

0: No transfer complete (TC) event on channel x

1: A transfer complete (TC) event occurred on channel x

GIFx: Channel x global interrupt flag (x = 1 ..7) This bit is set by hardware. It is cleared by software writing 1 to the corresponding bit in the DMA_IFCR register.

0: No TE, HT or TC event on channel x

1: A TE, HT or TC event occurred on channel x

4.2 DMA interrupt flag clear register (DMA_IFCR)

4.3 DMA channel x configuration register (DMA_CCRx) (x = 1..7, where x = channel number)

Bit 14 MEM2MEM: Memory to memory mode This bit is set and cleared by software.

0: Memory to memory mode disabled

1: Memory to memory mode enabled

Bits 13:12 PL[1:0]: Channel priority level These bits are set and cleared by software.

00: Low

01: Medium

10: High

11: Very high

Bits 11:10 MSIZE[1:0]: Memory size These bits are set and cleared by software.

00: 8-bits

01: 16-bits

10: 32-bits

11: Reserved

Bits 9:8 PSIZE[1:0]: Peripheral size These bits are set and cleared by software.

00: 8-bits

01: 16-bits

10: 32-bits

11: Reserved

Bit 7 MINC: Memory increment mode This bit is set and cleared by software.

0: Memory increment mode disabled

1: Memory increment mode enabled

Bit 6 PINC: Peripheral increment mode This bit is set and cleared by software.

0: Peripheral increment mode disabled

1: Peripheral increment mode enabled

Bit 5 CIRC: Circular mode This bit is set and cleared by software.

0: Circular mode disabled

1: Circular mode enabled

Bit 4 DIR: Data transfer direction This bit is set and cleared by software.

0: Read from peripheral

1: Read from memory

Bit 3 TEIE: Transfer error interrupt enable

This bit is set and cleared by software.

0: TE interrupt disabled

1: TE interrupt enabled

Bit 2 HTIE: Half transfer interrupt enable

This bit is set and cleared by software.

0: HT interrupt disabled

1: HT interrupt enabled

Bit 1 TCIE: Transfer complete interrupt enable

This bit is set and cleared by software.

0: TC interrupt disabled

1: TC interrupt enabled

Bit 0 EN: Channel enable

This bit is set and cleared by software.

0: Channel disabled

1: Channel enabled

4.4 DMA channel x number of data register (DMA_CNDTRx) (x = 1..7), where x = channel number)

要传输的数据数量(0到65535)。只有当通道被禁用时,才能写入此寄存器。一旦通道被启用,这个寄存器就是只读的,指示要传输的剩余字节.此寄存器在每次DMA传输后都会减少。一旦传输完成,此寄存器可以保持在零或重新加载。如果通道配置为自动重新加载模式,则由先前编程的值自动设置。

如果此寄存器为零,则无论是否启用通道,都无法处理任何事务。

4.5 DMA channel x peripheral address register (DMA_CPARx) (x = 1..7), where x = channel number)

Bits 31:0 PA[31:0]: Peripheral address

Base address of the peripheral data register from/to which the data will be read/written.

When PSIZE is 01 (16-bit), the PA[0] bit is ignored. Access is automatically aligned to a halfword address.

When PSIZE is 10 (32-bit), PA[1:0] are ignored. Access is automatically aligned to a word address.

4.6 DMA channel x memory address register (DMA_CMARx) (x = 1..7), where x = channel number)

Bits 31:0 MA[31:0]: Memory address

数据将被读写到的内存区域的基本地址。

当MSIZE为01(16位)时,MA[0]位被忽略.Access自动对齐到半字地址。

当MSIZE为10(32位)时,MA[1:0]被忽略.Access将自动对齐到一个单词地址。

13. DMA的更多相关文章

- 基本的DMA控制器

DMA的基本概念 直接内存访问(DMA)是一种完全由硬件执行I/O交换的工作方式.在这种方式中,DMA控制器从CPU完全接管对总线的控制,数据交换不经过CPU,而直接在内存和I/O设备之间进行 .DM ...

- STM32F103之DMA学习记录

/================翻译STM32F103开发手册DMA章节===========================/ 13 DMA(Direct memory access) 13.1 ...

- 成为Android高手必须掌握的28大项内容和10个建议

(一)成为Android高手必须掌握的8项基本要求 [1] Android操作系统概述1. Android系统架构. 2. Android利用设计理念. 3. ...

- 关于启动文件分析的(MDK-ARM) 【转】

;******************** (C) COPYRIGHT 2010 STMicroelectronics ******************** ;* File Name : star ...

- TMS320C64x DSP L1 L2 Cache架构(1)——C64x Cache Architecture

[前沿]研究生阶段从事于DSP和FPGA技术的相关研究工作,学习并整理了大量的技术资料,包括TI公司的官方文档和网络上的详细笔记,花费了大量的时间和精力总结了前人的工作成果.无奈工作却从事于嵌入式技术 ...

- STM32笔记四

1.时钟振荡器:产生时钟信号送给单片机内部各电路,并且控制这些电路,使它们有节拍的工作. 2.ROM是一种具有存储功能的电路,断电后信息不回丢失.RAM也是一种存储电路,断电后信息丢失. 3.串行通信 ...

- Linux就这个范儿 第13章 打通任督二脉

Linux就这个范儿 第13章 打通任督二脉 0111010110……你有没有想过,数据从看得见或看不见的线缆上飞来飞去,是怎么实现的呢?数据传输业务的未来又在哪里?在前面两章中我们学习了Linux网 ...

- mmap DMA【转】

转自:http://blog.csdn.net/lihaoweiv/article/details/6275241 第 13 章 mmap 和 DMA 本章将深入探讨 Linux 内存管理部分,并强 ...

- 内存映射MMAP和DMA【转】

转自:http://blog.csdn.net/zhoudengqing/article/details/41654293 版权声明:本文为博主原创文章,未经博主允许不得转载. 这一章介绍Linux内 ...

随机推荐

- 什么是 CSS?

什么是 CSS? CSS 指层叠样式表 (Cascading Style Sheets) 样式定义如何显示 HTML 元素 样式通常存储在样式表中 把样式添加到 HTML 4.0 中,是为了解决内容与 ...

- delphi INI文件

INI 文件读写 filecreate('路径加文件名')://创建一个文件. (1) INI文件的结构: ;这是关于INI文件的注释部分 [节点] 关键字=值 ... INI文件允许有多个节点,每个 ...

- [Go语言]cgo用法演示

经历了数十年发展的C语言,各种各样的现成的库已经非常丰富.通过cgo,可以在Go语言中使用C语言代码,充分利用好现有的“轮子”. 本文所有代码,在下述环境中调试通过: Windows 8.1 ...

- Selenium2Library中select frame关键字对没有name和id的frame或者iframe的处理

elenium2Library中原有的select_frame函数(对应的关键字为select frame)可根据locator选择frame,但是,若某个frame或者iframe没有id,没有na ...

- ASP.NET Core学习——3

中间件 中间件是用于组成应用程序管道来处理请求和相应的组件.管道内的每一个组件都可以选择是否将请求交给下一个组件,并在管道中调用下一个组件之前和之后执行某些操作.请求委托被用来建立请求管道,请求委托处 ...

- html select美化模拟jquery插件select2.js

代码展示:http://www.51xuediannao.com/demo.php 代码说明: select2.js是一个html select美化模拟类jquery插件,但是select2.js又远 ...

- 【Linux】- Systemd 命令篇

转自:阮一峰的网络日志 Systemd 是 Linux 系统工具,用来启动守护进程,已成为大多数发行版的标准配置. 一.由来 历史上,Linux 的启动一直采用init进程. 下面的命令用来启动服务. ...

- Redis数据结构之快速列表-quicklist

链表 在Redis的早期版本中,存储list列表结构时,如果元素少则使用压缩列表ziplist,否则使用双向链表linkedlist // 链表节点 struct listNode<T> ...

- vim的基本快捷操作(一)

一.光标移动 ^ 到该行第一个非空格字符处. + 到下一行的第一个非空格字符处 - 到上一行的第一个非空格字符处 `. 到上次修改点 <c-o> 到上次所停留位置, <c-i> ...

- 项目中UX设计1到2的设计提升总结