基于fpga的vga学习(1)

这次学习我主要掌握了vga的基本运行原理。

vga基本概念:

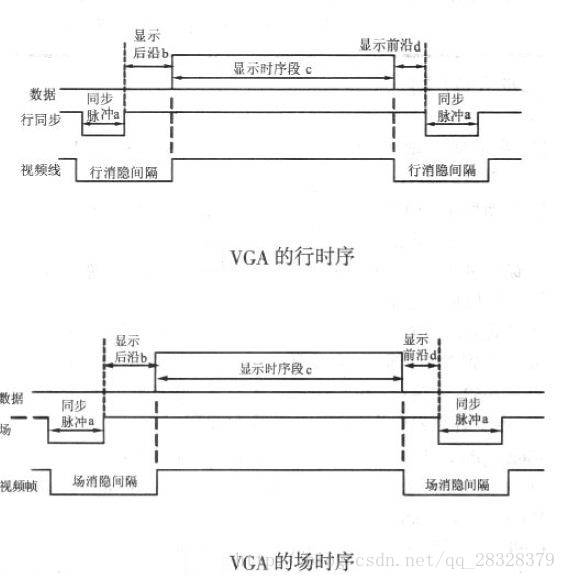

VGA时序主要包括两条信号线(HS,VS)的输出——行扫描和场扫描。VGA采用逐行扫描,每个像素对应的点扫描。行与行之间存在消隐以及显示时期,场与场之间也类似。行扫描可分为以下几个阶段:同步、消隐后肩、显示期、消隐前肩再到下个周期同步为一个循环,对应的是屏幕上的一行。场同步类似,对应为屏幕显示的一帧。标准的VGA屏幕比例为4:3有固定的帧率以及扫描场频率的标准。

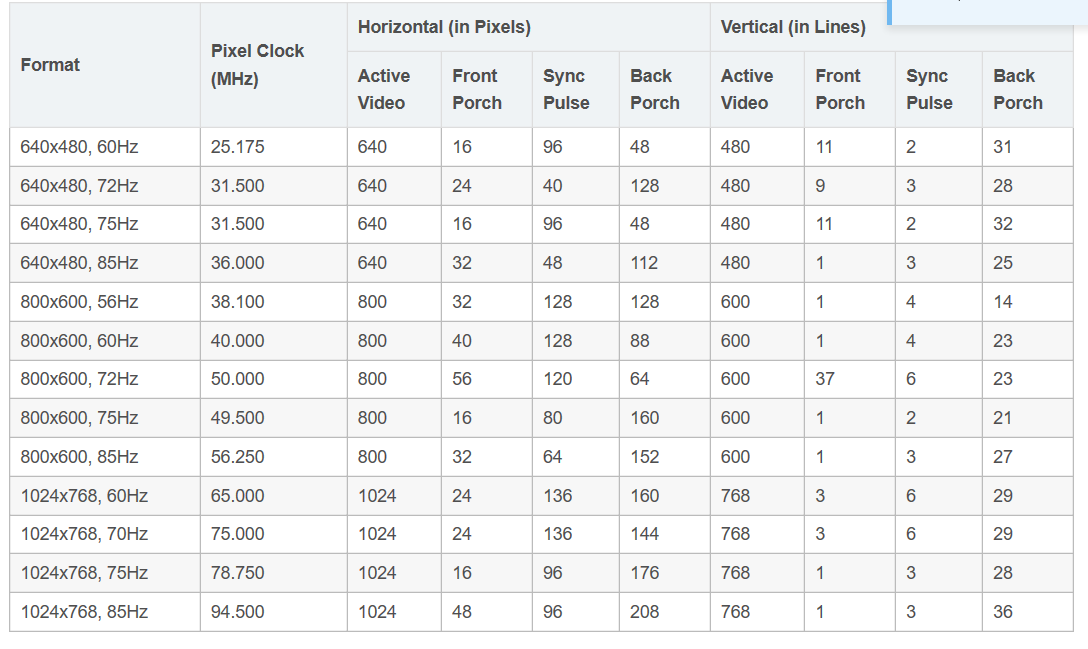

常见的4:3 vga时序表:

网上找的场和行的时序表:

这里可以看出,想要实现基本的vga其实 不难,只需要用verilog描述出:同步脉冲、后沿、前沿、和有效显示区域即可

接下来是代码

module vga(

input clk,

input rst,

output hsync, // 行同步信号

output vsynv, // 场同步信号

output vga_r,

output vga_g,

output vga_b

);

reg [10:0]x_cnt; //行坐标计数器 0~1039-1

reg [9:0]y_cnt; //列坐标计数器 0~666-1

always @(posedge clk or negedge rst)

begin

if(!rst)

x_cnt <= 0;

else if(x_cnt == 11'd1039 - 1)

x_cnt <= 0;

else

x_cnt <= x_cnt + 1;

end

always @(posedge clk or negedge rst)

begin

if(!rst)

y_cnt <= 0;

else if(y_cnt == 10'd666 - 1)

y_cnt <= 0;

else if(x_cnt == 11'd1039 - 1)

y_cnt <= y_cnt + 1;

end

wire valid; //有效显示区域来临的标志

assign valid = (x_cnt >= 11'd187) && (x_cnt < 11'd987)

&& (y_cnt >= 10'd31 ) && (y_cnt < 10'd631);

wire [9:0] xpos,ypos; // 有效的显示区域 800 * 600

assign xpos = x_cnt - 11'187; // 从0开始计数

assign ypos = y_cnt - 10'd31;

reg r_hsync,r_ysync; // 同步信号的产生

always @(posedge clk or negedge rst)

begin

if(!rst)

r_hsync <= 1'b1;

else if(x_cnt == 11'd0)

r_hsync <= 0;

else if(x_cnt == 11'd120 - 1)

r_hsync <= 1'b1

end

always @(posedge clk or negedge rst)

begin

if(!rst)

r_ysync <= 1'b1;

else if(y_cnt == 10'd0)

r_ysync <= 0;

else if(y_cnt == 10'd6 - 1)

r_ysync <= 1'b1

end

assign hsync = r_hsync;

assign vsync = r_vsync;

最后,我让vga在屏幕的左边显示黑色,右边显示蓝色:

always @(*)

begin

if(xpos <= 400) // 黑

vga_r = 0;

vga_g = 0;

vga_b = 0;

else

vga_r = 0; // 蓝

vga_g = 0;

vga_b = 1;

end

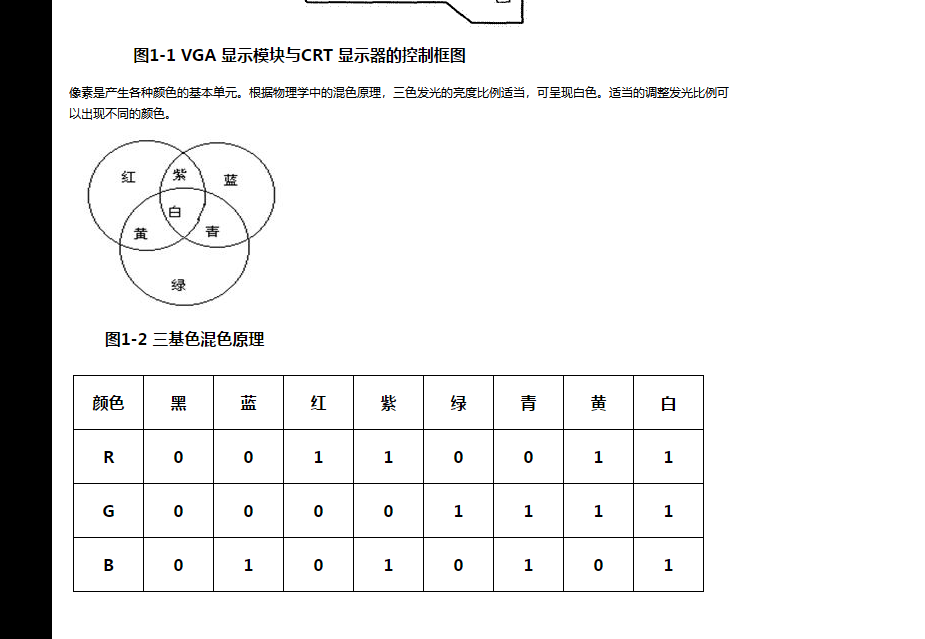

最后附上vga颜色搭配

基于fpga的vga学习(1)的更多相关文章

- 基于fpga的vga学习(3)

本次学习如何通过vga发送数字.文字.字母, 首先利用建模软件,将想要发送的数据通过数学建模转换,这里我用的软件是PCtoLCD,具体效果如下 这里可以看出,建模将数据装换成0和1,一个字母用16x8 ...

- 基于fpga的vga学习(2)

本次学习主要向配合basys2实行. 上次学习vga的rgb三个output都是1位的,但是我看了basys2的rgb分别是332位,这里让我卡顿了很久, 之后通过查资料才知道,rgb的不同大小表示的 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- 基于FPGA的VGA可移植模块终极设计【转】

本文转载自:http://www.cnblogs.com/lueguo/p/3373643.html 略过天涯 基于FPGA的VGA可移植模块终极设计 一.VGA的诱惑 首先,VGA的驱动,这事, ...

- 基于FPGA的VGA显示实验设计

基于FPGA的VGA显示实验设计 成果展示(优酷视频): 视频: 基于FPGA的VGA显示技术(手机控制) http://v.youku.com/v_show/id_XNjk4ODE3ODUy.htm ...

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- [置顶]

基于FPGA的VGA简易显存设计&NIOS ii软核接入

项目简介 本项目基于Altera公司的Cyclone IV型芯片,利用NIOS II软核,2-port RAM与时序控制模块,实现64*48分辨率的显存(再大的显存板载资源m9k不够用) 实现效果如下 ...

- 基于FPGA驱动VGA显示图片的小问题

学习VGA显示图片的过程中,遇到了一个小问题,我在显示屏上开了一个60x60的框,放了一张图片进去显示,但是最终的结果如下图所示. 出现了一个竖黑边,看了看代码,分析了一下逻辑没问题,然而看这个显示那 ...

- 基于FPGA的VGA显示设计(一)

前言 FPGA主要运用于芯片验证.通信.图像处理.显示VGA接口的显示器是最基本的要求了. 原理 首先需要了解 : (1)VGA接口协议:VGA端子_维基百科 .VGA视频传输标准_百度 引脚1 RE ...

随机推荐

- 产品大神1--工具axure

一,axure安装 链接:https://pan.baidu.com/s/1rb3SH5HSogP1k_ARTZTflA 提取码:084p 二,axure8.0的使用 因为下面的文章都已经写的非常详细 ...

- C#读取OPC server

1.安装opc server https://blog.csdn.net/yhtppp/article/details/80676118 2.c#读取opc https://github.com/le ...

- JUnit源码分析 - 扩展 - 自定义RunListener

RunListener简述 JUnit4中的RunListener类用来监听测试执行的各个阶段,由RunNotifier通知测试去运行.RunListener与RunNotifier之间的协作应用的是 ...

- jQuery轮播图--不使用插件

说明:引入jquery.min.js 将轮播图放入imgs文件夹 <!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitiona ...

- js给页面添加回车监测事件,实现回车登录功能

document.body.addEventListener('keyup', function (e) { ') { $("#btn_login").click(); } }) ...

- vue打开新页面

let tempPage = window.open('_blank');//先打开一个空白页 this.$axios.post("/aliPay/aliTradePagePay" ...

- server 打开失败

server:An unexpected exception was thrown. 当server服务器遇到这样遇到不能料想的错误导致打开失败的情况下,我们可以找到一个com.genuitec.ec ...

- python 将mysql数据库中的int类型修改为NULL 报1366错误,解决办法

gt.run_sql()是用pymysql 封装的类 distribution_sort_id type: int目的:将此字段值全部修改为NULL g=2gt.run_sql("updat ...

- 10.spring-boot基于角色的权限管理页面实现

10.spring-boot基于角色的权限管理页面实现

- 安卓adb工具的安装方法

adb是Android的一个很重要的调试工具,熟练掌握后可实现很多功能,比如有些手机的解锁.ROOT就会用到adb工具.可很多朋友都说不会安装,今天就从最开始的安装方法说起. adb工具其实不用安装, ...