浅析Xilinx 三速以太网MAC IP核

之前在使用Altera的三速以太网MAC IP的基础上,完成了UDP协议数据传输。此次为了将设计移植到xilinx FPGA上,需要用到xilinx的三速以太网MAC IP核,当然也可以自己用HDL编写,但必须对数据链路层协议有非常清晰的认识。以下是在使用xilinx 三速以太网MAC过程中的一些记录和总结。

在使用IP核传输数据之前要对MAC层功能有个了解。MAC层功能用一个词概括就是“成帧解帧”,具体来讲TX方向对用户侧发送来的MAC帧添加前导码和帧尾校验和,对长度过短帧会在帧尾填充0直至最小帧长,此外流控模块可以根据需要发送pause帧。RX方向过滤掉不符合规范的数据帧并移除填充域,只有目的MAC地址与自身相符且帧尾校验和正确的数据帧才为有效数据帧,去除前导码和校验域后即发送给用户侧。接收端也会根据可能收到的pause帧做出暂停发送处理。

认识以太网帧结构同样非常重要,目前常见的是Ethernet II和IEEE802.3两种格式,总体可以归纳为:目的MAC地址 源MAC地址 长度/类型 有效负荷(可能有填充) 帧校验,长度依次是6byte、6byte、2byte、46~1500byte、4byte。区别在于Ethernet II帧长度/类型域解释为上层协议类型,而IEEE802.3同样位置是长度字段。区分两者的标准是:当该字段值小于等于1500(十六进制的0x05DC)时,为IEEE802.3格式;当字段值大于等于1536(或者十六进制的0x0600)时,帧使用的是Ethernet II格式。其中Ethernet II最为常见。

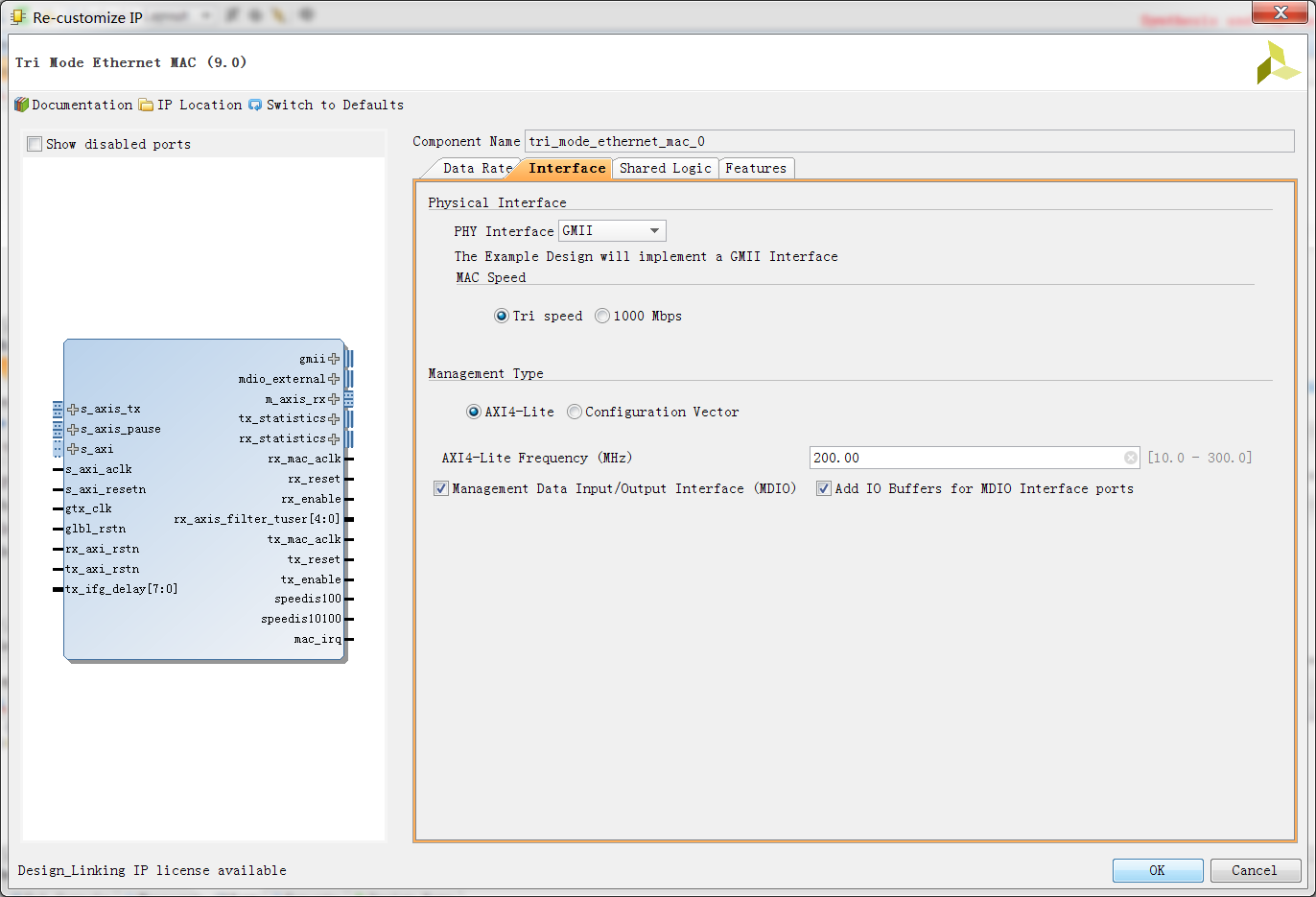

IP核的配置很简单,根据自己的需求设置即可。重点关注第二页,这里选择使用GMII作为物理层接口,并选择三速模式,可以通过接口改动传输速率。

IP核配置生成输出文件后,和其他较为复杂的IP核一样要熟读文档和分析example design的结构和功能。资料主要参考PG051.我们直接打开example design顶层文件对工程有个整体的认识:

// --------------------------------------------------

// | EXAMPLE DESIGN WRAPPER |

// | |

// | |

// | ------------------- ------------------- |

// | | | | | |

// | | Clocking | | Resets | |

// | | | | | |

// | ------------------- ------------------- |

// | -------------------------------------|

// | |FIFO BLOCK WRAPPER |

// | | |

// | | |

// | | ----------------------|

// | | | SUPPORT LEVEL |

// | -------- | | |

// | | | | | |

// | | AXI |->|------------->| |

// | | LITE | | | |

// | | SM | | | |

// | | |<-|<-------------| |

// | | | | | |

// | -------- | | |

// | | | |

// | -------- | ---------- | |

// | | | | | | | |

// | | |->|->| |->| |

// | | PAT | | | | | |

// | | GEN | | | | | |

// | |(ADDR | | | AXI-S | | |

// | | SWAP)| | | FIFO | | |

// | | | | | | | |

// | | | | | | | |

// | | | | | | | |

// | | |<-|<-| |<-| |

// | | | | | | | |

// | -------- | ---------- | |

// | | | |

// | | ----------------------|

// | -------------------------------------|

// -------------------------------------------------- //------------------------------------------------------

上边是官方提供的注释,非常清晰地给出了工程结构:

example_clocks: 时钟模块,提供工程中用到的所有时钟信号;

example_resets: 复位模块,产生所有子模块的复位信号;

axi_lite_controller: 控制模块,内部通过状态机对MAC和PHY芯片进行初始化和相应配置工作。

basic_pat_gen_inst: 包测试模块,有两种模式:发送固定样式测试数据包和将收到数据包环回送出给PHY。

trimac_fifo_block: AXI-S接口异步FIFO和MAC IP核。

MAC IP核包含的主要接口类型及作用是:

GMII接口--PHY数据通道 MDIO接口--PHY芯片配置管理 AXI-Stream接口--用户数据通道 AXI-Lite接口--用户控制管理

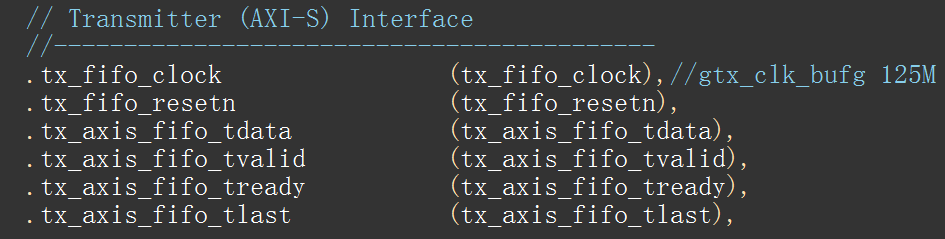

初步需要掌握的是用户数据接口,实际上AXI-Stream也无需过多关注,只要理解FIFO用户侧接口即可。以发送方向为例:

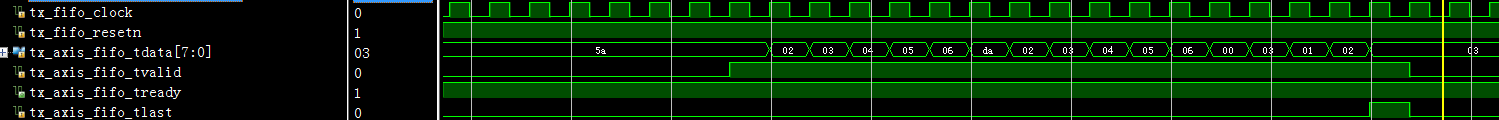

tx_axis_fifo_tdata 8位数据,tx_axis_fifo_tvalid 数据有效指示,tx_axis_fifo_tready MAC发送准备信号,tx_axis_fifo_tlast 数据包尾指示。接下来使用示例工程的testbench查看仿真波形,对用户接口时序有一个直观的认识。官方testbench demo_tb文件中会持续分别以10M 100M 1000M速率向example design RX方向GMII端口发送5个不同数据帧。先来看千兆网波形,在千兆模式下TX时钟为由FPGA提供的125MHz信号gtx_clk_bufg,RX时钟由PHY通过时钟恢复得到125MHz时钟信号。

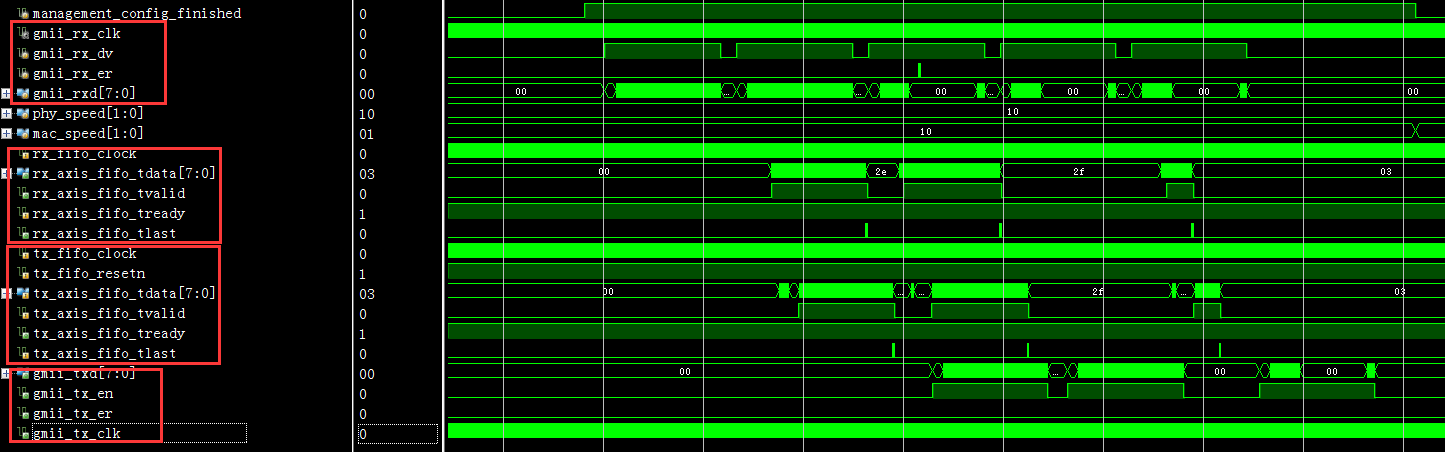

数据的流向为:gmii_rx_xx --> rx_axis_mac_xx --> rx_axis_fifo_xx --> tx_axis_fifo_xx --> tx_axis_mac_xx --> gmii_tx_xx。此时example design中basic_pat_gen_inst模块设置为环回模式,会将MAC接收的数据环回到发送通道。由于第三个帧错误指示信号gmii_rx_er拉高,而第5个帧MAC地址不匹配,因此这两个数据帧被滤除掉。

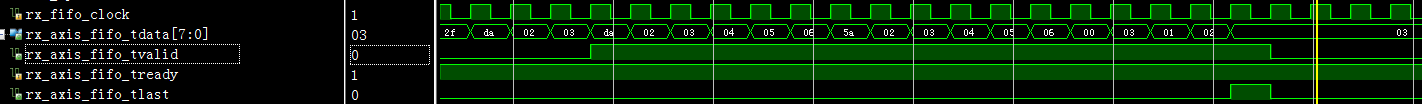

上图看出第三个数据帧带有错误指示信号,FIFO模块才会将其丢弃。第五个数据包MAC地址不符,在MAC核内部被丢弃。以第四个数据包为例观察时序:

包尾指示和数据在MAC核收到FCS并检测完毕后才输出有效。

该帧目的MAC地址是48'hda_02_03_04_05_06 源MAC地址是48'h5a_02_03_04_05_06 长度/类型域是16'h00_03,因此是解释为帧长度为3字节,负荷是01 02 03。环回后目的MAC地址和源MAC地址被basic_pat_gen_inst模块交换,TX方向用户数据包为:

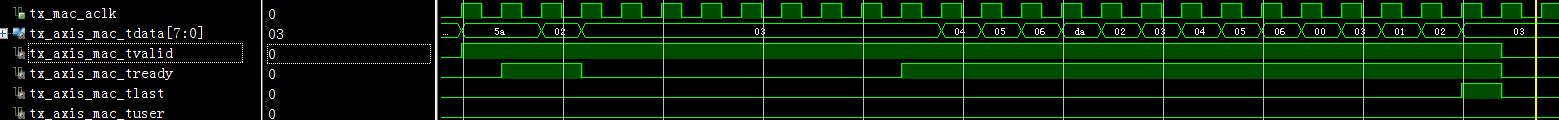

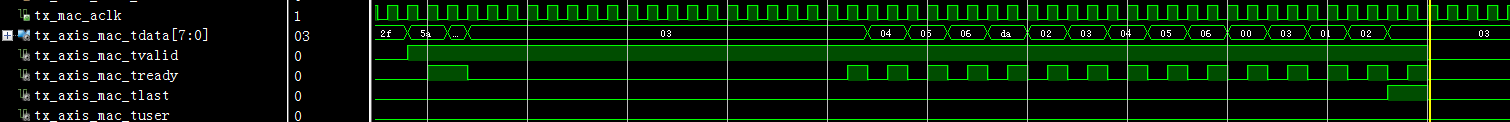

我们看下MAC核TX方向实际的用户接口时序,FIFO模块屏蔽了用户侧与MAC核之间的握手应答机制,缓存至少一个数据帧即开始数据传输,从而简化了接口时序。

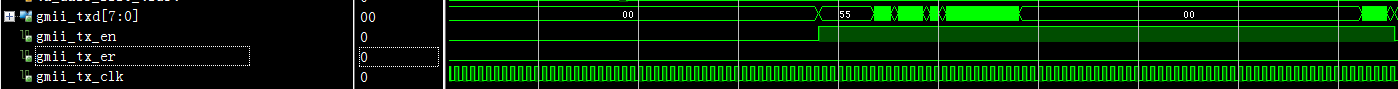

当数据发送到物理层接口,由于数据包小于最小长度,因此发送到gmii接口上再次被填充至最小帧长。此外添加上前导码和校验和。

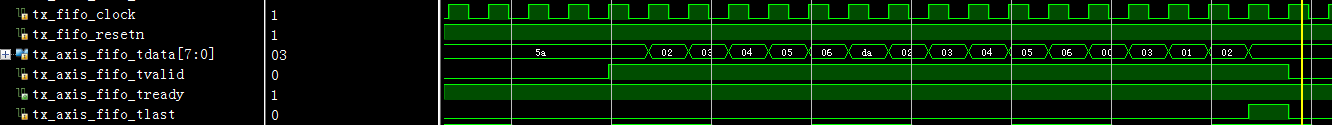

再来看看百兆网,速率为100M时TX和RX方向时钟信号均由PHY芯片提供。第四数据帧TX方向用户接口波形:

FIFO提供的用户侧接口时序上与千兆网没有差别,时钟频率是125MHz,位宽依然是8bit,那么又是如何实现百兆速率的呢?

MAC核用户接口时钟为25MHz,位宽为8bit,MAC核提供的tready信号每两周期拉高一周期,速率为25M*8/2 = 100M,因此100M速率是通过tready信号限流实现的。综上,对100M和1000M速率下全双工以太网概念和帧结构、MAC IP核配置以及核心用户接口时序功能均进行了阐述,本人也在学习中,希望对大家有帮助。

浅析Xilinx 三速以太网MAC IP核的更多相关文章

- 使用FDATOOL生成xilinx中FIR滤波器IP核的系数

1.在MATLAB命令窗口输入fdatool后回车,打开“Filter Designer & Analysis Tool”工具界面: 2.点击左下角的Set quantization para ...

- 转:基于 xilinx vivado 的PCIE ip核设置与例程代码详解

连接:https://blog.csdn.net/u014586651/article/details/103826967#comments

- FPGA设计千兆以太网MAC(2)——以太网协议及设计规划

上篇该系列博文中通过MDIO接口实现了PHY芯片的状态检测,验证其已处于1000M 全双工工作模式.在设计MAC逻辑之前,要先清楚MAC与PHY之间的接口以及以太网协议细节,这样才能保证网络的兼容性. ...

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- Altera三速以太网IP核使用(下篇)--- 百兆网接口设计与使用

MAC IP核的主要作用是:实现数据链路层协议,分为TX方向与RX方向,TX方向实现的是在原包文的前面加上7个55和1个D5,RX方向则相反.在使用这个 MAC IP核之前,首先确认下自己使用的网卡是 ...

- 【重新发布,代码开源】FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片

原创博客,转载请注明出处:[重新发布,代码开源]FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片 - 没落骑士 - 博客园 https://www.cnblogs.com/m ...

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

随机推荐

- ehcachexml文件解释

怎么修改默认配置

- [国嵌攻略][157][SPI总线介绍]

SPI总线架构 SPI(serial peripheral interface)串行外设接口,是一种高速,全双工,同步的通信总线.采用主从模式(master slave)架构,支持多个slave,一般 ...

- 同一台电脑使用 gitlab 和 github 配置

Git 客户端与服务器端的通信支持多种协议,ssh 最常用.ssh的公钥登录流程,用户将自己的公钥存储在远程主机,登录时,远程主机会向用户发送一条消息,用户用自己的私钥加密后,再发给服务器.远程主机用 ...

- centos利用yum安装卸载软件常用命令

来自:http://tech.v01.cn/Linuxchangjianwenti/changyongruanjiananzhuangyucao/2012/0119/70.html 一.使用yum安装 ...

- iOS enum 定义与使用

枚举其实很重要,特别是在应用开发初期,服务器端数据格式需要更改得情况下,枚举和宏都能是程序简洁,并且改动小. 网上有个人写的言简意赅,适合初学 转自:http://blog.csdn.net/ysy4 ...

- MyCat 启蒙:分布式系统的数据库架构演变

文章首发于[博客园-陈树义],点击跳转到原文<MyCat 启蒙:分布式系统的数据库架构演变> 单数据库架构 一个项目在初期的时候,为了尽可能快地验证市场,其对业务系统的最大要求是快速实现. ...

- Python---socket库

为方便以后查询和学习,特从常用库函数和示例来总结socket库 1. 术语 family:AF_INET socktype:SOCK_STREAM或SOCK_DGRAM protocol:IPPROT ...

- sqlserver存储过程及mybatis调用——待续

创建带输入参数存储过程 use yanantestgoif exists (select * from sys.objects where name='yanan')drop procedure ya ...

- java8大基本数据类型

基本类型 字节数 位数 最大值 最小值 byte 1byte 8bit 2^7 - 1 -2^7 short 2byte 16bit 2^15 - 1 -2^15 int 4byte 32bit 2^ ...

- RequestParam\@ResponseBody

为什么不写 RequestParam 也能拿到参数 三种写法,test(String name), test(@RequestParam String name), test(@RequestPara ...