bram_to_vid

Entity: bram_to_vid

- File: bram_to_vid.v

Diagram

Description

Company: Fpga Publish

Engineer: FP

Revision: 0.01

Revision 0.01 - File Created

Generics

| Generic name | Type | Value | Description |

|---|---|---|---|

| MD_SIM_ABLE | 0 | mode in sim mode enable | |

| NB_BRAM_DLY | 2 | BRAM read delay | |

| WD_BRAM_DAT | 8 | width of bram data | |

| WD_BRAM_ADR | 16 | width of bram address | |

| WD_BRAM_WEN | 1 | width of bram write en | |

| MD_VGA_PARA | "1280_720" | vga mode, 640_480/800_600/1280_720/1920_1080/1024_600 | |

| WD_VID_DATA | 24 | RGB data | |

| WD_VID_INFO | 12 | vid info width | |

| WD_ERR_INFO | 4 | width of error info |

Ports

| Port name | Direction | Type | Description |

|---|---|---|---|

| i_sys_clk | input | in system clock | |

| i_sys_resetn | input | in system reset_n | |

| i_fram_start_trig | input | frame start and VSYNC high | |

| i_bram_full_trig | input | bram write full and allow read | |

| o_bram_empt_trig | output | bram read empty and req write data | |

| m_err_bram_info1 | output | [WD_ERR_INFO-1:0] | [0]: [1]: |

| bram_master | out | Virtual bus | --read data |

| vid_master | out | Virtual bus | --write RGB data |

Virtual Buses

bram_master

| Port name | Direction | Type | Description |

|---|---|---|---|

| m_bram_rd_addr | output | [WD_BRAM_ADR-1:0] | bram address |

| m_bram_rd_clk | output | bram clock | |

| m_bram_rd_din | output | [WD_BRAM_DAT-1:0] | bram data in |

| m_bram_rd_dout | input | [WD_BRAM_DAT-1:0] | bram data out |

| m_bram_rd_en | output | bram enable | |

| m_bram_rd_rst | output | bram reset high | |

| m_bram_rd_we | output | [WD_BRAM_WEN-1:0] | bram write enable |

vid_master

| Port name | Direction | Type | Description |

|---|---|---|---|

| m_vid_wr_pdata | output | [WD_VID_DATA-1:0] | |

| m_vid_wr_phsync | output | hori sync | |

| m_vid_wr_pvsync | output | vert sync | |

| m_vid_wr_pvde | output | video info |

Signals

| Name | Type | Description |

|---|---|---|

| r_vid_wr_pdata = 0 | reg [WD_VID_DATA-1:0] | RGB data output |

| r_vid_wr_phsync = 0 | reg | hori sync |

| r_vid_wr_pvsync = 0 | reg | vert sync |

| r_vid_wr_pvde = 0 | reg | video info |

| r_vid_wr_hcunt = 0 | reg [WD_VID_INFO-1:0] | vid write hsync count |

| r_vid_wr_vcunt = 0 | reg [WD_VID_INFO-1:0] | vid write vsync count |

| r_bram_rd_addr = 0 | reg [WD_BRAM_ADR-1:0] | bram address |

| r_bram_rd_din = 0 | reg [WD_BRAM_DAT-1:0] | bram data in |

| r_bram_rd_en = 0 | reg | bram enable |

| r_bram_rd_rst = 0 | reg | bram reset high |

| r_bram_rd_we = 0 | reg [WD_BRAM_WEN-1:0] | bram write enable |

| r_bram_empt_trig = 0 | reg | frame sync |

Constants

| Name | Type | Value | Description |

|---|---|---|---|

| H_FRONT | MD_VGA | hsync front | |

| H_SYNC | MD_VGA | hsync time | |

| H_BACK | MD_VGA | hsync back time | |

| H_DISP | MD_VGA_ | hsync disp | |

| H_TOTAL | MD_VGA_ | hsync total time | |

| V_FRONT | MD_VGA | vsync front | |

| V_SYNC | MD_VG | vsync time | |

| V_BACK | MD_VGA | vsync back time | |

| V_DISP | MD_VGA_ | vsync disp | |

| V_TOTAL | MD_VGA_ | vsync total time |

Processes

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

- Description

vid interface

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

- Description

BRAM interface

- unnamed: ( @(posedge i_sys_clk) )

- Type: always

- Description

frame sync

/*

code

*/

// *******************************************************************************

//!Company: Fpga Publish

//!

//!Engineer: FP

//!

//

// Create Date: 2024/01/20 13:03:28

// Design Name:

// Module Name: bram_to_vid

// Project Name:

// Target Devices: ZYNQ7010 | XCZU2CG | Kintex7

// Tool Versions: 2021.1 || 2022.2

// Description:

// *

// Dependencies:

// *

//!-----------------

//!Revision: 0.01

//!

//!Revision 0.01 - File Created

//!

// Additional Comments:

//

// *******************************************************************************

`timescale 1ns / 1ps

module bram_to_vid #(

//sim mode

parameter MD_SIM_ABLE = 0,//!mode in sim mode enable

//bram bus

parameter NB_BRAM_DLY = 2, //! BRAM read delay

parameter WD_BRAM_DAT = 8, //! width of bram data

parameter WD_BRAM_ADR = 16, //! width of bram address

parameter WD_BRAM_WEN = 1 , //! width of bram write en

//vid bus

parameter MD_VGA_PARA = "1280_720", //! vga mode, 640_480/800_600/1280_720/1920_1080/1024_600

parameter WD_VID_DATA = 24, //! RGB data

parameter WD_VID_INFO = 12, //! vid info width

//error info

parameter WD_ERR_INFO = 4 //!width of error info

)(

//sy stem signals

input i_sys_clk , //!in system clock

input i_sys_resetn, //!in system reset_n

//data full trig

input i_fram_start_trig, //! frame start and VSYNC high

input i_bram_full_trig, //! bram write full and allow read

output o_bram_empt_trig, //! bram read empty and req write data

//! @virtualbus bram_master @dir out --read data

output [WD_BRAM_ADR-1:0] m_bram_rd_addr, //! bram address

output m_bram_rd_clk , //! bram clock

output [WD_BRAM_DAT-1:0] m_bram_rd_din , //! bram data in

input [WD_BRAM_DAT-1:0] m_bram_rd_dout, //! bram data out

output m_bram_rd_en , //! bram enable

output m_bram_rd_rst , //! bram reset high

output [WD_BRAM_WEN-1:0] m_bram_rd_we , //! bram write enable

//! @end

//! @virtualbus vid_master @dir out --write RGB data

output [WD_VID_DATA-1:0] m_vid_wr_pdata , //! RGB data output

output m_vid_wr_phsync, //! hori sync

output m_vid_wr_pvsync, //! vert sync

output m_vid_wr_pvde , //! video info

//! @end

//![0]:

//![1]:

//error info feedback

output [WD_ERR_INFO-1:0] m_err_bram_info1 //!master of error info

);

//========================================================

//function to math and logic

//========================================================

//localparam to converation and calculate

localparam H_FRONT = MD_VGA_PARA == "640_480" ? 12'd16 : //! hsync front

MD_VGA_PARA == "800_600" ? 12'd40 :

MD_VGA_PARA == "1280_720" ? 12'd110 :

MD_VGA_PARA == "1920_1080" ? 12'd88 :

MD_VGA_PARA == "1024_600" ? 12'd160 :

12'd16 ;

localparam H_SYNC = MD_VGA_PARA == "640_480" ? 12'd96 : //! hsync time

MD_VGA_PARA == "800_600" ? 12'd128 :

MD_VGA_PARA == "1280_720" ? 12'd40 :

MD_VGA_PARA == "1920_1080" ? 12'd44 :

MD_VGA_PARA == "1024_600" ? 12'd40 :

12'd96 ;

localparam H_BACK = MD_VGA_PARA == "640_480" ? 12'd48 : //! hsync back time

MD_VGA_PARA == "800_600" ? 12'd88 :

MD_VGA_PARA == "1280_720" ? 12'd220 :

MD_VGA_PARA == "1920_1080" ? 12'd148 :

MD_VGA_PARA == "1024_600" ? 12'd120 :

12'd48 ;

localparam H_DISP = MD_VGA_PARA == "640_480" ? 12'd640 : //! hsync disp

MD_VGA_PARA == "800_600" ? 12'd800 :

MD_VGA_PARA == "1280_720" ? 12'd1280:

MD_VGA_PARA == "1920_1080" ? 12'd1920:

MD_VGA_PARA == "1024_600" ? 12'd1024:

12'd640;

localparam H_TOTAL = MD_VGA_PARA == "640_480" ? 12'd800 : //! hsync total time

MD_VGA_PARA == "800_600" ? 12'd1056:

MD_VGA_PARA == "1280_720" ? 12'd1650:

MD_VGA_PARA == "1920_1080" ? 12'd2200:

MD_VGA_PARA == "1024_600" ? 12'd1344:

12'd800;

localparam V_FRONT = MD_VGA_PARA == "640_480" ? 12'd10 : //! vsync front

MD_VGA_PARA == "800_600" ? 12'd1 :

MD_VGA_PARA == "1280_720" ? 12'd5 :

MD_VGA_PARA == "1920_1080" ? 12'd4 :

MD_VGA_PARA == "1024_600" ? 12'd12 :

12'd10 ;

localparam V_SYNC = MD_VGA_PARA == "640_480" ? 12'd2 : //! vsync time

MD_VGA_PARA == "800_600" ? 12'd4 :

MD_VGA_PARA == "1280_720" ? 12'd5 :

MD_VGA_PARA == "1920_1080" ? 12'd5 :

MD_VGA_PARA == "1024_600" ? 12'd3 :

12'd2 ;

localparam V_BACK = MD_VGA_PARA == "640_480" ? 12'd33 : //! vsync back time

MD_VGA_PARA == "800_600" ? 12'd23 :

MD_VGA_PARA == "1280_720" ? 12'd20 :

MD_VGA_PARA == "1920_1080" ? 12'd36 :

MD_VGA_PARA == "1024_600" ? 12'd20 :

12'd33 ;

localparam V_DISP = MD_VGA_PARA == "640_480" ? 12'd480 : //! vsync disp

MD_VGA_PARA == "800_600" ? 12'd600 :

MD_VGA_PARA == "1280_720" ? 12'd720 :

MD_VGA_PARA == "1920_1080" ? 12'd1080:

MD_VGA_PARA == "1024_600" ? 12'd600 :

12'd480;

localparam V_TOTAL = MD_VGA_PARA == "640_480" ? 12'd525 : //! vsync total time

MD_VGA_PARA == "800_600" ? 12'd628 :

MD_VGA_PARA == "1280_720" ? 12'd750 :

MD_VGA_PARA == "1920_1080" ? 12'd1125:

MD_VGA_PARA == "1024_600" ? 12'd635 :

12'd525;

//========================================================

//register and wire to time sequence and combine

// ----------------------------------------------------------

//! vid interface

reg [WD_VID_DATA-1:0] r_vid_wr_pdata = 0; //! RGB data output

reg r_vid_wr_phsync = 0; //! hori sync

reg r_vid_wr_pvsync = 0; //! vert sync

reg r_vid_wr_pvde = 0; //! video info

assign m_vid_wr_pdata = r_vid_wr_pdata ;

assign m_vid_wr_phsync = r_vid_wr_phsync ;

assign m_vid_wr_pvsync = r_vid_wr_pvsync ;

assign m_vid_wr_pvde = r_vid_wr_pvde ;

//write count

reg r_frame_wr_flag = 0; //! only when frame start then send data

reg [WD_VID_INFO-1:0] r_vid_wr_hcunt = 0; //! vid write hsync count

reg [WD_VID_INFO-1:0] r_vid_wr_vcunt = 0; //! vid write vsync count

// ----------------------------------------------------------

//! BRAM interface

reg [WD_BRAM_ADR-1:0] r_bram_rd_addr = 0;//! bram address

// reg r_bram_rd_clk ; //! bram clock

reg [WD_BRAM_DAT-1:0] r_bram_rd_din = 0;//! bram data in

// reg [WD_BRAM_DAT-1:0] r_bram_rd_dout; //! bram data out

reg r_bram_rd_en = 0;//! bram enable

reg r_bram_rd_rst = 0;//! bram reset high

reg [WD_BRAM_WEN-1:0] r_bram_rd_we = 0;//! bram write enable

assign m_bram_rd_addr = r_bram_rd_addr;

assign m_bram_rd_clk = i_sys_clk;

assign m_bram_rd_din = r_bram_rd_din;

assign m_bram_rd_en = r_bram_rd_en;

assign m_bram_rd_rst = r_bram_rd_rst;

assign m_bram_rd_we = r_bram_rd_we;

// ----------------------------------------------------------

//! frame sync

reg r_bram_empt_trig = 0;

assign o_bram_empt_trig = r_bram_empt_trig;

//========================================================

//always and assign to drive logic and connect

// ----------------------------------------------------------

//! vid interface

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_frame_wr_flag <= 1'b0; //

end

else if(i_fram_start_trig) //

begin

r_frame_wr_flag <= 1'b1;//

end

else if(r_vid_wr_hcunt >= H_TOTAL - 1'b1

&& r_vid_wr_vcunt >= V_TOTAL - 1'b1)

begin

r_frame_wr_flag <= 1'b0;

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_hcunt <= 1'b0; //

end

else if(!r_frame_wr_flag)

begin

r_vid_wr_hcunt <= 1'b0;

end

else if(r_vid_wr_hcunt >= H_TOTAL - 1'b1) //

begin

r_vid_wr_hcunt <= 1'b0; //

end

else

begin

r_vid_wr_hcunt <= r_vid_wr_hcunt + 1'b1;

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_vcunt <= 1'b0; //

end

else if(!r_frame_wr_flag) //frame sync

begin

r_vid_wr_vcunt <= 1'b0;

end

else if(r_vid_wr_hcunt >= H_TOTAL - 1'b1) //

begin

if(r_vid_wr_vcunt >= V_TOTAL - 1'b1) //

begin

r_vid_wr_vcunt <= 1'b0;

end

else

begin

r_vid_wr_vcunt <= r_vid_wr_vcunt + 1'b1;

end

end

end

//vid signal

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_pvde <= 1'b0; //

end

else if(r_vid_wr_hcunt >= H_SYNC + H_BACK - 1'b1

&& r_vid_wr_hcunt < H_SYNC + H_BACK + H_DISP - 1'b1

&& r_vid_wr_vcunt >= V_SYNC + V_BACK - 1'b1

&& r_vid_wr_vcunt < V_SYNC + V_BACK + V_DISP - 1'b1) //

begin

r_vid_wr_pvde <= 1'b1; //

end

else

begin

r_vid_wr_pvde <= 1'b0;

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_pvsync <= 1'b0; //

end

else if(r_vid_wr_hcunt >= H_TOTAL - 1'b1) //

begin

if(r_vid_wr_vcunt >= V_SYNC - 1'b1

&& r_vid_wr_vcunt < V_TOTAL - 1'b1) //when count last then set it low

begin

r_vid_wr_pvsync <= 1'b1;

end

else

begin

r_vid_wr_pvsync <= 1'b0; //

end

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_phsync <= 1'b0; //

end

else if(r_vid_wr_hcunt <= V_SYNC - 1'b1 - 1'b1) //prepare vsync valid

begin

r_vid_wr_phsync <= 1'b0; //

end

else

begin

r_vid_wr_phsync <= 1'b1;

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_vid_wr_pdata <= 1'b0; //

end

else if(1) //

begin

r_vid_wr_pdata <= {3{m_bram_rd_dout}}; //

end

end

// ----------------------------------------------------------

//! BRAM interface

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_bram_rd_en <= 1'b0; //

end

else if(1) //

begin

r_bram_rd_en <= r_vid_wr_phsync;//

end

end

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_bram_rd_addr <= 1'b0;//

end

else if(r_vid_wr_hcunt == 0)

begin

r_bram_rd_addr <= 1'b0;

end

else if(r_vid_wr_hcunt >= H_SYNC + H_BACK - 1 - NB_BRAM_DLY) //bram write addr add

begin

r_bram_rd_addr <= r_bram_rd_addr + 1'b1; //

end

end

// ----------------------------------------------------------

//! frame sync

always@(posedge i_sys_clk)

begin

if(!i_sys_resetn) //system reset

begin

r_bram_empt_trig <= 1'b0; //

end

else if(r_vid_wr_hcunt == H_SYNC + H_BACK + H_DISP - 2'd2

&& r_vid_wr_pvde) //video enable

begin

r_bram_empt_trig <= 1'b1; //

end

else

begin

r_bram_empt_trig <= 1'b0;

end

end

//========================================================

//module and task to build part of system

//========================================================

//expand and plug-in part with version

//========================================================

//ila and vio to debug and monitor

endmodule

/* end verilog

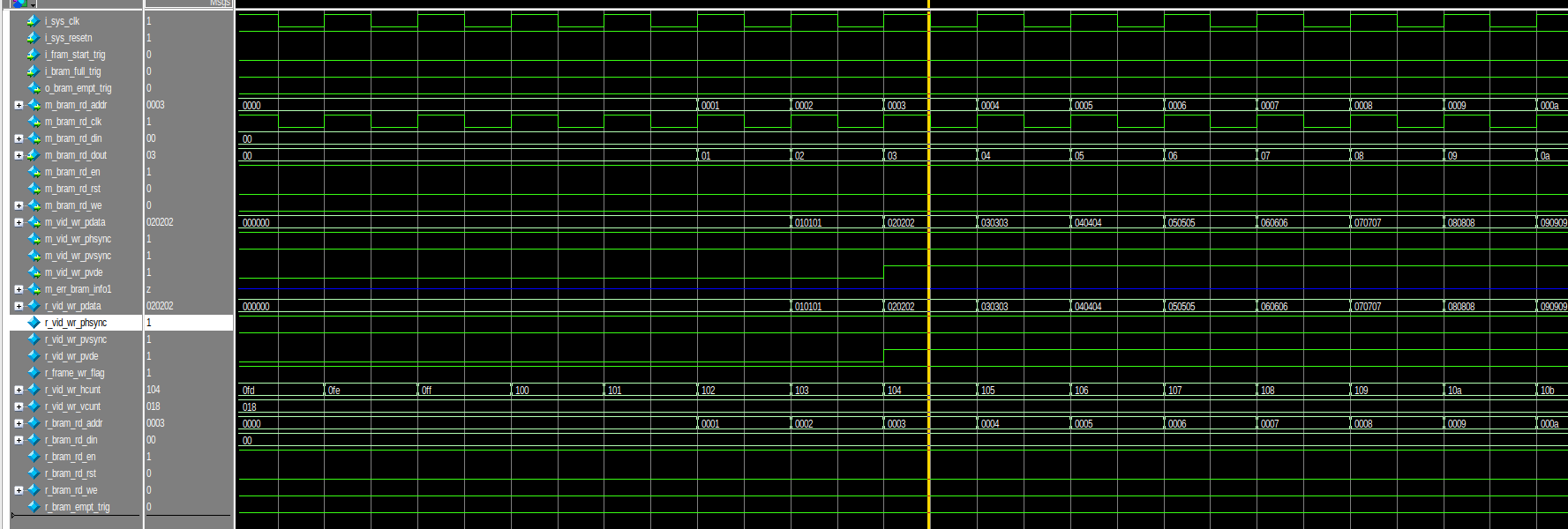

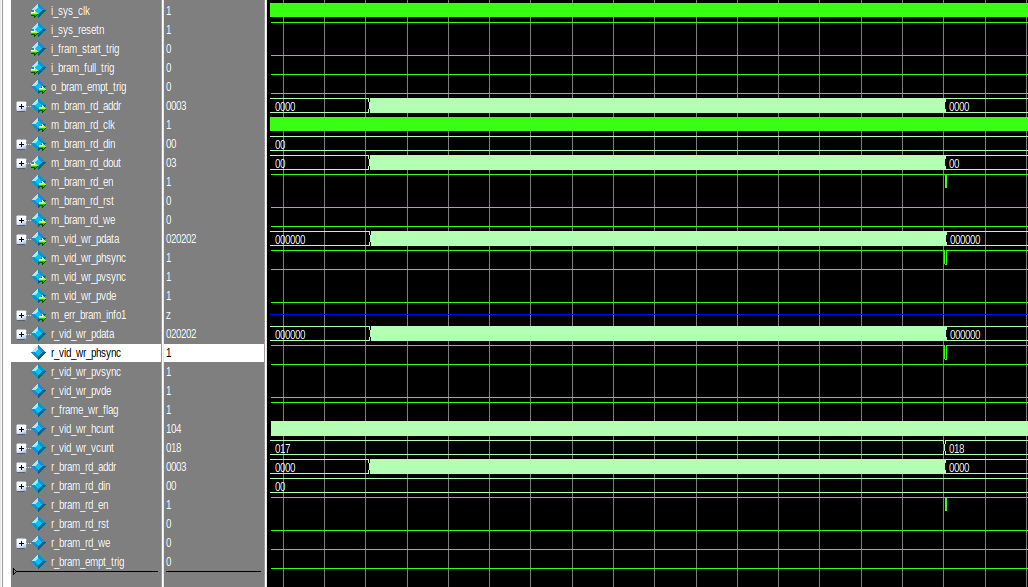

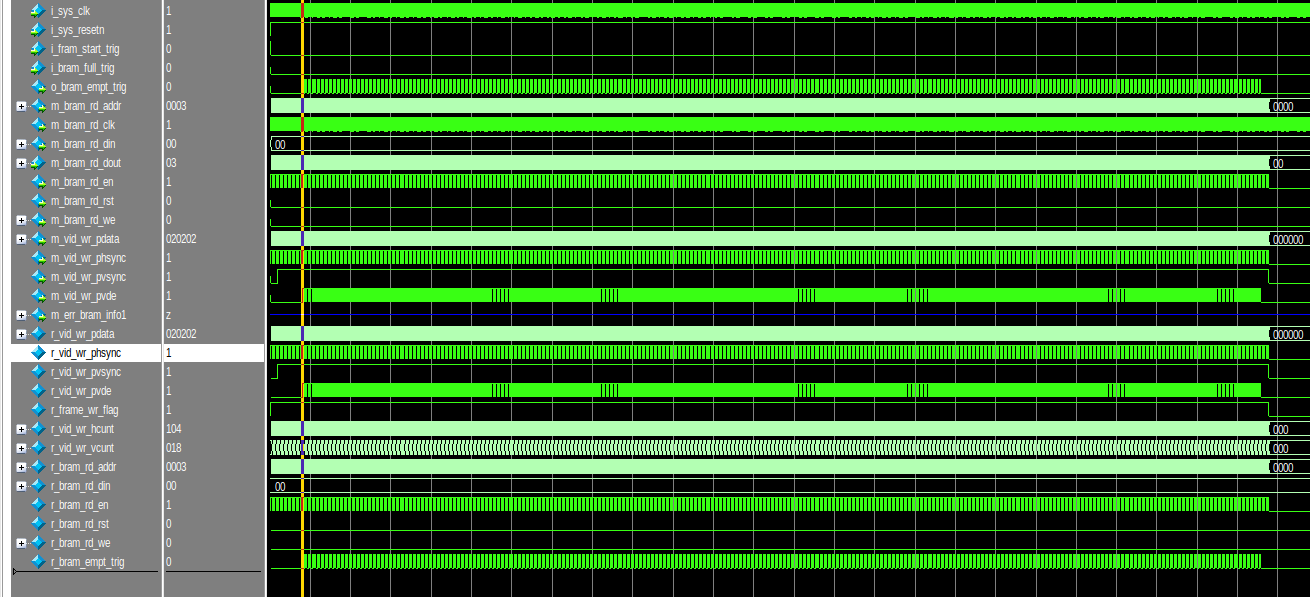

## logic

sim

- BRAM read delay

- video horizontal data

- video vertical data

*/

随机推荐

- SpringBoot 2.6 和 JUnit 5 的测试用例注解和排序方式

JUnit5 的测试注解 在JUnit5中, 不再使用 @RunWith 注解, 改为使用 @ExtendWith(SpringExtension.class) @ExtendWith(SpringE ...

- Spring源码之spring事务

目录 Spring事务 事务自定义标签 自定义标签 解析标签 bean 的初始化 InfrastructureAdvisorAutoProxyCreator 获取增强方法 获取所有增强中内适用于当前方 ...

- sklearn学习笔记之线性回归

AI时代扑面而来,在大众面对ChatGPT和Sora发出无数惊叹号的时候,我决定不再只当一个AI时代的API调用者,而是去学习机器学习技术本身. 刚好公司也要往人工智能方向发展的计划,于是我开始从基础 ...

- Docker进阶之02-Swarm集群入门实践

Docker集群概述 Docker集群有2种方案: 1.在Docker Engine 1.12之前的集群模式被称为经典集群,这是通过API代理系统实现的集群,目前已经不再维护. 2.自Docker E ...

- 记录一个错误:Traceback (most recent call last): from pip._internal.cli.main import main ImportError: No module named pip._internal.cli.main

问题描述 在安装yaml时得到报错如下 root@ag-virtual-machine:/home/ag/test_script# pip install pyyaml Traceback (most ...

- 第一百零九篇:基本数据类型(String类型)

好家伙, 本篇内容为<JS高级程序设计>第三章学习笔记 1.String类型 字符串类型是最常用的几个基本类型之一 字符串可以使用双引号,单引号以及反引号(键盘左Tab上面那个)标示 ...

- Redis哨兵(sentinel)

目录 前言 原理 架构图 下载 命令 配置 启动 查看 Sentinel(哨兵)配置 常用命令 Q&A Redis主从配置异常解决:Error condition on socket for ...

- 【Azure Developer】使用MSAL4J 与 ADAL4J 的SDK时候,遇见了类型冲突问题 "java.util.Collections$SingletonList cannot be cast to java.lang.String"

问题描述 在博文 "[Azure Developer]使用 Powershell az account get-access-token 命令获取Access Token (使用用户名+密码 ...

- 用 NetworkX + Gephi + Nebula Graph 分析<权力的游戏>人物关系(上篇)

我们都知道<权利的游戏>在全世界都很多忠实的粉丝,除去你永远不知道剧情下一秒谁会挂这种意外"惊喜",当中复杂交错的人物关系也是它火爆的原因之一,而本文介绍如何通过 Ne ...

- Java 客户信息管理软件 (面向对象 封装 总结)

1 package com.bytezero.cim.bean; 2 3 /** 4 * 5 * @Description Customer为实体对象,用来封装客户信息 6 * @author Byt ...