verilog 代码分析与仿真

verilog 代码分析与仿真

注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值

边沿检测

- module signal_test(

- input wire cmos_pclk_i,

- input wire cmos_vsync_i

- );

- // 上升沿捕获

- reg [:] vsync_d;

- wire vsync_start;

- wire vsync_end;

- always @(posedge cmos_pclk_i)

- begin

- vsync_d <= {vsync_d[], cmos_vsync_i};

- end

- assign vsync_start = vsync_d[] && (!vsync_d[]);

- assign vsync_end = (!vsync_d[]) && vsync_d[];

- endmodule

- /*

- add_force {/signal_test/cmos_pclk_i} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

- add_force {/signal_test/cmos_vsync_i} -radix hex {1 0ns} {0 300ns} {1 700ns}

- */

仿真结果:

时钟二分频的巧用

- //在一定区域内,将时钟cmos_pclk_i 进行二分频

- reg byte_flag = ;

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- byte_flag <= ;

- else if(cmos_href_i) //控制信号,固定区域

- byte_flag <= ~byte_flag;

- else

- byte_flag <= ;

- end

- //将byte_flag 延时一拍,从仿真图中才可以看出此处的用意

- reg byte_flag_r0 = ;

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- byte_flag_r0 <= ;

- else

- byte_flag_r0 <= byte_flag;

- end

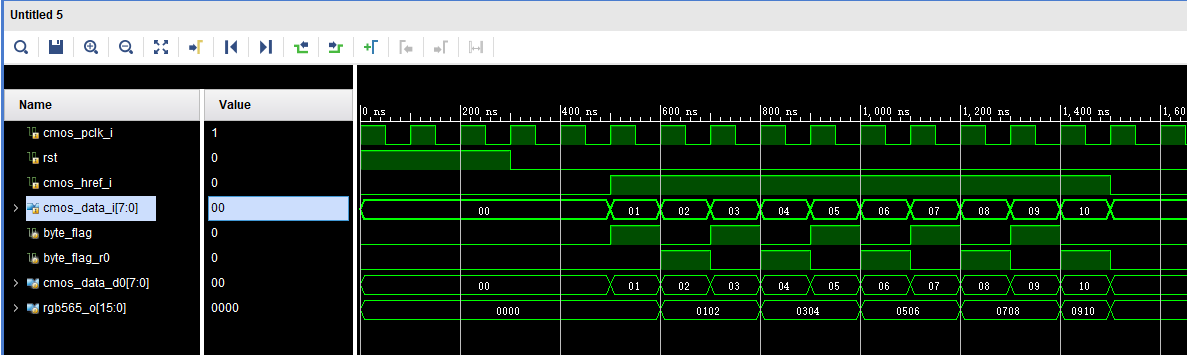

仿真结果:

数据采集与数据融合

注意rgb565信号的生成

- //接收摄像头的数据,当href为高电平时,采集数据,当为低电平时,用0填充

- reg [:] cmos_data_d0 = ;

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- cmos_data_d0 <= 'd0;

- else if(cmos_href_i)

- cmos_data_d0 <= cmos_data_i; //MSB -> LSB

- else if(~cmos_href_i)

- cmos_data_d0 <= 'd0;

- end

- reg [:] rgb565_o = ;

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- rgb565_o <= 'd0;

- //当href为高电平,byte_flag 为高时候,对rgb565数据进行拼装

- else if(cmos_href_i & byte_flag)

- rgb565_o <= {cmos_data_d0,cmos_data_i}; //MSB -> LSB

- else if(~cmos_href_i)

- rgb565_o <= 'd0;

- end

仿真结果:

成功的将两个数融合在一起,一个是寄存器里面保存的数据,一个是实时的输入数据。

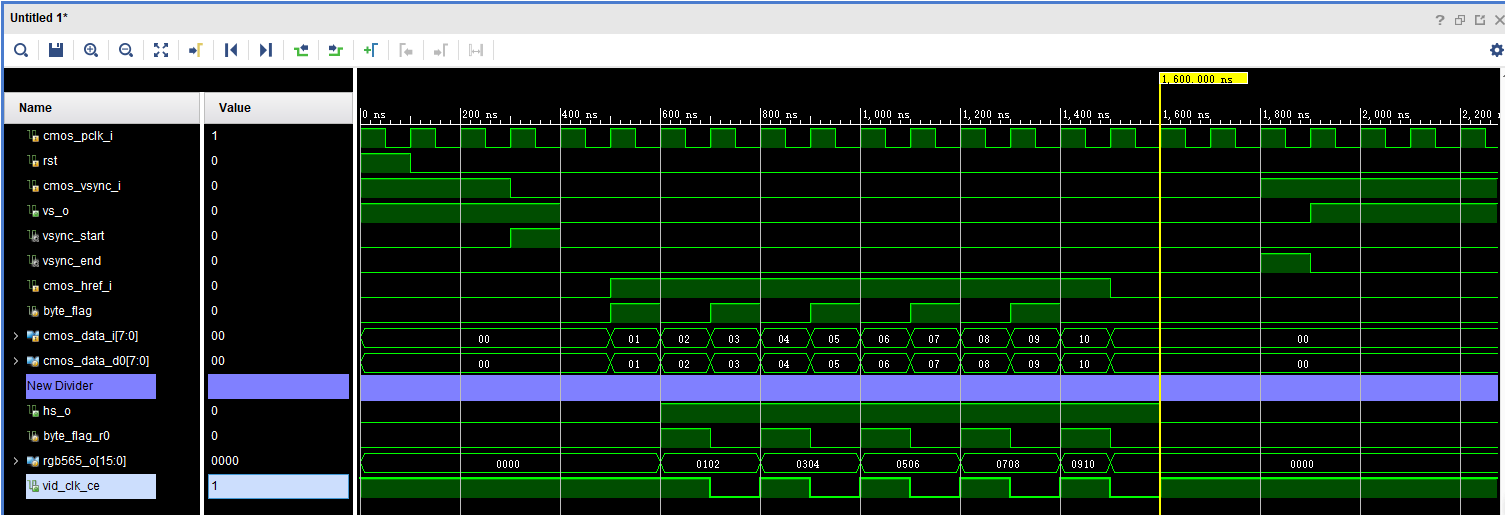

关于像素的输出使能信号的生成

- assign vs_o = vsync_d[];

- assign hs_o = href_d[];

- assign vid_clk_ce = (byte_flag_r0&hs_o)||(!hs_o);

仿真结果:

当hs_o 为高时,摄像头输出有效数据,2个2个一起,每当数据进行更新时,ce信号产生,当输出的是消隐区数据的时候,ce信号一直使能。

- module signal_test_1(

- input wire cmos_pclk_i,

- input wire rst,

- input wire [:]cmos_data_i,

- input wire cmos_href_i,

- input wire cmos_vsync_i,

- output wire hs_o,

- output wire vs_o,

- output wire vid_clk_ce

- );

- /*parameter[5:0]CMOS_FRAME_WAITCNT = 4'd15;*/

- // 对行场信号进行边沿检测处理

- reg[:]vsync_d = 'b11;

- reg[:]href_d = 'b00;

- wire vsync_start;

- wire vsync_end;

- //vs signal deal with.

- always@(posedge cmos_pclk_i)

- begin

- vsync_d <= {vsync_d[],cmos_vsync_i};

- href_d <= {href_d[],cmos_href_i};

- end

- assign vsync_start = vsync_d[]&(!vsync_d[]); //捕捉vsync信号的下降沿

- assign vsync_end = (!vsync_d[])&vsync_d[]; //捕捉vsync信号的上升沿

- /*reg[6:0]cmos_fps = 0;

- //frame count.

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- begin

- cmos_fps <= 7'd0;

- end

- else if(vsync_start) //每当一场开始的时候,计数器加一,难道是一帧只有一场?

- begin

- cmos_fps <= cmos_fps + 7'd1;

- end

- //计数到了CMOS_FRAME_WAITCNT时,就保持这个数值不变(15)

- else if(cmos_fps >= CMOS_FRAME_WAITCNT)

- begin

- cmos_fps <= CMOS_FRAME_WAITCNT;

- end

- end*/

- //在一定区域内,将时钟cmos_pclk_i 进行二分频

- reg byte_flag = ;

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- byte_flag <= ;

- else if(cmos_href_i) //控制信号,固定区域

- byte_flag <= ~byte_flag;

- else

- byte_flag <= ;

- end

- //将byte_flag 延时一拍,从仿真图中才可以看出此处的用意

- reg byte_flag_r0 = ;

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- byte_flag_r0 <= ;

- else

- byte_flag_r0 <= byte_flag;

- end

- //接收摄像头的数据,当href为高电平时,采集数据,当为低电平时,用0填充

- reg [:] cmos_data_d0 = ;

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- cmos_data_d0 <= 'd0;

- else if(cmos_href_i)

- cmos_data_d0 <= cmos_data_i; //MSB -> LSB

- else if(~cmos_href_i)

- cmos_data_d0 <= 'd0;

- end

- reg [:] rgb565_o = ;

- always@(posedge cmos_pclk_i)

- begin

- if(rst)

- rgb565_o <= 'd0;

- //当href为高电平,byte_flag 为高时候,对rgb565数据进行拼装

- else if(cmos_href_i & byte_flag)

- rgb565_o <= {cmos_data_d0,cmos_data_i}; //MSB -> LSB

- else if(~cmos_href_i)

- rgb565_o <= 'd0;

- end

- assign vs_o = vsync_d[];

- assign hs_o = href_d[];

- assign vid_clk_ce = (byte_flag_r0&hs_o)||(!hs_o);

- /*

- add_force {/signal_test_1/cmos_pclk_i} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps

- add_force {/signal_test_1/rst} -radix hex {1 0ns} {0 100ns}

- add_force {/signal_test_1/cmos_href_i} -radix hex {0 0ns} {1 500ns} {0 1500ns}

- add_force {/signal_test_1/cmos_data_i} -radix hex {0 0ns} {1 500ns} {2 600ns} {3 700ns} {4 800ns} {5 900ns} {6 1000ns}\

- {7 1100ns} {8 1200ns} {9 1300ns} {10 1400ns} {0 1500ns}

- add_force {/signal_test_1/cmos_vsync_i} -radix hex {1 0ns} {0 300ns} {1 1800ns}

- */

- endmodule

源程序与注释:

- `timescale 1ns / 1ps

- //////////////////////////////////////////////////////////////////////////////////

- // Company:

- // Engineer:

- //

- // Create Date: 2018/05/17 13:22:09

- // Design Name:

- // Module Name: cmos_decode

- // Project Name:

- // Target Devices:

- // Tool Versions:

- // Description:

- //

- // Dependencies:

- //

- // Revision:

- // Revision 0.01 - File Created

- // Additional Comments:

- //

- //////////////////////////////////////////////////////////////////////////////////

- module cmos_decode(

- //system signal.

- input cmos_clk_i, //cmos senseor clock.

- input rst_n_i, //system reset.active low.

- //cmos sensor hardware interface.

- input cmos_pclk_i, //input pixel clock.

- input cmos_href_i, //input pixel hs signal.

- input cmos_vsync_i, //input pixel vs signal.

- input[:]cmos_data_i, //data.

- output cmos_xclk_o, //output clock to cmos sensor.

- //user interface.

- output hs_o, //hs signal.

- output vs_o, //vs signal.

- output reg [:] rgb565_o, //data output

- output vid_clk_ce

- );

- parameter[:]CMOS_FRAME_WAITCNT = 'd15;

- //复位信号延时5个时钟周期

- reg[:] rst_n_reg = 'd0;

- //reset signal deal with.

- always@(posedge cmos_clk_i)

- begin

- rst_n_reg <= {rst_n_reg[:],rst_n_i};

- end

- // 对行场信号进行边沿检测处理

- reg[:]vsync_d;

- reg[:]href_d;

- wire vsync_start;

- wire vsync_end;

- //vs signal deal with.

- always@(posedge cmos_pclk_i)

- begin

- vsync_d <= {vsync_d[],cmos_vsync_i};

- href_d <= {href_d[],cmos_href_i};

- end

- assign vsync_start = vsync_d[]&(!vsync_d[]); //捕捉vsync信号的下降沿

- assign vsync_end = (!vsync_d[])&vsync_d[]; //捕捉vsync信号的上升沿

- reg[:]cmos_fps;

- //frame count.

- always@(posedge cmos_pclk_i)

- begin

- if(!rst_n_reg[])

- begin

- cmos_fps <= 'd0;

- end

- else if(vsync_start) //每当一场开始的时候,计数器加一,难道是一帧只有一场?

- begin

- cmos_fps <= cmos_fps + 'd1;

- end

- //计数到了CMOS_FRAME_WAITCNT时,就保持这个数值不变(15)

- else if(cmos_fps >= CMOS_FRAME_WAITCNT)

- begin

- cmos_fps <= CMOS_FRAME_WAITCNT;

- end

- end

- //wait frames and output enable.

- reg out_en;

- always@(posedge cmos_pclk_i)

- begin

- if(!rst_n_reg[])

- begin

- out_en <= 'b0;

- end

- //当计数器达到CMOS_FRAME_WAITCNT(15)时,产生一个使能信号

- else if(cmos_fps >= CMOS_FRAME_WAITCNT)

- begin

- out_en <= 'b1;

- end

- //没有达到条件时候,保持原信号不变

- else

- begin

- out_en <= out_en;

- end

- end

- //output data 8bit changed into 16bit in rgb565.

- reg [:] cmos_data_d0;

- reg [:]cmos_rgb565_d0;

- reg byte_flag;

- always@(posedge cmos_pclk_i)

- begin

- if(!rst_n_reg[])

- byte_flag <= ;

- //产生一个标志位,每当href为高 电平时,产生跳变

- else if(cmos_href_i)

- byte_flag <= ~byte_flag;

- else

- byte_flag <= ;

- end

- //为什么在这里打一拍

- reg byte_flag_r0;

- always@(posedge cmos_pclk_i)

- begin

- if(!rst_n_reg[])

- byte_flag_r0 <= ;

- else

- byte_flag_r0 <= byte_flag;

- end

- //接收摄像头的数据,当href为高电平时,采集数据,当为低电平时,用0填充

- always@(posedge cmos_pclk_i)

- begin

- if(!rst_n_reg[])

- cmos_data_d0 <= 'd0;

- else if(cmos_href_i)

- cmos_data_d0 <= cmos_data_i; //MSB -> LSB

- else if(~cmos_href_i)

- cmos_data_d0 <= 'd0;

- end

- //重要的来了

- always@(posedge cmos_pclk_i)

- begin

- if(!rst_n_reg[])

- rgb565_o <= 'd0;

- //当href为高电平,byte_flag 为高时候,对rgb565数据进行拼装

- else if(cmos_href_i & byte_flag)

- rgb565_o <= {cmos_data_d0,cmos_data_i}; //MSB -> LSB

- else if(~cmos_href_i)

- rgb565_o <= 'd0;

- end

- assign vid_clk_ce = out_en ? (byte_flag_r0&hs_o)||(!hs_o) : 'b0;

- assign vs_o = out_en ? vsync_d[] : 'b0;

- assign hs_o = out_en ? href_d[] : 'b0;

- assign cmos_xclk_o = cmos_clk_i;

- endmodule

verilog 代码分析与仿真的更多相关文章

- 串口接收端verilog代码分析

串口接收端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- 串口发送端verilog代码分析

串口发送端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- VGA设计(原理说明。Verilog代码实现,仿真结果)

各类显示屏的显示原理大部分是利用人眼的视觉暂留效应.比如之前的数码管显示就是设计每个周期内各个小段按顺序显示,来达到显示一个数字的效果. VGA同理,显示屏在显示时是一个像素一个像素地显示,在人眼看来 ...

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- Verilog代码规范I

Verilog代码规范I "规范"这问题 "规范"这个富含专业气息的词汇(个人感觉),其实规范这种东西,就是大家都约定熟成的东西,一旦你不遵守这个东西,专业人士 ...

- Xilinx Vivado的使用详细介绍(1):创建工程、编写代码、行为仿真

Xilinx Vivado的使用详细介绍(1):创建工程.编写代码.行为仿真 Author:zhangxianhe 新建工程 打开Vivado软件,直接在欢迎界面点击Create New Projec ...

- STM32F103片外运行代码分析

STM32F103片外运行代码分析 STM32F103有三种启动方式: 1.从片内Flash启动: 2.从片内RAM启动: 3.从片内系统存储器启动,内嵌的自举程序,用于串口IAP. 无法直接在片外N ...

- Verilog代码和FPGA硬件的映射关系(一)

代码和硬件之间的映射关系是一个很奇妙的过程,也展现出人类的智慧.单片机内部的硬件结构都是固定的,无法改变,我们通过代码操作着寄存器的读写,来执行各种复杂的任务.FPGA的硬件结构并不像单片机一样是固定 ...

- Verilog代码和FPGA硬件的映射关系(二)

大家可能会有这样的疑问,我们编写的Verilog代码最终会在FPGA上以怎样的映射关系来实现功能呢?我们以一个最简单的组合逻辑与门为例来向大家说明.RTL代码如下所示: //------------- ...

随机推荐

- 无头浏览器phantomJS

selenium: 有头浏览器的代表(selenium+python也可实现静默运行 引入python的一个包,包叫:虚拟屏幕pyvirtualdisplay) PhantomJS : 无头浏览器的代 ...

- 【分布式搜索引擎】Elasticsearch如何部署以及优化查询性能

一.Elasticsearch生产集群如何部署 (1)es生产集群部署5台机器,若每台机器是6核64G的,那么集群总内存是320G (2)假如我们es集群的日增量数据大概是2000万条,每天日增量数据 ...

- Web版记账本开发记录(六)

经过今天的学习和实践,终于把这个web版的记账系统给做出来了, 虽然是很简单的一个系统,但是自己花费的时间也着实不少. 今天将大部分功能都实现了,接下来就是完善和美化, 接下来会对不足的地方进行改善, ...

- 小程序 input 组件内容显示不全(显示的长度不满 input 宽度)问题

问题:小程序的input组件经常用到,但在使用input组件的时候会出现一种现象:明明设置了input的宽度,但是输入的内容显示的长度范围却怎么都不到一整个input组件的宽度,而且后面没显示的地方无 ...

- 漏洞复现——Apache SSI远程命令执行

漏洞原理:当目标服务器开启了SSI与CGI支持,我们就可以上传shtml文件,利用<!--#exec cmd="id" -->语法执行命令. SSI:SSI(服务器端包 ...

- 选择器:first-child与:last-child失效的解决方法

作为还在努力练习的代码小白来说,有时类名或者ID名太多很容易就会搞混,为此,在练习中会想着借用多样的选择器来设置而不是每一个标签都设一个类名(Id名),在此次练习中使用选择器:first-child与 ...

- CloudStack学习-1

环境准备 实验使用的虚拟机配置 Vmware Workstation 虚拟机系统2个 系统版本:centos6.6 x86_64 内存:4GB 网络:两台机器都是nat 磁盘:装完系统后额外添加个50 ...

- Excel中针对IP地址的排序方法

新建一个辅助排序列,用辅助列来扩展,辅助列公式如下: =TRIM(TEXT(LEFT(SUBSTITUTE(A1,".",REPT(" ",99)),100), ...

- 跟随我在oracle学习php(3)

这次讲一下html中的列表和比较重要的表格 列表分为有序和无序,有序列表与无序列表都是块状元素 <ul>(父标签) 定义无序列表.复合标签(由父标签和子标签组成),不单独出现,用<l ...

- 为Linux技术学习推荐看的书籍—《Linux就该这么学》

成长,是一种经历:经历,是一种人生的体验.人生的意义不在于我们拥有了什么,而在于从中我们体悟了什么.在这短短的三年,却在我的人生中弥足珍贵,在脑海中记忆犹新,在这大学三年里,我从一个莽撞少年成长为一名 ...