双口RAM,值得研究

在FPGA设计过程中,使用好双口RAM,也是提高效率的一种方法。

官方将双口RAM分为简单双口RAM和真双口RAM。

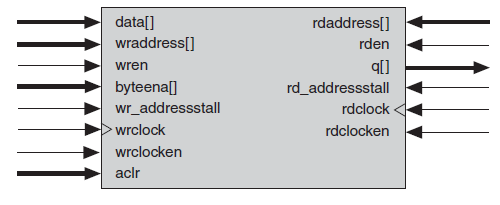

简单双口RAM只有一个写端口,一个读端口。

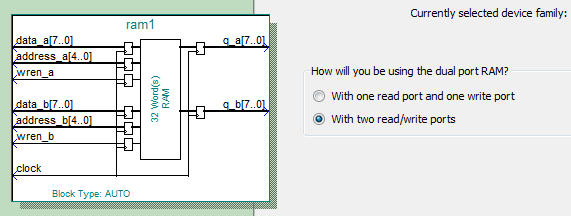

真双口RAM分别有两个写端口和两个读端口。

无论是简单双口RAM还是真双口RAM,在没有读操作的情况下,应将读使能rden信号拉成低电平,节省功耗。

在两种情况下,都应当避免read-during-write,虽然可在软件中进行设置,但是,作为设计者,应当尽量避免此种情况。

对于真双口RAM,还应当避免两个读端口或者两个写端口同时操作同一个地址,RAM中并没有此种冲突解决电路,设计者应该避免这种冲突。

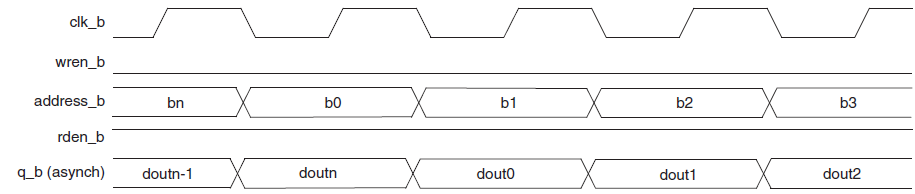

无论是那种双口RAM,读时序图是相同的。

当读使能有效时,数据会在时钟下一个上升沿从Q端输出。

真双口RAM给设计带来很多便利。在高速存储中,需要对连续的数据同时处理,使用简单双口RAM只能读取一个数据,而使用真双口RAM可以同时读取两个数据,这样明显提高读取速度以及处理速度。

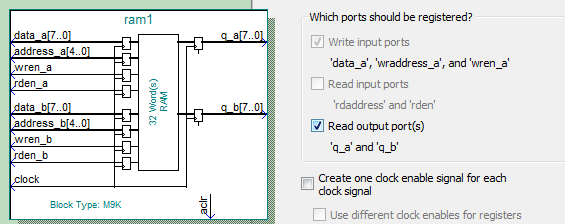

调用真双口RAM,如图设置。

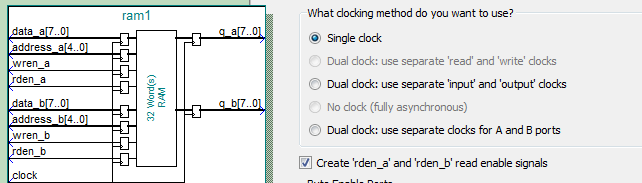

这里可以设置时钟方案,而读使能rden并非必须信号。当使用rden信号时,此信号高电平有效,当不使用rden信号时,给定地址,下一个脉冲数据从q端口送出。

这里的设置非常重要,当选中read output ports时,q端会增加一级寄存器。虽然这样增加流水线能够提高电路的速度,但同时从读使能有效到最终数据有效将会多延迟一个时钟周期。在设计中要格外注意。根据设计自行设置。

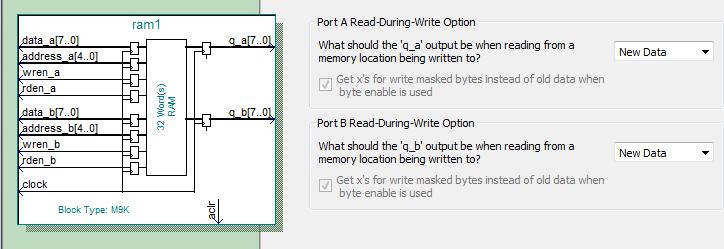

上面两张图是指定对同一地址操作时的输出。作为设计者,应尽量在自己的设计中避免这种情况发生。

真双口RAM用好了是非常省时间的。之前我们文章中提到硬件FFT的实现,在实现过程中,使用基2的设计方案,需要同时读取两个RAM数据,这种情况下可以使用真双口RAM提高效率。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

双口RAM,值得研究的更多相关文章

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 用嵌入式块RAM IP核配置一个双口RAM

本次设计源码地址:http://download.csdn.net/detail/noticeable/9914173 实验现象:通过串口将数据发送到FPGA 中,通过quartus II 提供的in ...

- 单口 RAM、伪双口 RAM、真双口 RAM、单口 ROM、双口 ROM 到底有什么区别呢?

打开 IP Catalog,搜索 Block Memory Generator,即可看到其 Memory Type 可分为 5 中,分别是单口 RAM(Single Port RAM).伪双口 RAM ...

- FMC与FPGA双口ram通讯

硬件环境:ARM+FPGA通过FMC互联,STM32F767和 EP4CE15F23I7 FMC设置,STM的系统时钟HCLK为216MHz /* FMC initialization functio ...

- 单口RAM、双口RAM、FIFO

单口与双口的区别在于,单口只有一组数据线与地址线,因此读写不能同时进行.而双口有两组数据线与地址线,读写可同时进行.FIFO读写可同时进行,可以看作是双口. 双口RAM分伪双口RAM(Xilin ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 单双口RAM

// Quartus II Verilog Template// Simple Dual Port RAM with separate read/write addresses and// singl ...

- 【知识强化】第三章 存储系统 3.5 双口RAM和多模块存储器

下面我们进入双端口RAM和多模块存储器的学习.这是提高我们的存储器的访存速度的一些措施. 我们之前已经讲过我们的主存和CPU是进行连接的,那么这就导致了一个问题就是说,随着我们现代科技的发展,计算机的 ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

随机推荐

- 二十四、DBMS_SQL

1.概述 1) 在整个程序的设计过程中,对游标的操作切不可有省略的部分,一旦省略其中某一步骤,则会程序编译过程既告失败,如在程序结尾处未对改游标进行关闭操作,则在再次调用过程时会出现错误. 2) db ...

- 利用Docker编译Hadoop 3.1.0

前言 为什么要使用Docker编译,请自行百度 操作系统环境:Centos 6.8 uname -r 内核版本:2.6.32-642.el6.x86_64 除非有把握否则不要在Centos6.8中直接 ...

- 通过格式化字符串漏洞绕过canary

1.1 canary内存保护机制 1.1.1 canary工作原理 canary保护机制类似于/GS保护机制,是Linux下gcc编译器的安全保护机制之一,在栈中的结构如下图所示: 在函数 ...

- # 2018-2019-2 20165210《网络攻防技术》Exp1 PC平台逆向破解(BOF实验)

2018-2019-2 20165210<网络攻防技术>Exp1 PC平台逆向破解(BOF实验) 实验分为三个部分: 手工修改可执行文件,改变程序执行流程,直接跳转到getShell函数. ...

- (三) ffmpeg filter学习-编写自己的filter

目录 目录 什么是ffmpeg filter 如何使用ffmpeg filter 1 将输入的1920x1080缩小到960x540输出 2 为视频添加logo 3 去掉视频的logo 自己写一个过滤 ...

- Ubuntu循环登录libGL error: fbConfigs swrast等

Ubuntu16.04更新NVIDIA驱动后,无法进入桌面,使用vim .xsession-errors 查看错误信息,如下: libGL error: No matching fbConfigs o ...

- JDiPad项目runtime的使用分析

首先,项目有点老 但是运行还是没有问题的.其中很多地方到了runtime,同时也看到了 早期的开发人员 基本没用pod 第三方也很少用,除了微信登录,整个项目还没看到集成的第三方SDK.然后慢慢梳理 ...

- 【sklearn】性能度量指标之ROC曲线(二分类)

原创博文,转载请注明出处! 1.ROC曲线介绍 ROC曲线适用场景 二分类任务中,positive和negtive同样重要时,适合用ROC曲线评价 ROC曲线的意义 TPR的增长是以FPR的增长为代价 ...

- php自动添加相关文章

{pc:content action="relation" relation="$relation" id="$id" catid=&quo ...

- hexo的环境搭建

今天开始折腾下hexo,安装起来还是有点坑,简单记录下,会不断更新. 网上安装的文章多不胜数,当然首先还是得去看看官方的文档. 按照官方的文档,不知大家是否顺利,本人搭建环境的时候并不顺利. 明确要安 ...