使用uart串口接收模块接收信号,控制led灯闪烁

功能描述:

使用遵循uart协议的接收模块接收控制信号,用来控制led的闪烁。

设计输入:

1.uart输入信号

2.时钟信号

3.复位信号

4.led信号

设计思路:

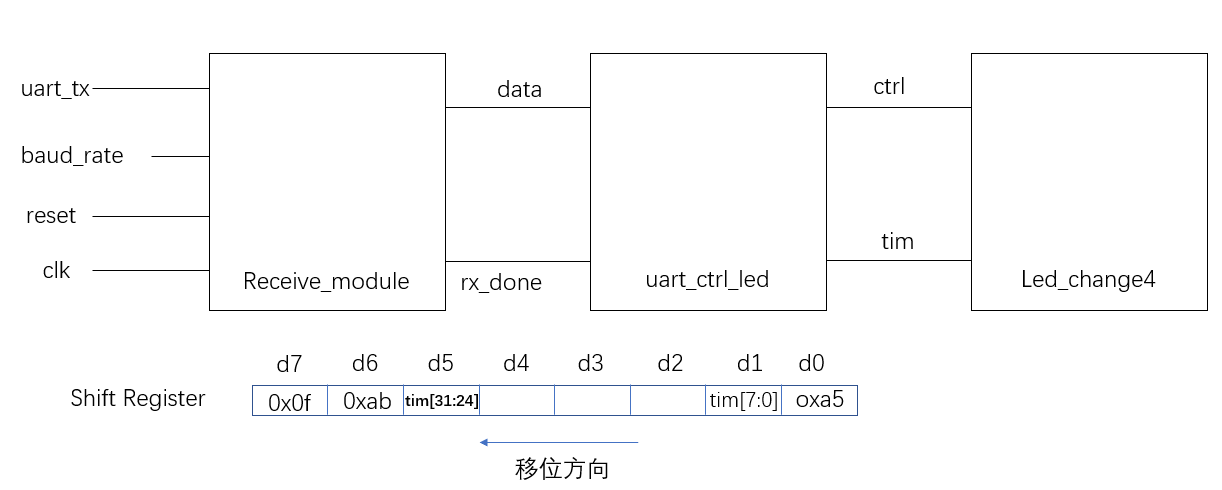

总体上:前面已经写了串口接收模块,led闪烁模块。现在要把接收到的多个数据对应传送给led闪烁模块的输入(闪烁周期,亮灭模式设置),我们再写一个模块来实现传输的功能,然后在顶层把这三个模块进行连线就可以了。

细节处:单个数据的传输遵循uart协议,而为了确定传送来的数据哪个对应led的时间设置,哪个对应亮灭模式设置,我们也需要人为再设定一个协议,第一,二个数据为某固定值时,视为开端,然后接着是对应数据,最后一个数据是固定值。发送数据端应按照这个协议来发送各个数据,这样子接收端就可以按照这个协议来控制输入led的信号了。

注意

①在代码中用到了延时,如#xx......等,则应在文件第一行写明时间单位和精度:·timescale ns/ns 。

②如果想让某个标志信号siagnl_a 延后一个周期,可以新设定一个信号siagnl_b,让siagnl_b永远等于siagnl_a就行。

③在本次设计中,修正了receive_rx_1代码中把r_data赋给data的时刻以及清零时刻。

学习:

①设计底层模块convert,顶层直接连线很方便。

②对于串口通信的应用,一般都有串口接收模块+移位寄存器+协议+应用功能 四个部分组成,其中,串口模块和功能模块一般已经设计好了,我们要设计移位寄存器和协议,即接收到的数据用来干嘛,怎么排序对应。

③判断条件设定的技巧: if(const <= variable),有两个好处:Ⅰ.常数const不能被变量variabl赋值,以此检查会不会把比较符写成赋值符。Ⅱ.用<=取代 == ,可以避免 == 的时刻已经被跳过,导致判断条件无法实现。

设计:

代码:

`timescale 1ns / 1ns

module uart_rx_ctrl_led(//顶层,就是连线

clk,

reset,

uart_tx,

led

);

input clk;

input reset;

input uart_tx;

output led; //本模型由uart_receive到led_chang的传输协议为:

//0x0f,0xab,tim[31:24] tim[23:16] tim[15:8] tim[7:0] ctrl[7:0] oxa5 //首先例化三个模块进来

wire [2:0]baud_rate ;

assign baud_rate = 3'd5 ;

wire [7:0]data;

wire rx_done;

uart_receive_1 uart_receive(//接收模块

clk ,

reset ,

baud_rate ,

uart_tx,

data ,

rx_done

); wire [31:0]tim;

wire [7:0]ctrl;

uart_led_convert uart_led_convert(//转换模块

data,

rx_done,

clk,

reset,

tim,

ctrl

); led_change4 led_change4(//led闪烁模块

clk,

reset,

ctrl,

tim,

led

); endmodule

module uart_receive_1(

clk ,

reset ,

baud_rate ,

uart_tx,

data ,

rx_done

);

input clk ;

input reset ;

input [2:0]baud_rate ;

input uart_tx ;

output reg [7:0]data ;

output reg rx_done ; reg [2:0]r_data[7:0] ;//接收每一位数据

reg [2:0]sta_bit ;

reg [2:0]sto_bit ; reg [17:0]bit_tim ;//每一位持续的时间(计数)

always@(baud_rate) //在这里一个 码元由一位组成,所以波特率=比特率

begin

case(baud_rate) //常见的串口传输波特率

3'd0 : bit_tim = 1000000000/300/20 ; //波特率为300

3'd1 : bit_tim = 1000000000/1200/20 ; //波特率为1200

3'd2 : bit_tim = 1000000000/2400/20 ; //波特率为2400

3'd3 : bit_tim = 1000000000/9600/20 ; //波特率为9600

3'd4 : bit_tim = 1000000000/19200/20 ; //波特率为19200

3'd5 : bit_tim = 1000000000/115200/20 ; //波特率为115200

default bit_tim = 1000000000/9600/20 ; //多余的寄存器位置放什么:默认速率

endcase

end wire [17:0]bit_tim_16 ;//每1/16位的持续时间(计数)

assign bit_tim_16 = bit_tim / 16; wire [8:0]bit16_mid ; //在中心点产生采样脉冲

assign bit16_mid = bit_tim_16 / 2 ; //边沿检测

reg [1:0]edge_detect ;

always @( posedge clk or negedge reset )

begin

if (!reset )

edge_detect <= 2'd0 ;

else

begin

edge_detect[0] <= uart_tx ;

edge_detect[1] <= edge_detect[0] ;

end

end wire byte_sta_neg ;

assign byte_sta_neg = ( edge_detect == 2'b10 ) ? 1 : 0 ;//输入的数据开始出现下降沿,说明出现了起始位(一直运行?) reg receive_en ;//接收使能端

reg [17:0]div_cnt ;//每1/16bit内的计数

reg [7:0]bit16_cnt ;//计数到了第几个状态(10位,每位分成16份,总共160个状态)

always @( posedge clk or negedge reset )

begin

if (!reset )

receive_en <= 1'd0 ;

else if ( byte_sta_neg ) //检测到下降沿,使能段有效(只要有下降沿就使能?)

receive_en <= 1'd1 ;

else if ( (rx_done) || (sta_bit >= 3'd4 ))

receive_en <= 1'd0 ; //检测到结束信号,使能端无效

else if ( ( bit16_cnt == 8'd159 ) && (div_cnt == bit_tim_16 - 1'd1 ) )//跑完159后re_en置零

receive_en <= 1'd0 ;

end always@( posedge clk or negedge reset )

begin

if ( ! reset )

div_cnt <= 18'd0 ;

else if (receive_en)

begin

if ( div_cnt == bit_tim_16 - 1'd1 )//计数,每1/16bit清零

div_cnt <= 18'd0 ;

else

div_cnt <= div_cnt + 1'b1 ;

end

else

div_cnt <= 18'd0 ;

end reg bit16_pulse ;//产生采样脉冲

always@( posedge clk or negedge reset )

begin

if ( ! reset )

bit16_pulse <= 18'd0 ;

else if (receive_en)

if ( div_cnt == bit16_mid )

bit16_pulse <= 1'd1 ;

else

bit16_pulse <= 1'd0 ;

else

bit16_pulse <= 1'd0 ;

end always@( posedge clk or negedge reset )

begin

if ( ! reset )

bit16_cnt <= 8'd0 ;

else if (receive_en)

begin

if (( bit16_cnt == 8'd159 ) && (div_cnt == bit_tim_16 - 1'd1 ))

bit16_cnt <= 8'd0 ;

else if ( div_cnt == bit_tim_16 - 1'd1 )

bit16_cnt <= bit16_cnt + 1'b1 ;

end

end always@(posedge clk or negedge reset)

begin

if(!reset)

begin

sta_bit <= 3'd0 ;

r_data[0] <= 3'd0 ;

r_data[1] <= 3'd0 ;

r_data[2] <= 3'd0 ;

r_data[3] <= 3'd0 ;

r_data[4] <= 3'd0 ;

r_data[5] <= 3'd0 ;

r_data[6] <= 3'd0 ;

r_data[7] <= 3'd0 ;

sto_bit <= 3'd0 ;

end

else if (bit16_pulse)//舍弃前5后4取中7

case(bit16_cnt)

0:

begin

sta_bit <= 3'd0 ;

r_data[0] <= 3'd0 ;

r_data[1] <= 3'd0 ;

r_data[2] <= 3'd0 ;

r_data[3] <= 3'd0 ;

r_data[4] <= 3'd0 ;

r_data[5] <= 3'd0 ;

r_data[6] <= 3'd0 ;

r_data[7] <= 3'd0 ;

sto_bit <= 3'd0 ;

end

5,6,7,8,9,10,11 : sta_bit <= sta_bit + uart_tx ;

21,22,23,24,25,26,27 : r_data[0] <= r_data[0] + uart_tx ;

37,38,39,41,42,43,44 : r_data[1] <= r_data[1] + uart_tx ;

53,54,55,56,57,58,59 : r_data[2] <= r_data[2] + uart_tx ;

69,70,71,72,73,74,75 : r_data[3] <= r_data[3] + uart_tx ;

85,86,87,88,89,90,91 : r_data[4] <= r_data[4] + uart_tx ;

101,102,103,104,105,106,107 : r_data[5] <= r_data[5] + uart_tx ;

117,118,119,120,121,122,123 : r_data[6] <= r_data[6] + uart_tx ;

133,134,135,136,137,138,139 : r_data[7] <= r_data[7] + uart_tx ;

149,150,151,152,153,154,155 : sto_bit <= sto_bit + uart_tx ;

default ;

endcase

end always@( posedge clk or negedge reset )

begin

if ( ! reset )

rx_done <= 8'd0 ;

else if ( ( bit16_cnt == 8'd159 ) && (div_cnt == bit_tim_16 - 1'd1 ) )//跑完159后产生一个rx_done信号

rx_done <= 8'd1 ;

else if (rx_done <= 8'd1 )

rx_done <= 8'd0 ;

end always@( posedge clk or negedge reset )//接收完数据发出rx_done后,把数据从r_data传递给data

begin

if ( ! reset )

data <= 8'd0 ;

else if (bit16_pulse)//舍弃前5后4取中7

case(bit16_cnt)

28:data[0] = ( r_data[0] >3 ) ? 1 : 0 ;

44:data[1] = ( r_data[1] >3 ) ? 1 : 0 ;

60:data[2] = ( r_data[2] >3 ) ? 1 : 0 ;

76:data[3] = ( r_data[3] >3 ) ? 1 : 0 ;

92:data[4] = ( r_data[4] >3 ) ? 1 : 0 ;

108:data[5] = ( r_data[5] >3 ) ? 1 : 0 ;

124:data[6] = ( r_data[6] >3 ) ? 1 : 0 ;

140:data[7] = ( r_data[7] >3 ) ? 1 : 0 ;

endcase

else if(rx_done)

data <= 8'd0 ;

end endmodule

`timescale 1ns / 1ns

module uart_led_convert(

data,

rx_done,

clk,

reset,

tim,

ctrl

);

input [7:0]data;

input rx_done;

input clk;

input reset;

output reg [31:0]tim;

output reg [7:0]ctrl; //设定本模型由uart_receive到led_chang的传输协议为:

//0x0f,0xab,tim[31:24] tim[23:16] tim[15:8] tim[7:0] ctrl[7:0] oxa5

//设计一个二维移位寄存器

reg [7:0]data_regist[7:0];

always@(posedge clk or negedge reset)

begin

if(!reset)

begin

data_regist[0] <= 0;

data_regist[1] <= 0;

data_regist[2] <= 0;

data_regist[3] <= 0;

data_regist[4] <= 0;

data_regist[5] <= 0;

data_regist[6] <= 0;

data_regist[7] <= 0;

end

else if(rx_done)

begin

data_regist[0] <= data ;

data_regist[1] <= data_regist[0] ;

data_regist[2] <= data_regist[1] ;

data_regist[3] <= data_regist[2] ;

data_regist[4] <= data_regist[3] ;

data_regist[5] <= data_regist[4] ;

data_regist[6] <= data_regist[5] ;

data_regist[7] <= data_regist[6] ;

end

end always@(posedge clk or negedge reset)

begin

if(!reset)

begin

tim <= 0 ;

ctrl <= 0 ;

end

else if ( ( data_regist[0] == 8'ha5 ) && ( data_regist[6] == 8'hab ) && ( data_regist[7] == 8'h0f ) )

begin

ctrl[7:0] <= data_regist[1] ;

tim[7:0] <= data_regist[2] ;

tim[15:8] <= data_regist[3] ;

tim[23:16] <= data_regist[4] ;

tim[31:24] <= data_regist[5] ;

end

end

endmodule

module led_change4( //以tim*20/8 ns为变化周期,tim*20 ns为一个循环,每个周期的亮灭模式,tim由用户设置。.

clk,

reset,

ctrl,

tim,

led

);

input clk;

input reset;

input [7:0]ctrl;

input [31:0]tim;

output reg led ; reg [31:0]counter0; always@( posedge clk or negedge reset )

begin

if ( reset == 0 )

counter0 <= 32'b0 ;

else if ( tim - 1 <= counter0 )

counter0 <= 0 ;

else

counter0 <= counter0 + 1'd1;

end always@( posedge clk or negedge reset )

begin

if ( reset == 0 )

led <= 0 ;

else case( counter0 ) //可以用第二个计数器的方法来设置判断条件

tim * 1 / 8 - 1 : led <= ctrl[0] ;

tim * 2 / 8 - 1 : led <= ctrl[1] ;

tim * 3 / 8 - 1 : led <= ctrl[2] ;

tim * 4 / 8 - 1 : led <= ctrl[3] ;

tim * 5 / 8 - 1 : led <= ctrl[4] ;

tim * 6 / 8 - 1 : led <= ctrl[5] ;

tim * 7 / 8 - 1 : led <= ctrl[6] ;

tim * 8 / 8 - 1 : led <= ctrl[7] ;

default led <= led ;

endcase

end

endmodule

使用uart串口接收模块接收信号,控制led灯闪烁的更多相关文章

- 树莓派开机运行Python脚本 控制LED灯闪烁

一.新建一个开机运行文件 在 /home/pi/.config 下创建一个文件夹,名称为 autostart,并在该文件夹下创建一个led.desktop文件(文件名以.desktop结尾) 编辑le ...

- C#与Arduino通过串口通信来控制LED灯的状态

一.引言 最近摆弄了一段时间的Arduino,发现Arduino做一些电子类项目.监控.机器人.电子玩具比较容易,并且Arduino与.NET程序集成也不难.接下来介绍一个简单的小程序,C#做的一个W ...

- arduino入门学习实现语音控制LED灯

需要的准备的硬件arduino+PC+麦克风实现语音命令控制LED灯的亮灭. 首先需要将写好的arduino程序烧录到arduino uno主板中,下面是代码如下: int val;//定义变量val ...

- arduino 红外遥控器控制LED灯

/* 日期:2016.9.1 功能:红外遥控器控制LED灯 开,关,闪烁,呼吸 元件: 跳线公公头 * 5 led 220欧电阻 红外接收管,红外遥控 接线: 红外灯面向自己从左到右分别接 IO3 , ...

- BLE 安卓APP控制LED灯的实现(转)

源:BLE 安卓APP控制LED灯的实现 //注:参考AmoMcu源代码修改. 打开APP,检查蓝牙是否打开 BluetoothAdapter mBluetoothAdapter; final Blu ...

- Arduino控制LED灯(开关控制)

问题:当使用"digitalRead(BUT) == 1"控制LED灯时会出现"digitalWrite(LED, ledState);"的值出现跳动. 原因: ...

- 嵌入式Linux学习入门:控制LED灯

记录自己linux学习过程,让自己能够一直坚持下去 1.原理图分析: nLED_1, nLED_2, nLED_4, 给低电平则对应LED灯亮,高电平则对应LED灯灭, S3C2440芯片GPF4-G ...

- enc28J60 网页控制LED灯

软件IDE:Arduino 1.6.3 1.库的安装: 从https://github.com/jcw/ethercard 下载源码包,解压,复制ethercard-master文件夹到Arduino ...

- 云中树莓派(4):利用声音传感器控制Led灯

云中树莓派(1):环境准备 云中树莓派(2):将传感器数据上传到AWS IoT 并利用Kibana进行展示 云中树莓派(3):通过 AWS IoT 控制树莓派上的Led 云中树莓派(4):利用声音传感 ...

随机推荐

- fedora使用root超级用户

sudo -i可以使当前用户变成root帐号. 这样就不用一遍一遍的输sudo 了! 原来用sudo su也可以.

- H5如何实现唤起APP

前言 写过hybrid的同学,想必都会遇到这样的需求,如果用户安装了自己的APP,就打开APP或跳转到APP内某个页面,如果没安装则引导用户到对应页面或应用商店下载.这里就涉及到了H5与Native之 ...

- MySQL(8) - MySQL的事务机制

MySQL数据库的事务机制 1.1.事务的概念和特性 1.2.事务的隔离级别 repeatable read是mysql默认的事务隔离级别 #事务A #事务A,临时修改工资,未commit, STAR ...

- Golang可重入锁的实现

Golang可重入锁的实现 项目中遇到了可重入锁的需求和实现,具体记录下. 什么是可重入锁 我们平时说的分布式锁,一般指的是在不同服务器上的多个线程中,只有一个线程能抢到一个锁,从而执行一个任务.而我 ...

- 基于RabbltMQ延迟插件实现延迟队列代码示例

上一篇文章写了docker安装RabbitMQ及延迟插件的安装,这篇的话是基于RabbitMQ延迟插件实现延迟队列的示例 那么废话不多说 直接上代码!! 首先创建延迟队列配置类 DelayedQueu ...

- 定制.NET 6.0的依赖注入

大家好,我是张飞洪,感谢您的阅读,我会不定期和你分享学习心得,希望我的文章能成为你成长路上的垫脚石,让我们一起精进. 在本章中,我们将学习ASP.NET Core的依赖项注入(DI)以及如何自定义它. ...

- Apache Shiro反序列化漏洞(Shiro550)

1.漏洞原理: Shiro 是 Java 的一个安全框架,执行身份验证.授权.密码.会话管理 shiro默认使用了CookieRememberMeManager,其处理cookie的流程是:得到rem ...

- 你真的了解git的分支管理跟其他概念吗?

现在前端要学的只是太多了,你是不是有时会有这个想法,如果我有两个大脑.一个学Vue,一个学React,然后到最后把两个大脑学的知识再合并在一起,这样就能省时间了. 哈哈,这个好像不能实现.现实点吧!年 ...

- 【RPA之家转载RPA创新产业峰会回看】机器人流程自动化专利态势报告

[RPA之家转载RPA创新产业峰会回看]机器人流程自动化专利态势报告 自动化的一个专利情况的监测,就是全球监测的情况.今天我可能给大家汇报的主要是三个方面,第一个方面就是讲一下全球投资智能化的专利的一 ...

- 【前端面试】(三)JavaScript相等(==)和全等(===)运算符的区别

视频链接: JavaScript相等()和全等(=)运算符的区别 - Web前端工程师面试题讲解 参考链接: JavaScript == 与 === 区别 区别 对于string.number 等基础 ...