VerilogHDL概述与数字IC设计流程学习笔记

一、HDL的概念和特征

HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言。那么什么是硬件描述语言呢?为什么不叫硬件设计语言呢?硬件描述语言,顾名思义就是描述硬件的语言,它用文本的形式来描述电子系统硬件结构和行为,是一种用形式化方法来描述数字电路和系统的语言。正是因为如此,硬件与软件不一样,他不像软件,你某天突发奇想,想实现某个的界面,搞搞代码就OK了。硬件它是由实实在在的物理器件搭载而成,用抽象的语言怎么可能弄出一个电路来呢?

一门语言,总有那么一些特殊之处,不然人家就不认,HDL主要有下面一些特征:

①HDL语言既包括一些高级程序设计语言的结构形式,同时也兼顾描述硬件线路连接的具体结构。

②通过使用结构级描述,可以在不同的抽象层次描述设计。HDL语言采用自顶向下的数字电路设计方法。

③HDL语言是并行处理的,具有同一时刻执行多任务的能力,这个和高级设计语言串行执行的特征是不同的。

④HDL语言具有时序的概念。一般的高级语言没有时序的概念,但在硬件电路中从输入到输出是有延时存在的,为了描述这一特征,需要引入时延的概念。因此HDL语言不仅可以描述电路的功能,还可以描述电路的时序。

二、Verilog HDL的发展历史

1983年,Gateway Gesign Automation 硬件描述语言公司的Philip Moorby这个人(带领团队)首创了Verilog HDL。

1984~1986年,Moorby设计出第一个关于VerilogHDL的仿真器。

1987年,synopsys公司使用verilog HDL作为综合工具的输入。

1989年,cadence公司收购Gateway公司,因此verilog也成为的cadence的囊中之物。

1990年初,cadence公开发布verilogHDL,后来open verilog HDL international组织(由verilog使用者和计算机辅助工程供应商组成)指定标准。

1993年,几乎所有的ASIC厂商都支持verilogHDL,OVI推出了verilog HDL 2.0版本。接着IEEE把verilog HDL 2.0 作为IEEE标准的提案。

1995年12月,IEEE制定了Verilog HDL的标准IEEE 1364--1995。

2000年,发展为IEEE 1364--2000.

最后,在2005年,verilog 的标准停止在了IEEE 1364--2005。05年以后,与verilog有关的system verilog了,verilog的标准就不再更新了,而是融入到system verilog中。我们现在用的verilog HDL,都是按照05年及其以前的标准制定的语法。

三、Verilog HDL 的描述能力

在前面已经讲到,Verilog HDL可以在不同的的抽象层次进行描述电路下面的它们的具体层次分类:

|

描述级别 |

抽象级别 |

功能描述 |

物理模型 |

|

行为级 |

系统级 |

用语言提供的高级结构实现所设计模块外部性能的模型 |

芯片、电路板和物理划分的子模块 |

|

算法级 |

用语言提供的高级功能实现算法运行的行为 |

部件之间的物理连接,电路板 |

|

|

RTL级 |

描述数据如何在寄存器之间流动和如何处理、控制这些数据流动的模型 |

芯片、宏单元 |

|

|

逻辑级 |

门级 |

描述逻辑门之间的连接模型 |

标准单元布图 |

|

电路级 |

开关级 |

描述器件中三极管和存储节点以及它们之间连接的模型 |

晶体管布图 |

在这里说明一下,行为级描述中的系统级和算法级描述很少用Verilog HDL进行描述,而是用matlab 或者C++进行描述,逻辑级和电路级也几乎不用Verilog HDL进行描述。真正用到的是寄存器传输级(RTL级),因此在描述RTL级的时候,Verilog HDL根据设计和语法的情况,有可以分为行为描述和结构描述,这个在以后的语法中会说到。

四、Verilog HDL的应用

Verilog HDL的一个大致情况以及说明了,那么Verilog HDL主要有哪些应用呢?毫无疑问,就是用它来进行数字逻辑设计了,只要是在FPGA(field programer gate array ,现场可编程逻辑门阵列)的逻辑设计和数字集成电路设计前端的逻辑设计中用到。下面就来谈谈FPGA的设计流程和数字IC设计的流程吧。

五、FPGA设计流程

这个设计流程我就不记录,毕竟有一部分是跟后面的数字IC设计流程重复。

六、数字IC设计与流程概述

在开篇的时候,我先讲一下IC设计分类跟设计流程,提前声明一下,由于本人水平有限,加上没有完全亲身体验过从设计规划到工艺制造这一完整的设计流程,只是知道这一流程的某些步骤,因此本篇的设计流程是我根据我的一些实践体会、一些文献内容、一些网络资料、与一些工程师的交谈等得出的一个大体流程,这个流程也许跟一些公司的流程不一样,如果有错误的地方,希望指出。本篇我主要记录的内容是IC设计的分类跟IC设计的流程概述。没错,就只有这些内容,毕竟我比较垃圾,“狗嘴里吐不出象牙”,现在我们就看看这IC吧。

分类:

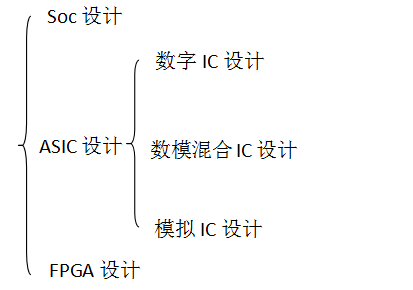

IC也就是集成电路,通俗的讲也就是芯片了。我觉得芯片设计在现在来看,主要有Soc芯片设计、ASIC设计、FPGA设计,如下图所示:

也许有人就出来抬杠了,说:“你这是在扯淡,不是还有功率IC这些分类么?!”。我这里是说主要,是根据大体的方向分的,功率IC嘛...可以算是数模混合里面,也有可以是模拟的里面,看你怎么做了。总之,大体分类就是这么一个情况了。

这里着重强调一下,我以后所说的,包括流程啊,设计概述啊,还是什么乱七八糟的,都是关于ASIC设计里面的,有时间我们再来掰扯掰扯SoC跟FPGA设计的问题,毕竟ASIC在向着SoC发展,此外FPGA也是不可忽略的一块领域。模拟那些问题嘛,我不是很感兴趣,就不在这里记载了,这里涉及的都是数字设计相关的。当然,这只是有时间哈,没有时间,谁想理这些东西,还是好好地弄好自己的方向吧(我自己定下的方向是:数字IC(系统)设计,数字信号处理相关,至于详细的方向嘛,可能是通信,也可能是图像,也可能是音频等等,到时候再说吧,现在每个领域都涉及一点再说。。。)。

废话不多少,现在来看一下数字IC的设计流程吧。

流程:

设计之前——项目策划

在设计之前,需要知道自己为什么要设计这么一个数字IC(系统)。因此在设计之前要进行项目策划。

项目策划呢,大概就是这么一个过程,首先市场部门(营销部门)等有关部门(“有关”这个官方词语,还是很好用的,哈哈)根据经济状况,对市场进行调研或者反馈,得出市场的需求;或者一些先进的有关领导,注意到某些比较现在或者将来发展比较好领域,决定要开发这么各个产品。于是开会,决定这个东西可以赚一笔的时候,就让技术人员跟市场部的进行研究、论证,最后又开一次大会,决定:“好,就这么干!”。于是,一份项目策划书就出来了。这个项目策划书一出来,蚂蚱都得在这一根绳上爬了。项目策划书里面有啥内容呢,其实...我也不知道,md我又不是产品经理、或者什么部门老大,我怎么知道,但是,有小到消息说,里面有:对项目时间及资源的描述;对设计项目的目标描述;风险和成本的估计分析等(具体我也不清楚,我就一硅农,哈哈哈哈)。

OK,项目策划完成了,下面就开始进行设计了。

设计ing——技术人员的活

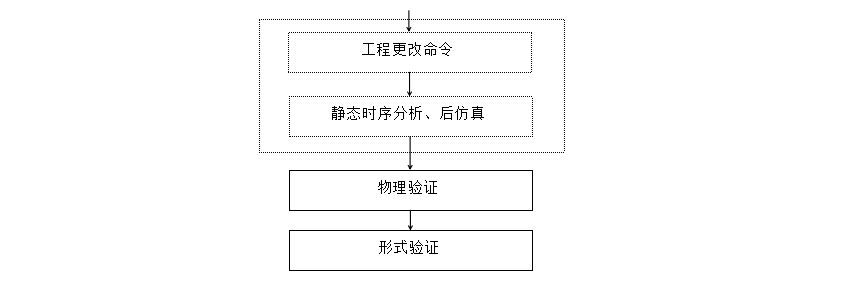

设计流程大概有下面这些步骤:系统总体规划、模块设计、顶层模块集成、顶层功能模块验证、逻辑综合、形式验证、静态时序分析、可测性设计插入、芯片版图物理规划、功耗分析、单元布局与优化、时钟树综合、布线、信号完整性分析、寄生参数提取、后仿真、工程更改命令、物理验证。用下图表示流程可能更清晰一点:

简单地,可以分成系统设计,前端设计,后端设计。前端设计主要是输入、验证、综合;后端设计主要是APR(自动布局布线,也就是从floorplan→布局→布线)。当然,这些流程也不是完全顺序操作下去的,此外,全部的数字IC系统设计也未必按照这个流程跑,当有错的时候,也是需要返回去进修改的,这里我就不返回去了。下面是相关步骤的概述,每一部分包含的内容至少有一个章,这里仅仅是简单介绍。

1、系统总体规划(system global plan)

项目策划完成,领导开始让工人们干活。首先就是高级工人,系统算法工程师,根据要求,搞一堆算法来,看看哪一个比较符合老大的项目策划书要求。系统架构工程师根据系统算法工程师提出的算法,想想怎么用详细的特定功能硬件实现,发现算法的硬件实现比较坑爹,就去找系统算法工程师理论。然后这两类系统工程师通过对系统的方案、设计、仿真跟各种撕逼之后(他们撕逼的内容听说有这些:浮点数算法,软硬件划分,IC设计中数据的定点表示,定点算法表示,结构的并行性跟流水线,存储器分配,还有其他等...),达到平衡点(就是算法能够较好地使用良好架构跟电路的实现),一份系统设计规格书就出来了。至于系统设计规格书里面具体有什么,我们就不展开说明了。

2、模块设计(module design)

高级的系统工程师完毕,就到我们这些螺丝钉,进行模块设计了。模块设计也还是分等级,人家有高级数字IC设计工程师。而真正专门写模块的呢,就是螺丝钉级的一般数字IC工程师,别称”硅农”...透露一下,系统设计规格书里面就有进行模块划分的内容,这里就是进行设计模块了。一般,模块设计使用HDL语言进行输入,输入工具使用GVIM。写完一个模块了,(进行代码设计规则检查,这个靠检查工具来工作了,检查工具可以检测几百个设计规则,检查的内容主要有:标准规则检查、可重用性检查、竞争条件检查、可综合性、可测试性、时钟域、结构性、加速策略、用户自定义的规则等),然后进行功能验证,就是验证你写的这个电路是不是符合模块的功能要求,使用的工具是synopsys的VCS。仿真通过之后,就可以把模块提交上去了给上层负责管理顶层模块的高级数字IC工程师了。有兴趣的话,可以自己综合一下自己负责维护的模块。

3、顶层模块集成(top level integration)

底层的的模块写完之后,开始进行模块集成,新模块跟复用的旧模块集成,I/O,时钟等模块的基础,把系统集成起来,构成整个系统后,就完成了系统模块的集成。

4、顶层功能模块验证(top level verification)

顶层模块集成完毕后,检测集成之后模块是否还能正常工作,验证功能是否正确,各项指标是否完好等等。这里,数字IC验证工程师就可以放大招了。验证使用VCS进行。验证是一门杂活哇,各种方法学UVM之类的,还是我们硅农的小模块验证比较好。

5、逻辑综合(logic synthesis)

逻辑综合就是通过EDA工具把顶层的HDL模块,在一定的约束情况下,映射到制造厂家标准单元库元件的门级电路的过程。通过这个步骤,从HDL代码,得到了门级网表,也就是得到了电路。具体的有关综合的知识将在后文联合synopsys的综合工具design compiler进行记载。

6、形式验证(formal verification)

形式验证,就是对设计过程中不同阶段的输出结果进行逻辑功能一致性的对比,根据电路的结构,判断两个设计在逻辑功能上是否对等。有关形式验证的知识将在后文中记载。

7、静态时序分析(static time analysis,STA)

静态时序分析,就是通过EDA工具,提取电路中所以路径的延迟信息进行分析,计算出信号在路径上的延时,检查时序是否满足设定的时序约束要求。静态时序分析将在后文中结合synopsys的PT工具进行记载。

8、可测性设计插入(design for test,DFT)

可测性设计是指:在进行电路的前端设计时,就预先规划、设计出如何在样片中进行电路的测试方案和办法,并通过逻辑综合过程完成芯片内部专用测试结构的插入,一遍在芯片形成后能按照预先制定的方案进行相应的电路功能测试的一种设计方法。也就是进行可测性设计,就是在原有的电路中插入专门测试的电路(插入电路)。

===========================================

上面的部分基本前端设计的部分,是我后面内容主要涉及的内容,后面的主要是后端设计的部分,这后端设计就是专业名词特别多,而且还中英互联,很少让人讨厌。所以后端的部分知识按照常规来介绍了

============================================

9、版图物理规划(floor-plan)

这一步骤主要是通过对EDA工具进行输入标准单元库、标准I/O库、综合后的网表、各种约束文件等,规划好让EDA工具完成各模块的位置摆放、电源网络的设定、I/O信号出口位置、同时确定面积、封装、工艺、噪声、负载能力等参数。

10、功耗分析(power analysis)

在完成版图物理规划后,需要进行功耗分析。功耗分析可以确定电源引脚的位置和电源线的宽度是否满足要求。对整个版图进功耗分析,即要进行动态功耗分析跟静态功耗分析,找出主要的功耗单元或者模块,以供优化。

11、单元布局与优化(placement & optimistic)

根据floor-plan中的布局规划,摆放网表中调用的所以标准单元,EDA工具自动对时序约束、布线面积、布线拥堵等综合考虑标准单元的摆放,从而依靠EDA工具完成电路的布局设计跟优化。

EDA主要进行自动对floor-plan的具体工作的标准单元实现:确定各功能模块的位置和整个芯片的尺寸;确定I/O buffer 的位置,定义电源和地PAD的位置;定义各种物理的组、区域或模块,对大的宏单元进行放置;设计整个供电网络,基于电势降和电迁移进行拓扑优化;通过布局调整、约束修改、属性添加、密度、高速信号分析等手段达到优化的目的。

12、时钟树综合(clock tree synthesis,CTS)

要了解时钟树综合,那么就得中断什么是时钟树。时钟树就是分布在芯片内部的的寄存器跟数字的驱动电流构成的一种树状结构的电路。时钟树综合就是EDA工具按照约束,插入buffer,使时钟的源头(时钟根节点)到达各个需要时钟驱动的器件(各叶子节点,如触发器)的时间基本一致的过程。时钟树综合通常使用EDA工具自动进行。

13、布线(routing)

布线就是完成模块、节点的相互连线。EDA工具可以分成全局布线和详细布线。一般情况下先使用EDA工具布线,然后在人工干预的情况下局部自动或者手工进行连接一些比较关键地连线,进行修复连接上的问题和时序约束上的问题。注意,关键路劲跟时钟上的连接线要尽量最先连接,以免绕线,导致时序问题。

14、信号完整性分析(signal competition analysis)

信号完整性分析是通常是进行分析噪声。随着器件尺寸的下降,器件的供电电压、噪声容限均下降。也就是说,也许由于某一根导线可能电阻过大,带来的压降过大,导致器件的供电电压达不到而不能正常工作等等的一系列问题。对这些问题进行分析,是信号完整分析的一部分。

15、寄生参数提取(parasitic extraction)

根据布线完成得版图提前RC(电阻电容)参数文件。对EDA工具输入相应的工艺参数(厂家提供)后,EDA工具根据这些参数和版图实际几何形体的面积计算出RC值,然后通过存储从而提取出RC参数。提取出来的RC参数,可以直接用于静态时序分析,也可以在计算出相应的路径延时时,用于反标功能后仿真。

16、后仿真(post-layout simulation)

后仿真也叫门级仿真、时序仿真、带反标的仿真。它是通过采用外部激励和布局布线后产生的标准延时文件(*.sdf),对布局布线后的门级电路网表进行功能和时序验证,来检验门级电路是否符合功能要求。

17、工程更改命令(engineering change order,ECO)

在设计的最后阶段发现个别路劲有时序问题或者逻辑错误时,通过芯片内部专门留下的寄存器跟组合逻辑,对设计部分进行必要的小范围的修改和重新连线。

ECO在是在网表上做文章,在非必须的情况下(如时间充足,人员充足),不要进行ECO。

18、物理验证(physical verification)

物理验证主要是一个对版图的设计结果是否预定要求而进行的验证过程。

首先是通过DRC(design rule check,设计规则检查)对版图设计中的约束违规情况进行检查,以保证各层版图都符合设计的要求。然后是进行LVS(layout vs. Schematic,版图网表与电路原理图比较),进行版图网表跟原始电路图的一致性对比检查,即通过版图寄生参数提取工具得到一个有版图寄生参数的电路图,将它跟原理电路图进行比较,以确保版图设计与原要求的电路图的逻辑功能一致性。

此外还有一些需要进行ERC,即电气规则检查。这里不详述了。

我所知道流程大概就是这样了,参考文献:

《Soc设计方法与实现(第二版)》

《EDA与集成电路工程实践》

《数字IC系统设计》

《数字集成电路设计与技术》

VerilogHDL概述与数字IC设计流程学习笔记的更多相关文章

- 【转载】数字IC设计流程及开发工具

原文链接:https://www.zhihu.com/question/28322269/answer/42048070 Design Flow <img src="h ...

- 数字IC设计入门书单

首发于观芯志 写文章 数字IC设计入门书单 Forever snow 1 年前 作者:Forever snow链接:你所在领域的入门书单? - 知乎用户的回答来源:知乎著作权归作者所有,转 ...

- 数字IC设计工程师的知识结构

刚毕业的时候,我年少轻狂,以为自己已经可以独当一面,庙堂之上所学已经足以应付业界需要.然而在后来的工作过程中,我认识了很多牛人,也从他们身上学到了很多,从中总结了一个IC设计工程师需要具备的知识架构, ...

- 《Photoshop智能手机APP界面设计》学习笔记-转

第一章 APP用户界面基础 1.1 手机UI设计相关基本概念 1.1.1 什么是UI设计 UI(User's Interface)即用户界面,它不仅仅是美化界面,还需要研究用户,让界面变得更友好.简洁 ...

- IC设计流程概述

芯片设计分为前端设计和后端设计,前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计. Front-end design flow 1. 规格制定 ...

- 数字IC设计入门必备——VIM自定义模板调用与VCS基本仿真操作示例

一.前言 毕业论文答辩结束,闲下来写篇文章.芯片研发人员都在Linux系统下借助各种EDA工具和代码语言完成工作,因此提高代码开发效率,熟练运用开发工具是十分必要的.本文讲述VIM编辑神器的veril ...

- IC设计流程介绍

芯片设计分为前端设计和后端设计,前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计. 1. 规格制定 芯片规格,也就像功能列表一样 ...

- 数字IC设计工程师成长之路

学习的课程 仿真工具VCS实践学习 2019年12月9日-2019年12月23日

- 数字IC设计-15-DPI(延续)

简介 供SV,无论是构建测试激励,或模拟硬件的并行行为,DPI这是非常方便.上次我们介绍SV内通"import"导入和电话C性能. 在本节,通过一个简单的例子来说明C什么语言的函数 ...

随机推荐

- 二分查找(binary search)

二分查找又叫折半查找,要查找的前提是检索结果位于已排序的列表中. 概念 在一个已排序的数组seq中,使用二分查找v,假如这个数组的范围是[low...high],我们要的v就在这个范围里.查找的方法是 ...

- (转)关于 Java 对象序列化您不知道的 5 件事

关于 Java 对象序列化您不知道的 5 件事 转自:http://developer.51cto.com/art/201506/479979.htm 数年前,当和一个软件团队一起用 Java 语言编 ...

- Bash扩展顺序

当进行变量替换.命令替换.数学扩展以及路径扩展时,Bash Shell遵循如下顺序: 1.大括号扩展 $ls f{oo,aa,unble} 2.~扩展 ~cb, ~/doc/working 3.命令参 ...

- java IO文件操作简单基础入门例子,IO流其实没那么难

IO是JAVASE中非常重要的一块,是面向对象的完美体现,深入学习IO,你将可以领略到很多面向对象的思想.今天整理了一份适合初学者学习的简单例子,让大家可以更深刻的理解IO流的具体操作. 1.文件拷贝 ...

- none 和 host 网络的适用场景 - 每天5分钟玩转 Docker 容器技术(31)

本章开始讨论 Docker 网络. 我们会首先学习 Docker 提供的几种原生网络,以及如何创建自定义网络.然后探讨容器之间如何通信,以及容器与外界如何交互. Docker 网络从覆盖范围可分为单个 ...

- Xmanager连接到RedHat Enterprise Linux 6.8

RedHat Enterprise Linux 6 配置Xmanager ,实现图形界面连接 X是用在大多数UNIX系统中的图形支持系统.如果你在你的Linux机器上使用GNOME或者KDE的话,你就 ...

- 浅谈Cordova框架的一些理解

前言 因为工作原因,最近需要研究Cordova框架,看了其中的源码和实现方式,当场在看的时候马上能理解,但是事后再回去看相关源码时候却发现之前理解的内容又忘记了,又不得不重新开始看,所以总觉得需要记录 ...

- java源码学习(五)LinkedList

LinkedList [TOC] 一.定义 public class LinkedList<E> extends AbstractSequentialList<E> imple ...

- java高并发锁的3种实现

初级技巧 - 乐观锁 乐观锁适合这样的场景:读不会冲突,写会冲突.同时读的频率远大于写. 以下面的代码为例,悲观锁的实现: Java代码 public Object get(Object key) ...

- Spring Boot 集成 Mybatis

原文:https://github.com/x113773/testall/issues/9 方式一:mybatis-spring-boot-starter---这种方式比较简单,具体步骤如下:1. ...