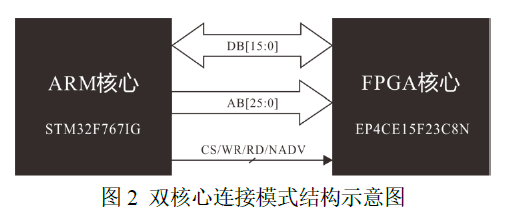

FMC与FPGA双口ram通讯

硬件环境:ARM+FPGA通过FMC互联,STM32F767和 EP4CE15F23I7

FMC设置,STM的系统时钟HCLK为216MHz

/* FMC initialization function */

void MX_FMC_Init(void)

{

FMC_NORSRAM_TimingTypeDef Timing; /** Perform the NOR1 memory initialization sequence

*/

hnor1.Instance = FMC_NORSRAM_DEVICE;

hnor1.Extended = FMC_NORSRAM_EXTENDED_DEVICE;

/* hnor1.Init */

hnor1.Init.NSBank = FMC_NORSRAM_BANK1;

hnor1.Init.DataAddressMux = FMC_DATA_ADDRESS_MUX_DISABLE;

hnor1.Init.MemoryType = FMC_MEMORY_TYPE_NOR;

hnor1.Init.MemoryDataWidth = FMC_NORSRAM_MEM_BUS_WIDTH_16;

hnor1.Init.BurstAccessMode = FMC_BURST_ACCESS_MODE_DISABLE;

hnor1.Init.WaitSignalPolarity = FMC_WAIT_SIGNAL_POLARITY_LOW;

hnor1.Init.WaitSignalActive = FMC_WAIT_TIMING_BEFORE_WS;

hnor1.Init.WriteOperation = FMC_WRITE_OPERATION_ENABLE;

hnor1.Init.WaitSignal = FMC_WAIT_SIGNAL_DISABLE;

hnor1.Init.ExtendedMode = FMC_EXTENDED_MODE_DISABLE;

hnor1.Init.AsynchronousWait = FMC_ASYNCHRONOUS_WAIT_DISABLE;

hnor1.Init.WriteBurst = FMC_WRITE_BURST_DISABLE;

hnor1.Init.ContinuousClock = FMC_CONTINUOUS_CLOCK_SYNC_ONLY;

hnor1.Init.WriteFifo = FMC_WRITE_FIFO_ENABLE;

hnor1.Init.PageSize = FMC_PAGE_SIZE_NONE;

/* Timing */

Timing.AddressSetupTime = ;

Timing.AddressHoldTime = ;

Timing.DataSetupTime = ;

Timing.BusTurnAroundDuration = ;

Timing.CLKDivision = ;

Timing.DataLatency = ;

Timing.AccessMode = FMC_ACCESS_MODE_A;

/* ExtTiming */ if (HAL_NOR_Init(&hnor1, &Timing, NULL) != HAL_OK)

{

_Error_Handler(__FILE__, __LINE__);

}

}

verilog核心代码,其中双口ram的a口与FPGA内部模块相连,b口与ARMFMC端口相连,clk时钟为100MHz

reg wr_clk1,wr_clk2;.

wire rd = (cs0 | rdn);

wire wr = (cs0 | wrn);

wire clk_b = (!wr_clk2 | !rd); ram u1(

.data_a(data_a),

.address_a(address_a),

.wren_a(wren_a),

.rden_a(rden_a),

.clock_a(clk_50m),

.q_a(dataout_a), .data_b(db),

.address_b(ab),

.wren_b(!wr),

.rden_b(!rd),

.clock_b(clk_b),

.q_b(dataout_b)

); always@(posedge clk_100m or negedge rst_n)

if(!rst_n)

begin

wr_clk1 <= 'd1;

wr_clk2 <= 'd1;

end

else

{wr_clk2,wr_clk1} <= {wr_clk1,wr}; assign db = !rd ? dataout_b : 'hzzzz;

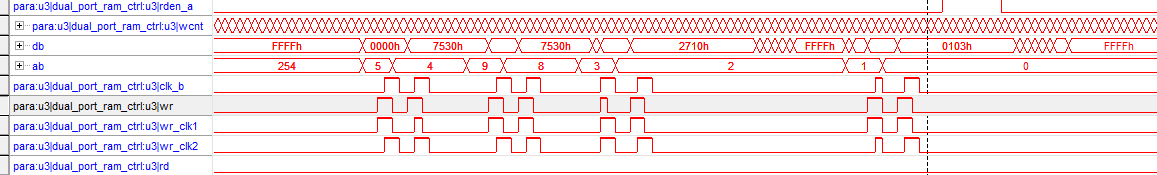

在SignalTap中调试发现有时写入丢失(写入后读出不正常),时序上具体体现为

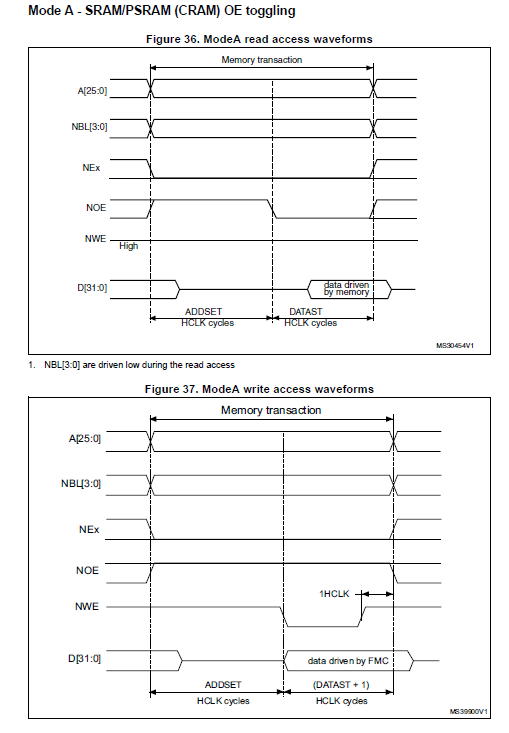

上图中wr信号丢失,造成部分写入失败,wr由ARM输出,与FPGA时钟异步,这里是时钟匹配问题,导致信号丢失,查看STM32F7XX手册关于FMC时序:

图中可以看到, rd与ADDSET时间有关,wr与DATAST-1时间有关,结合前面FMC程序中

Timing.DataSetupTime = 4;

那么wr理论时间是3*HCLK = 3/216MHZ ≈14ns, FPGA时钟周期10ns,理论上wr信号不会丢失。猜想可能是异步信号,同时信号边沿存在斜率(有条件可以用示波器捕捉验证),可能存在信号丢失现象,这里修改FMC时间配置参数。

/* Timing */

Timing.AddressSetupTime = ;

Timing.AddressHoldTime = ;

Timing.DataSetupTime = ;

Timing.BusTurnAroundDuration = ;

Timing.CLKDivision = ;

Timing.DataLatency = ;

Timing.AccessMode = FMC_ACCESS_MODE_A;

修改后发现以上问题得到解决,调试时序如下:

FMC与FPGA双口ram通讯的更多相关文章

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 用嵌入式块RAM IP核配置一个双口RAM

本次设计源码地址:http://download.csdn.net/detail/noticeable/9914173 实验现象:通过串口将数据发送到FPGA 中,通过quartus II 提供的in ...

- 双口RAM,值得研究

在FPGA设计过程中,使用好双口RAM,也是提高效率的一种方法. 官方将双口RAM分为简单双口RAM和真双口RAM. 简单双口RAM只有一个写端口,一个读端口. 真双口RAM分别有两个写端口和两个读端 ...

- 单口 RAM、伪双口 RAM、真双口 RAM、单口 ROM、双口 ROM 到底有什么区别呢?

打开 IP Catalog,搜索 Block Memory Generator,即可看到其 Memory Type 可分为 5 中,分别是单口 RAM(Single Port RAM).伪双口 RAM ...

- 单口RAM、双口RAM、FIFO

单口与双口的区别在于,单口只有一组数据线与地址线,因此读写不能同时进行.而双口有两组数据线与地址线,读写可同时进行.FIFO读写可同时进行,可以看作是双口. 双口RAM分伪双口RAM(Xilin ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 单双口RAM

// Quartus II Verilog Template// Simple Dual Port RAM with separate read/write addresses and// singl ...

- 【知识强化】第三章 存储系统 3.5 双口RAM和多模块存储器

下面我们进入双端口RAM和多模块存储器的学习.这是提高我们的存储器的访存速度的一些措施. 我们之前已经讲过我们的主存和CPU是进行连接的,那么这就导致了一个问题就是说,随着我们现代科技的发展,计算机的 ...

随机推荐

- XSS相关Payload及Bypass的备忘录(上)

翻译学习准备自用,同时分享给大家, 来自于: https://github.com/swisskyrepo/PayloadsAllTheThings/tree/master/XSS%20Injecti ...

- Composer更新与清除缓存命令

一.更新命令 composer self-update --preview 二.清除缓存命令 composer clearcache 操作如下图所示:

- Qt隐式共享机制

1.浅拷贝 浅拷贝-引用类型.浅拷贝是指源对象与拷贝对象共用一份实体,仅仅是引用的变量不同(名称不同),对其中任何一个对象的改动都会影响另外一个对象. 2.深拷贝 而深拷贝-值类型.深拷贝是指源对象与 ...

- vue+element表单校验功能

要实现这个功能其实并不难,element组件直接用就可以, 但是我在使用过程中碰到了几个坑,就记录下来,分享给大家,避免落坑,话不多说,直接上过程...... 表单校验功能: 实现这个功能,总共分 ...

- 02篇ELK日志系统——升级版集群之kibana和logstash的搭建整合

[ 前言:01篇LK日志系统已经把es集群搭建好了,接下来02篇搭建kibana和logstash,并整合完成整个ELK日志系统的初步搭建. ] 1.安装kibana 3台服务器: 192.168.2 ...

- Linux的权限管理操作-Linux从入门到精通第八天(非原创)

文章大纲 一.网络相关概述二.网络相关命令三.项目上线流程(必须掌握)四.学习资料下载五.参考文章 一.网络相关概述 1. 网络发展 1.1 信息传递远古时期,人们就通过简单的语言.壁画等方式交 ...

- 【Linux】yum 安装 JDK

一.查看java的所有版本 yum list java* 二.安装jdk8 yum install java--openjdk.x86_64 三.检查是否安装完成 java -version 四.默认 ...

- Vue中美元$符号的意思与vue2.0中的$router 和 $route的区别

vue的实例属性和方法 除了数据属性,Vue 实例还暴露了一些有用的实例属性与方法.它们都有前缀 $,以便与用户定义的属性区分开来.例如: var data = { a: 1 } var vm = n ...

- MySql数据库中的datediff函数

MySql数据库中的datediff函数:主要是用来返回两个日期之间相隔的天数 一半情况下是大日期在前,小日期在后的 这样写也是能够运行的 要注意查询结果:

- 原生PHP+原生ajax批量删除(超简单),ajax删除,ajax即点即改,完整代码,完整实例

效果图: 建表:company DROP TABLE IF EXISTS `company`;CREATE TABLE `company` ( `id` int(11) NOT NULL AUTO_I ...