基于FPGA Manager的Zynq PL程序写入方案

本文主要描述了如何在Linux系统启动以后,在线将bitstream文件更新到ZYNQ PL的过程及方法。相关内容主要译自xilinx-wiki,其中官网给出了两种方法,分别为Device Tree Overlay和Sysfs interface。由于项目需要,暂只对sysfs interface在线烧录的执行过程作简要介绍和实践,并附有相关的配置脚本文件,更多详情请参照Solution Zynq PL Programming With FPGA Manager。

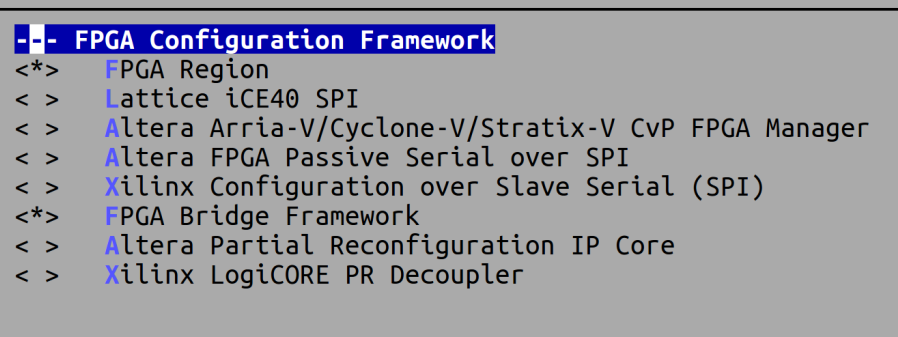

内核配置

为保证FPGA Manager可正常使用,需要按图中配置内核相关选项。(在zynq_defconfig里面,这些选项是默认使能的)

配置 Zynq FPGA Manager:

选择:Device Drivers ---> FPGA Configuration Framework

配置Contiguous Memory Allocator:

CONFIG_CMA

Kernel Features --> Contiguous Memory Allocator

CONFIG_DMA_CMA

Select: Device Drivers --> Generic Driver Options → DMA Contiguous Memory Allocator

工具准备

- bootgen

映像文件准备

- FSBL

- u-boot

- Linux内核映像(uImage)

- 该映像可参考http://www.wiki.xilinx.com/Zynq+Linux创建

- Bin文件

使用Bootgen工具,将.bit文件转换成.bin文件

bootgen -image Full_Bitstream.bif -arch zynq -process_bitstream bin

其中,Full_Bitstream.bif文件应包含下列内容

all:

{

design_1_wrapper.bit /* Bitstream file name */

}

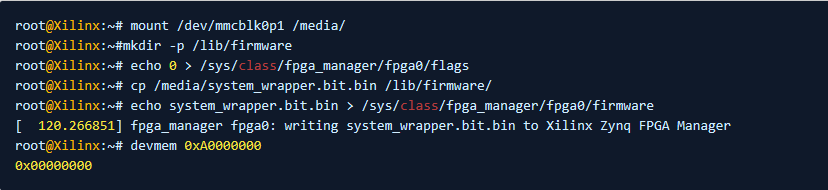

执行过程

设置flags为Full Bitstream模式

echo 0 > /sys/class/fpga_manager/fpga0/flags

通过sysfs提供的接口,下载Bitstream文件到PL

mkdir -p /lib/firmware

cp /media/design_1_wrapper.bit.bin /lib/firmware/

echo design_1_wrapper.bit.bin > /sys/class/fpga_manager/fpga0/firmware

正常输出如下:

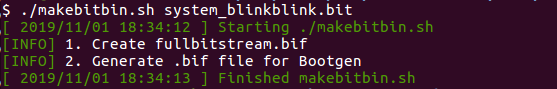

参考脚本

为便于项目使用,笔者将上述过程形成以下两个脚本,其中makebitbin.sh可将.bit文件转换为.bin文件,具体使用方法为:

注意,该脚本执行前需要配置好Bootgen工具才可以正常使用!

脚本如下:

#!/bin/bash

###############################################################################

#

# Copyright (C) 2019 by Luego Zhang <zhanglucc@foxmail.com>

#

# This program is free software; you can redistribute it and/or modify

# it under the terms of the GNU General Public License as published by

# the Free Software Foundation; either version 2 of the License, or

# (at your option) any later version.

#

# Reference:

# https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18841645/Solution+Zynq+PL+Programming+With+FPGA+Manager

################################################################################

# => Force locale language to be set to English. This avoids issues when doing

# text and string processing.

export LC_ALL=C LANGUAGE=C LANG=C # => Help and information

usage() {

printf "

NAME

$(basename ${BASH_SOURCE}) - generating .bin from .bit file using Bootgen SYNOPSIS

$(basename ${BASH_SOURCE}) [option] filename DESCRIPTION

In order to load bitstream files to PL through Linux, we need to get one

type of file with suffix like '.bit.bin'. Run this script and .bin will

be generated with the given file(.bit) using Bootgen.

Please run this script in PC. OPTIONS

--help Display this help message EXAMPLE Version : 191031v1.0

"

exit 0;

}

expr "$*" : ".*--help" > /dev/null && usage # => Setting the development environment variables

if [ ! "${ZN_CONFIG_DONE}" ]; then

printf "\033[31m[ERROR]\033[0m Please source the settings64.sh script first\n"

exit 1

else

# => Setting zynq-7000 development envirionment variables

if [ -f "${ZN_SCRIPTS_DIR}/xilinx/export_xilinx_env.sh" ]; then

source ${ZN_SCRIPTS_DIR}/xilinx/export_xilinx_env.sh

else

error_exit "Could not find file ${ZN_SCRIPTS_DIR}/xilinx/export_xilinx_env.sh"

exit 1

fi

fi ZN_SCRIPT_NAME="$(basename ${BASH_SOURCE})"

ZN_SCRIPT_PATH="$(dirname ${BASH_SOURCE})"

################################################################################

# => The beginning

print_info "[ $(date "+%Y/%m/%d %H:%M:%S") ] Starting ${BASH_SOURCE}\n" # => Check user input is correct

[[ -f $1 ]] || error_exit "$1 not found, please check that the filename is correct\n" echo_info "1. Create fullbitstream.bif "

BIF_FILE=${ZN_SCRIPT_PATH}/fullbitstream.bif

echo "//arch = zynq; split = yes; format = .bit.bin" > ${BIF_FILE}

echo "all:" >>${BIF_FILE}

echo "{" >>${BIF_FILE}

echo " $1" >>${BIF_FILE}

echo "}" >>${BIF_FILE} echo_info "2. Generate .bif file for Bootgen"

bootgen -image fullbitstream.bif -arch zynq -process_bitstream bin -w # => The end

print_info "[ $(date "+%Y/%m/%d %H:%M:%S") ] Finished ${ZN_SCRIPT_NAME}\n"

makebitbin.sh

另一个脚本为load-fpga-image.sh,该脚本应在开发板上运行,具体使用方法为:

将load-fpga-image.sh脚本和上一步生成的blinkblink.bit.bin文件共同copy至开发板的同一目录下,然后按以下方法执行脚本:

./load-fpga-image.sh blinkblink.bit.bin

即可,参考脚本如下:

#!/bin/bash

###############################################################################

#

# Copyright (C) 2019 by Luego Zhang <zhanglucc@foxmail.com>

#

# This program is free software; you can redistribute it and/or modify

# it under the terms of the GNU General Public License as published by

# the Free Software Foundation; either version 2 of the License, or

# (at your option) any later version.

#

# Reference:

# https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18841645/ \

# Solution+Zynq+PL+Programming+With+FPGA+Manager

################################################################################

# => Force locale language to be set to English. This avoids issues when doing

# text and string processing.

export LC_ALL=C LANGUAGE=C LANG=C # => Help and information

usage() {

printf "

NAME

$(basename ${BASH_SOURCE}) - load fullbitstream file to PL through Linux SYNOPSIS

$(basename ${BASH_SOURCE}) [option] bitstream_file DESCRIPTION

Load bitstream file to PL using sysfs interface through Linux.

Be careful the type of bitstream_file is .bit.bin file which is generated

by Bootgen and bitstream_file should be in the same path with the script.

Please run this script on the board! OPTIONS

--help Display this help message EXAMPLE Version : 191031v1.0

"

exit 0;

}

expr "$*" : ".*--help" > /dev/null && usage

#------------------------------------------------------------------------------

# => Check system environment and make sure fpga manager runs well

FPGA_MGR_PATH=/sys/class/fpga_manager/fpga0

if [ ! -d ${FPGA_MGR_PATH} ]; then

printf "\033[31m[ERROR]\033[0m FPGA Manager is not found, please check the driver!"

exit 1

fi # => Check that user input is correct

if [ ! -f "$1" ]; then

printf "\033[31m[ERROR]\033[0m '$1' not found, please check if the file exists\n"

exit 1

fi ZN_SCRIPT_NAME="$(basename ${BASH_SOURCE})"

ZN_SCRIPT_PATH="$(dirname ${BASH_SOURCE})" BITSTREAM="$1"

FPGA_MGR_FLAGS=${FPGA_MGR_PATH}/flags

FPGA_MGR_FIRMWARE=${FPGA_MGR_PATH}/firmware ################################################################################

# => The beginning

echo "\033[32m[ $(date "+%Y/%m/%d %H:%M:%S") ]\033[0m Starting ${ZN_SCRIPT_NAME}\n" # => Set flags for Full Bitstream

echo 0 > $FPGA_MGR_FLAGS

read flag <<<$(cat $FPGA_MGR_FLAGS)

[ "$flag" = "" ] || $(echo "[error] invalid mode, please check ${FPGA_MGR_FLAGS}" && exit 1) # => Loading Bitstream into PL

mkdir -p /lib/firmware/ && cp ./$BITSTREAM /lib/firmware/

echo $BITSTREAM > $FPGA_MGR_FIRMWARE # => The end

printf "\033[32m[ $(date "+%Y/%m/%d %H:%M:%S") ]\033[0m Finished ${ZN_SCRIPT_NAME}\n"

load-fpga-image

基于FPGA Manager的Zynq PL程序写入方案的更多相关文章

- 基于FPGA的按键扫描程序

最近在学习FPGA,就试着写了个按键扫描的程序.虽说有过基于单片机的按键扫描处理经验,对于按键的处理还是有一些概念.但是单片机程序的编写通常都采用C写,也有用汇编,而FPGA却是采用VHDL或者Ver ...

- 基于FPGA的线阵CCD实时图像采集系统

基于FPGA的线阵CCD实时图像采集系统 2015年微型机与应用第13期 作者:章金敏,张 菁,陈梦苇2016/2/8 20:52:00 关键词: 实时采集 电荷耦合器件 现场可编程逻辑器件 信号处理 ...

- S02_CH07_ ZYNQ PL中断请求

S02_CH07_ ZYNQ PL中断请求 7.1 ZYNQ 中断介绍 7.1.1 ZYNQ中断框图 可以看到本例子中PL到PS部分的中断经过ICD控制器分发器后同时进入CPU1 和CPU0.从下面的 ...

- 基于FPGA的SPI FLASH控制器设计

1.SPI FLASH的基本特征 本文实现用FPGA来设计SPI FLASH,FLASH型号为W25Q128BV.支持3种通信方式,SPI.Dual SPI和Quad SPI.FLASH的存储单元无法 ...

- 基于 SailingEase WinForm Framework 开发客户端程序(3:实现菜单/工具栏按钮的解耦及状态控制)

本系列文章将详细阐述客户端应用程序的设计理念,实现方法. 本系列文章以 SailingEase WinForm Framework 为基础进行设计并实现,但其中的设计理念及方法,亦适用于任何类型的客 ...

- 基于FPGA的音频信号的FIR滤波(Matlab+Modelsim验证)

1 设计内容 本设计是基于FPGA的音频信号FIR低通滤波,根据要求,采用Matlab对WAV音频文件进行读取和添加噪声信号.FFT分析.FIR滤波处理,并分析滤波的效果.通过Matlab的分析验证滤 ...

- 基于FPGA的DW8051移植(三)

总结一下问题: 1) http://www.cnblogs.com/sepeng/p/4137405.html 基于FPGA的DW8051移植(一)里面用modelsim观测波形发现程序进入了ida ...

- 基于FPGA的红外遥控解码与PC串口通信

基于FPGA的红外遥控解码与PC串口通信 zouxy09@qq.com http://blog.csdn.net/zouxy09 这是我的<电子设计EDA>的课程设计作业(呵呵,这个月都拿 ...

- 基于FPGA的OLED真彩色动态图像显示的实现

源:基于FPGA的OLED真彩色动态图像显示的实现 作为第3代显示器,有机电致发光器件(Organic Light Emitting Diode,OLED)由于其主动发光.响应快.高亮度.全视角.直流 ...

随机推荐

- Javascript的数据类型(原始类型和引用类型)

1.ECMAScript3中定义了变量可分为原始值和引用值. 原始值:是保存在栈(stack)中的简单数据段:也就是说他们的值是直接存储在变量访问的位置. 引用值:是保存在堆(heap)中的对象,也就 ...

- SVN cornerstone Commit\Update 提示xxx is already Locked解决方法

点击菜单栏“working copy” 点“clean”: 或者,如下图: 右击,点击“clean”,问题解决.

- nginx 常用全局变量

变量 说明 $args 请求中的参数,如www.123.com/1.php?a=1&b=2的$args就是a=1&b=2 $content_length HTTP请求信息里的" ...

- Watcher监听

可以设置观察的操作:exists,getChildren,getData 可以触发观察的操作:create,delete,setData zookeeper观察机制; 服务端只存储事件的信息,客户 ...

- SpringBoot上传文件到本服务器 目录与jar包同级问题

目录 前言 原因 实现 不要忘记 最后的封装 Follow up 前言 看标题好像很简单的样子,但是针对使用jar包发布SpringBoot项目就不一样了.当你使用tomcat发布项目的时候,上传 ...

- 实现mysql的读写分离(mysql-proxy)____2

mysql-proxy简介 MySQL读写分离是指让master处理写操作,让slave处理读操作,非常适用于读操作量比较大的场景,可减轻master的压力. 使用mysql-proxy实现mysql ...

- 冰多多团队-第七次scrum例会

冰多多团队-第七次Scrum会议 工作情况 团队成员 已完成任务 待完成任务 zpj 接入IAT模块 debug, IAT 牛雅哲 调研科大讯飞SDK中其他模块,寻找符合我们的需求的部分,将接口更换成 ...

- 剑指offer:表示数值的字符串

题目描述: 请实现一个函数用来判断字符串是否表示数值(包括整数和小数).例如,字符串"+100","5e2","-123","3. ...

- poi导出word表格

代码如下: package com.ksource.pwlp.util; import java.io.FileOutputStream; import java.math.BigInteger; i ...

- linux , nginx: 封禁IP的办法【转】

今天,我们的一台服务器出了问题: 被若干IP地址访问某个接口,该接口会发送短信. 所以,我们可以做两件事: 1. nginx的层面封IP . 2 linux server的层面封IP 先看ngin ...