FPGA内部硬件结构简介

我们知道FPGA内部有很多可供用户任意配置的资源,其中包括:可编程逻辑、可编程I/O、互连线、IP核等资源,很多学过数字电路的人都知道与或非门可以构成几乎所有的数字电路,但是FPGA内部最基本的主要单元并不是这些与或非门,而是由无数个查找表(Look Up Tabe,简称为LUT)和寄存器构成。

虽然FPGA的内部结构对于初学者来说是云里雾里,一头雾水,但是了解FPGA的内部结构能让我们更好的理解FPGA设计过程中我们所编写的代码和硬件是怎样的一个映射关系,从而更深刻理解FPGA和单片机、ARM的不同。当我们对FPGA内部结构了解透彻后,就可以把FPGA的设计了如指掌,才能有助于进一步优化我们的设计,优化好的设计能使我们设计的整个系统跑的更快、更加节省资源、功耗更低,稳定性更好。

我们选用的是CycloneIV系列的EP4CE10F17C8,很多入门开发板一般都配置的这款芯片,其主要资源如下图所示。

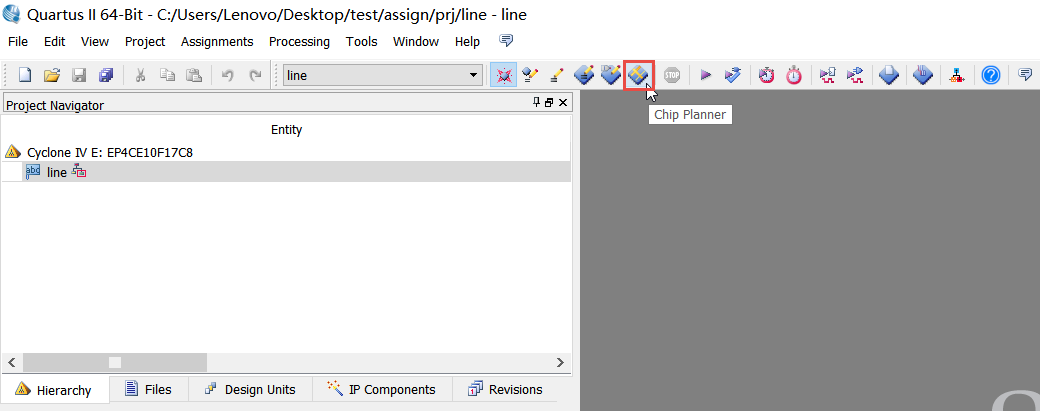

首先我们来认识一下FPGA内部的一些资源。点击下图所示图标打开Chip Planner来查看这款FPGA芯片的版图模型。

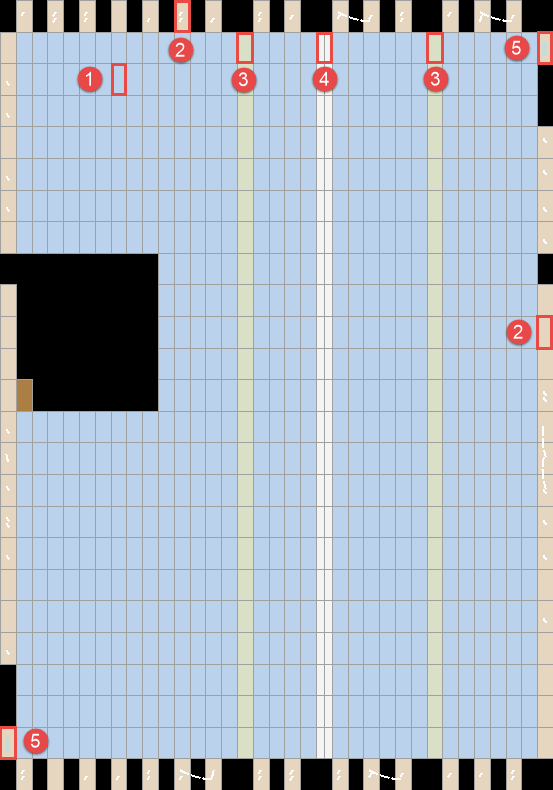

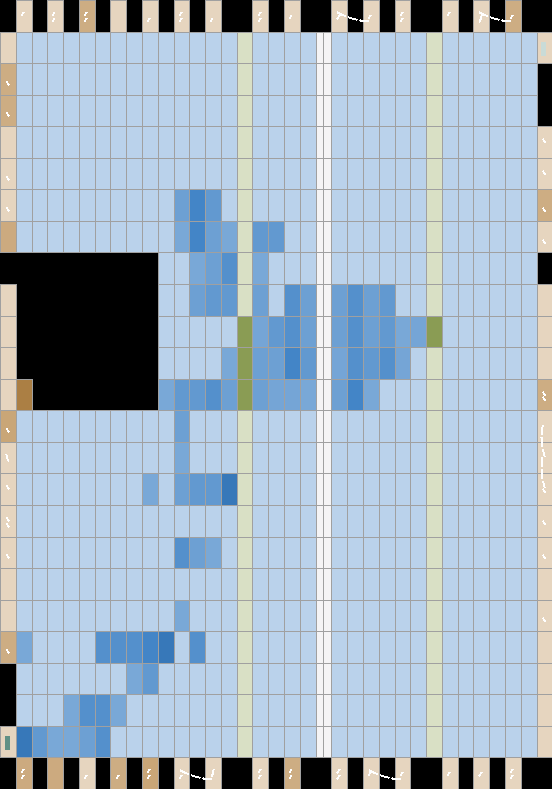

打开后的版图模型如下图所示,第一张图是未进行布局不线的图,因为资源未被使用所以都是浅色。第二张图是已经布局布线后的图,也就是已经将使用的资源映射到了版图模型上(只有全编译后才能看到映射效果),其中深色表示该资源已经被使用,而颜色越深的地方表示资源利用率越高。黑色区域为一些固定功能的资源或没有资源,用户不可对其进行任意配置。

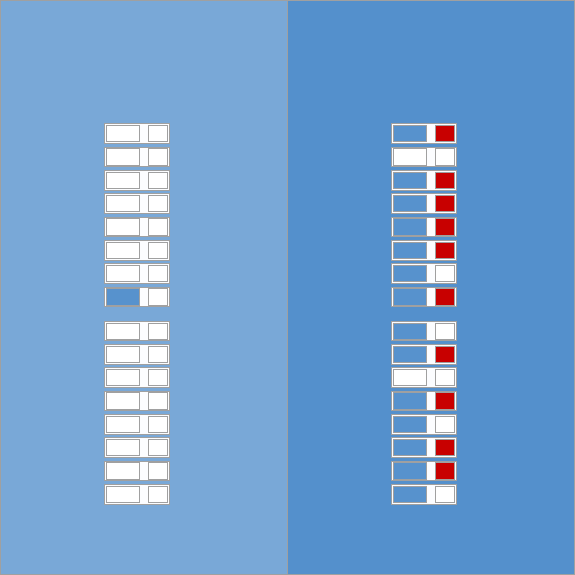

①逻辑阵列块(Logic Array Block,也简称为LAB):每个LAB由16个LE(Logic Element)组成,下图是两个已经映射资源后的LAB,资源利用率不同的LAB其颜色深浅也有所差异(左边使用的资源少,颜色就浅;右边使用的资源多,颜色就深)。

放大后的LE如下图所示,每个LE由左边一个蓝色LUT和右边一个红色寄存器组成。整个芯片中共有10320个LE。

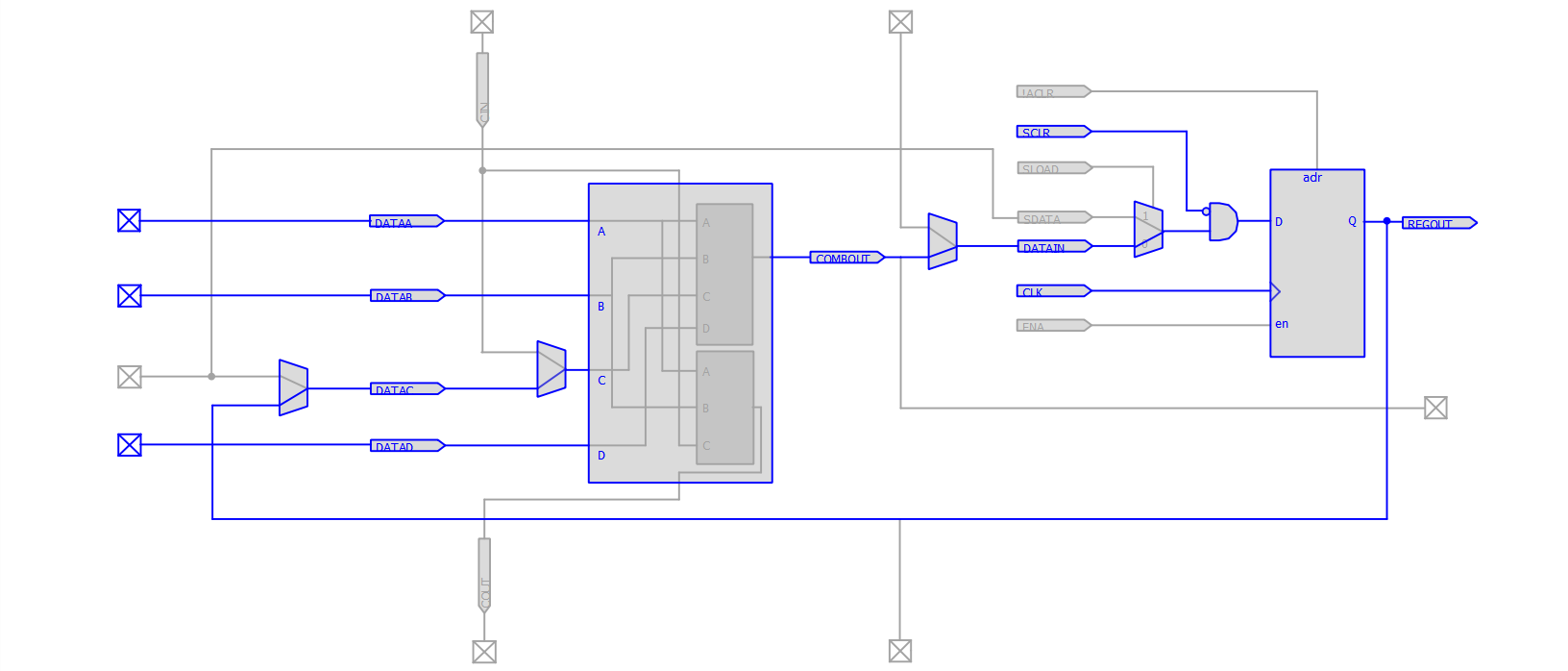

双击其中一个LE可以观察到其大致的内部结构(内部结构只有被使用才能够双击打开查看),我们可以看到主要的两个部分,一是左边的4输入LUT,另一个是可编程寄存器,还包括一些选择器、与门等辅助逻辑电路。(蓝色高亮的部分是已经使用的资源,未高亮灰色的部分是未被使用的资源)。

②用户可编程I/O(User I/Os,也被称为IOE):可编程I/O资源分布在整个芯片的四周。该芯片共有256个管脚,除去一些固定功能的管脚,可供用户任意配置的管脚资源只有180个,下图是其中一个可编程I/O单元,里面又包含三个最小单元(每个可编程I/O单元中的最小单元个数不固定,有的包含两个,也有的包含四个)。

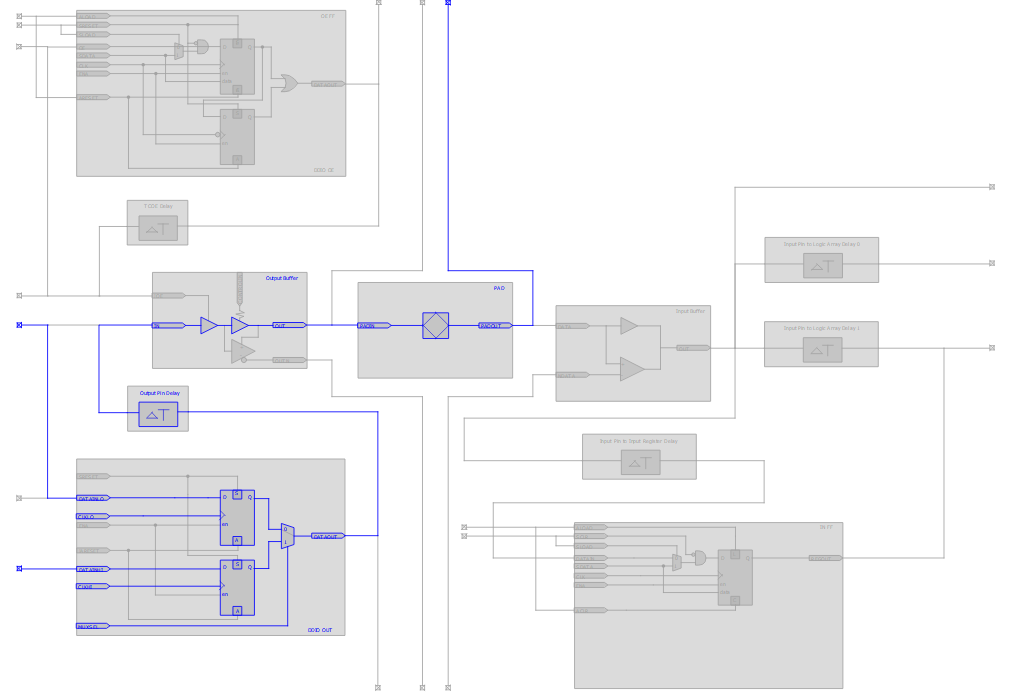

下图是可编程I/O最小单元内部结构图,包括双向I/O缓冲器、OE寄存器、对齐寄存器、同步寄存器、DDR输出寄存器、三态门、延时模块等组成。

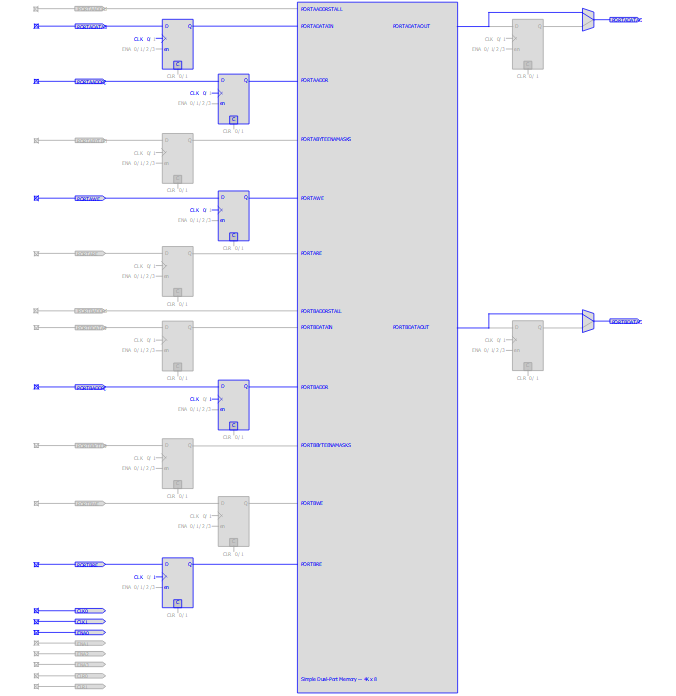

③嵌入式存储单元(Memory Bits,也被称为Block RAM或简称为BRAM):该部分资源主要用于生成RAM、ROM、FIFO、移位寄存器,在存储较多数据或作跨时钟域处理时常用到。该芯片共有423936bit存储单元,并以每9Kbit容量为一个块,共有46个,下图所示为一个M9K的RAM块。相对于LUT构成的分布式RAM(Distribute RAM,简称为DRAM),这种专门的存储单元容量更大,从而避免LUT资源的浪费。

下图是一个M9K内部结构图。由输入输出寄存器和一个RAM块构成。

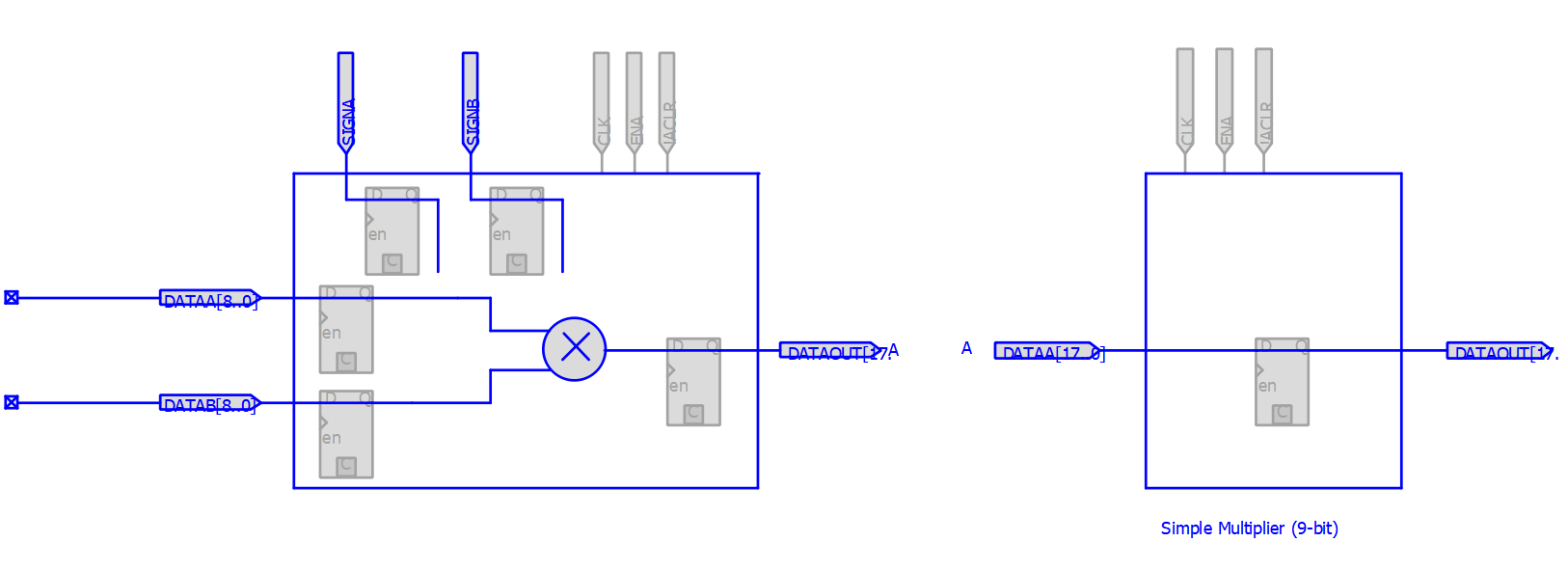

④嵌入式乘法单元(Embedded multiPlier 9-bit elements,也称为DSP块):该单元主要用于各种复杂的数学运算,乘法、除法以及常用的功能函数如:有限冲激响应滤波器(FIR),无限冲击响应滤波器(IIR),快速傅里叶变换(FFT),离散余弦变换(DCT)等时会消耗很多逻辑资源,而FPGA中的LUT和寄存器资源有限,这时候使用嵌入式乘法单元这部分资源就不会造成逻辑资源的浪费。该芯片共有46个DSP块,成列式分布在芯片的中间位置,下图为一对DSP块资源。

下图是嵌入式乘法器单元DSP块的内部结构图。包含输入输出寄存器和一个乘数块。

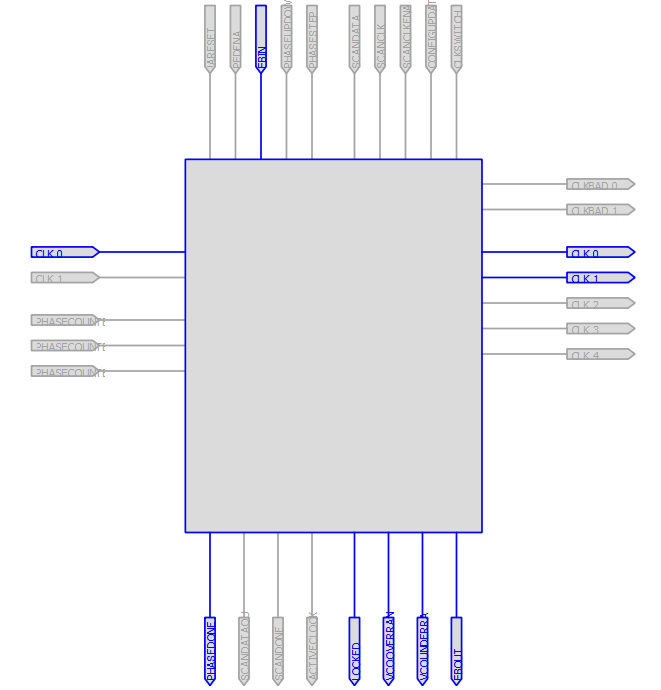

⑤锁相环(Phase Lock Loop,也简称为PLL):该芯片一共有两个锁相环,一个在右上角处附近,一个在左下角附近。PLL的参考时钟输入都是由专用时钟管脚上的晶振进来的,用于时钟的倍频、分频,以及相位、占空比调制。PLL出来的时钟都会连接到全局时钟网络上,以保证时钟的质量,减小时钟偏斜(Skew)和抖动(Jitter)。

下图是锁相环内部的结构图,每个锁相环可以分出五个同源时钟信号。

FPGA内部硬件结构简介的更多相关文章

- 硬盘内部硬件结构和工作原理详解[zz]

一般硬盘正面贴有产品标签,主要包括厂家信息和产品信息,如商标.型号.序列号.生产日期.容量.参数和主从设置方法等.这些信息是正确使用硬盘的基本依据,下面将逐步介绍它们的含义. 硬盘主要由盘体.控制电路 ...

- FPGA芯片内部硬件介绍

FPGA芯片内部硬件介绍 FPGA(Filed programmable gate device):现场可编程逻辑器件 FPGA基于查找表加触发器的结构,采用SRAM工艺,也有采用flash或者反熔丝 ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

- 论山寨手机与Android联姻 【9】SmartPhone的硬件结构

如何区别智能手机(SmartPhone)与功能手机(FeaturePhone)? 有一种观点认为,智能手机本质上是功能手机与便携式电脑(Laptop PC)的结合.功能手机的功能受限于制造厂商的预制, ...

- CPU的硬件结构和汇编语言

(已更正) 这个问题包括CPU的硬件结构和汇编语言的范畴. 这里梳理一下. 首先, 题主"李建国"自问自答的部分说的是正确的, CPU的指令集是软件与CPU这两个层级之间的接口, ...

- FPGA内部动态可重置PLL讲解(一)

SDRAM驱动需要两个时钟,一个是控制时钟,一个是驱动时钟,这两个时钟有一个相位差,如何产生高精度的时钟是SDRAM能够正常工作的关键,采用FPGA内部动态可重置PLL生成SDRAM所需要的时钟频率. ...

- FPGA 内部详细架构你明白了吗?

FPGA 芯片整体架构如下所示,大体按照时钟域划分的,即根据不同的工艺.器件速度和对应的时钟进行划分: FPGA 内部详细架构又细分为如下六大模块: 1.可编程输入输出单元(IOB)(Input Ou ...

- 【转】FPGA内部小数计算

FPGA内部计算小数 [转载] 谓定点小数,就是小数点的位置是固定的.我们是要用整数来表示定点小数,由于小数点的位置是固定的,所以就没有必要储存它(如果储存了小数点的位置,那就是浮点数了).既然没有 ...

- 【CUDA学习】GPU硬件结构

GPU的硬件结构,也不是具体的硬件结构,就是与CUDA相关的几个概念:thread,block,grid,warp,sp,sm. sp: 最基本的处理单元,streaming processor 最 ...

随机推荐

- 详解Linux 安装 JDK、Tomcat 和 MySQL(图文并茂)

https://www.jb51.net/article/120984.htm

- 看了就会的VScode给C++的配置编译环境(Visual Studio Code)

我看了网上的大佬们配的我是在是看不懂啊?我是一个小白啊?这太难了,这阻挡不了我,想使用这很骚的IDE,于是在不断的摸索下,终于配置成功,小白们也不用慌,这次非常简单.一定可以的. 1.下载 VS Co ...

- ubuntu 下修改MySQL 的root用户密码

环境:Ubuntu 16.04 : Mysql 5.7问题:mysql root登录密码 忘记了..忘记了..忘..了 1.登录MySQL $ mysql -u root -p 输入密码,如果登录 ...

- 简单使用媒体查询@media

@media 可以针对不同的屏幕尺寸设置不同的样式,特别是如果你需要设置设计响应式的页面,@media 是非常有用的. 那媒体查询该如何使用呢? 一.铺垫 1.首先我们在使用 @media 的时候需要 ...

- H - Fire CodeForces - 864E 01背包

https://codeforces.com/problemset/problem/864/E 这个题目要把这个按照物品毁灭时间进行排序,如果时间短就要排在前面,这个是因为要保证之后的物品的拯救不会影 ...

- Tunnel Warfare 线段树 区间合并|最大最小值

B - Tunnel WarfareHDU - 1540 这个有两种方法,一个是区间和并,这个我个人感觉异常恶心 第二种方法就是找最大最小值 kuangbin——线段树专题 H - Tunnel Wa ...

- Vuel路由跳转动画

1.App.vue中添加 <transition :name="animate"> <router-view/> </transition> e ...

- Python 爬取豆瓣电影Top250排行榜,爬虫初试

from bs4 import BeautifulSoup import openpyxl import re import urllib.request import urllib.error # ...

- ssh框架整合时的延迟加载问题(no session问题)的分析以及解决方案

当我们整合完三大框架,并采用hibernate的延迟加载方案时,会出现如下的异常: 现在对这个异常进行分析,如下图所示(模拟通过id查询用户信息的过程): 上图分析了为什么会出现no session的 ...

- js函数传递参数的方式------传值与传递指针

原则: 1. 基本类型:传值 2. 对象:传递指针 应用场景之一: 用jq选择器获取某个div后(例如:element),准备进行某些修改,之后添加到页面中去. 采取例一的方式,append后发现修改 ...