强化版按键消抖Verilog实现

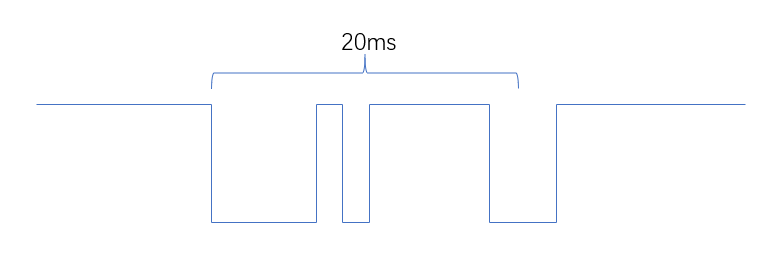

介绍:按键的物理结构导致了会有抖动现象的出现,判断按键是否真正按下,需要把抖动的部分滤波。根据经验可知,抖动一般在20ms内,所以常规的消抖方法是从变化沿出现时刻开始,延时20ms后判断按键的状态。这种方法适用范围不广,因为精度不高(如下图,会判断出错)。

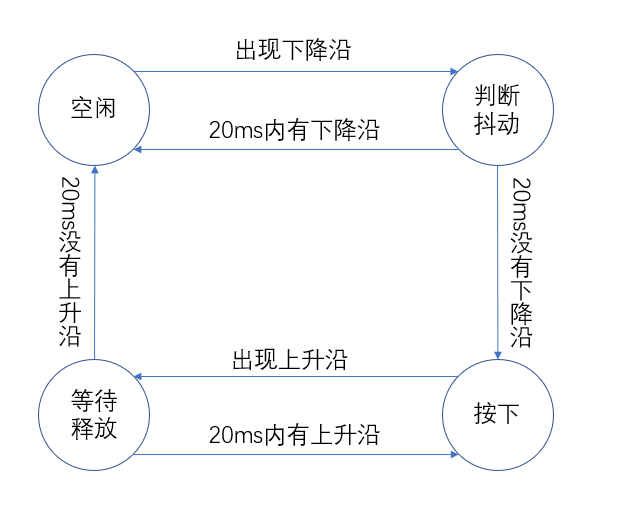

本次设计通过状态机的设计提高了按键消抖的性能,具体思路如图:

学习:

①testbench文件不会综合成电路,所以可以适用较多的高级语句。

②学会看IEEE手册,里面有很完整的语法讲解。想查看某个语句的语法,可以直接 Ctrl+F 搜关键字 ,找的比较快

新语法:

①random function:产生一个随机数

rand = $random(seed) 则rand为一个随机数,seed一般为1,2等,不影响结果,可以直接省略为 rand = $random 。

rand = $random % range 则rand为在 - range ~ +range-1 内的随机数 。%是取余运算

rand = {$random } % range 则rand为在 0 ~ +range-1 内的随机数 。{}是取绝对值运算。

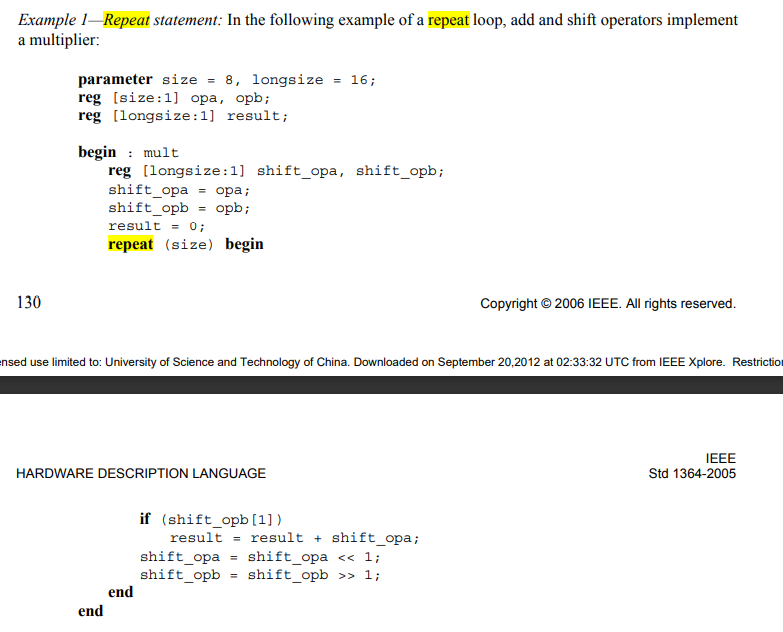

② repeat 重复,循环

repeat(n)重复n次,下面跟begin-end语句,重复n次begin-end 。

代码实现:

module buttopn_debounde(

clk,

tx,

reset,

bd_tx

);

input tx ;

input clk ;

input reset ;

output reg bd_tx ; reg [1:0]edge_detect_regist;

always@(posedge clk or negedge reset)//输入信号的移位寄存器

begin

if (!reset)

edge_detect_regist <= 2'd0 ;

else

begin

edge_detect_regist[0] <= tx ;

edge_detect_regist[1] <= edge_detect_regist[0] ;

//等效于 edge_detect_regist <={ edge_detect_regist[0] , tx }

end

end wire neg_edge , pos_edge ;

assign neg_edge = ( edge_detect_regist == 2'b10 ) ? 1 : 0 ;//下降沿

assign pos_edge = ( edge_detect_regist == 2'b01 ) ? 1 : 0 ;//上升沿 parameter delay = 20000000 / 20 ;//抖动20ms reg [3:0]state ;

reg [19:0]counter1 ;

always@(posedge clk or negedge reset)

begin

if (!reset)

state <= 4'd0 ;//空闲态

else if ( ( neg_edge ) && ( state == 4'd0 ) )

state <= 4'd1 ;//按下消抖态

else if ( ( state == 4'd1 ) && (( delay - 1) > counter1 ) && ( pos_edge ) )

state <= 4'd0 ;//空闲态

else if ( ( state == 4'd1 ) && (( delay - 1) <= counter1 ) )

state <= 4'd2 ;//按下态

else if ( ( pos_edge ) && ( state == 4'd2 ) )

state <= 4'd3 ;//释放消抖态

else if ( ( state == 4'd3 ) && (( delay - 1) > counter1 ) && ( neg_edge ) )

state <= 4'd2 ;//按下态

else if ( ( state == 4'd3 ) && (( delay - 1) <= counter1 ) )

state <= 4'd0 ;//空闲态

end always@(posedge clk or negedge reset)

begin

if (!reset)

counter1 <= 5'd0 ;

else if ( ( neg_edge ) || ( pos_edge ) )

counter1 <= 5'd0 ;

else if ( ( state == 4'd1 ) && (! neg_edge ) && (! pos_edge ) )

counter1 <= counter1 + 1'd1 ;

else if ( ( state == 4'd3 ) && (! neg_edge ) && (! pos_edge ) )

counter1 <= counter1 + 1'd1 ;

end always@(posedge clk or negedge reset)

begin

if (!reset)

bd_tx <= 1'd1 ;//空闲态

else

case(state)

0:bd_tx <= 1'd1 ;

1:bd_tx <= 1'd1 ;

2:bd_tx <= 1'd0 ;

3:bd_tx <= 1'd0 ;

endcase

end reg pre_sign ;

always@(posedge clk or negedge reset)

begin

if (!reset)

pre_sign <= 1'd1 ;//空闲态

else if( ( state == 4'd1 ) && (( delay - 1) <= counter1 ) )

pre_sign <= 1'd0 ;

else if ( state == 4'd2 )

pre_sign <= 1'd1 ;

end reg release_sign ;

always@(posedge clk or negedge reset)

begin

if (!reset)

release_sign <= 1'd0 ;//空闲态

else if( ( state == 4'd3 ) && (( delay - 1) <= counter1 ) )

release_sign <= 1'd1 ;

else if ( state == 4'd0 )

release_sign <= 1'd0 ;

end endmodule

`timescale 1ns / 1ns

module button_debounce_tb(

); reg clk ;

reg tx ;

reg reset ;

wire bd_tx ; buttopn_debounde

#(

.delay(100)

)

buttopn_debounde_sim(

clk,

tx,

reset,

bd_tx

); initial clk = 1 ;

always #10 clk = ! clk ;

initial

begin

reset = 1'd0 ;

tx = 1'd1 ;

#201 ;

reset = 1'd1 ;

#200 ;

tx = 1'd0 ;#500 ;

tx = 1'd1 ;#400 ;

tx = 1'd0 ;#200 ;

tx = 1'd1 ;#100 ;

tx = 1'd0 ;#2100;

#2000 ;

tx = 1'd1 ;#100 ;

tx = 1'd0 ;#200 ;

tx = 1'd1 ;#1900;

tx = 1'd0 ;#200 ;

tx = 1'd1 ;#2000;

#2000;

$stop;

end

endmodule

`timescale 1ns / 1ns

module button_debounce_tb_optimization(

); reg clk ;

reg tx ;

reg reset ;

wire bd_tx ; buttopn_debounde

#(

.delay(100)

)

buttopn_debounde_sim1(

clk,

tx,

reset,

bd_tx

); initial clk = 1 ;

always #10 clk = ! clk ;

initial

begin

reset = 1'd0 ;

tx = 1'd1 ;

#200 ;

reset = 1'd1 ;

#2000 ;

press_generator(1) ;

#1000;

press_generator(1) ;

#10000;

press_generator(1) ;

#10000;

$stop;

end reg [31:0]rand ;

task press_generator;

input reg seeds;

begin

tx = 1 ;

# 200 ;

tx = ! tx ; //0 repeat(6)

begin

rand = {$random(seeds)} % ( 2000 );

# rand ;

tx = ! tx ;

end #10000; repeat(5)

begin

tx = ! tx ;

rand = {$random(seeds)} % ( 2000 );

# rand ;

end

#10000;

end

endtask

endmodule

强化版按键消抖Verilog实现的更多相关文章

- 按键消抖-----verilog

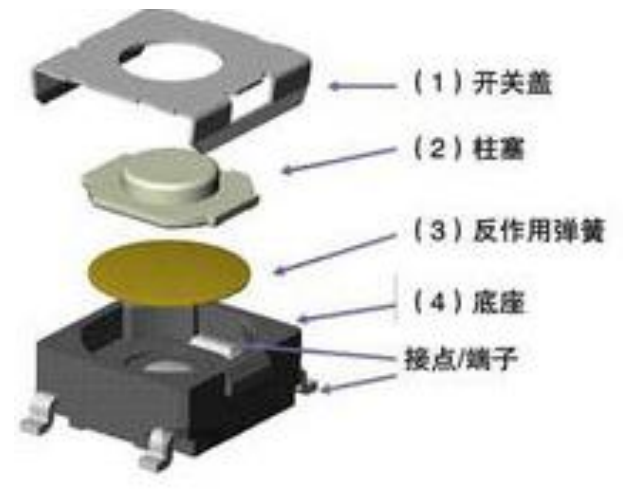

实际系统中常用的按键大部分都是轻触式按键,如下图所示.该按键内部由一个弹簧片和两个固定触点组成,当弹簧片被按下,则两个固定触点接通,按键闭合.弹簧片松开,两个触点断开,按键也就断开了.根据这种按键的机 ...

- 按键消抖VERILOG实现

对于消抖,有很多种写法.今天分享一下我的写法. 基本思路: 1. 看图 图1 ...

- Verilog HDL那些事_建模篇笔记(实验三:按键消抖)

实验三:按键消抖 首先将按键消抖功能分成了两个模块,电平检查模块和10ms延迟模块.电平检测模块用来检测按键信号的变化(是否被按下),10ms延迟模块用来稳定电平检查模块的输入,进而稳定按键信号,防止 ...

- 【代码】verilog之:按键消抖

此模块完美运行 /*-------------------------------------------------------------------------------------- -- ...

- 09A-独立按键消抖实验01——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习状态机的设计思想并以此为基础实现按键消抖 2.单bit异步信号同步化以及边沿检测 3.在激励文件中学会使用随机数发生函数$random 4.仿真模 ...

- FPGA学习笔记(八)—— 状态机设计实例之独立按键消抖

###### [该随笔中部分内容转载自小梅哥] ######### 独立按键消抖自古以来在单片机和FPGA中都是个不可避免的问题,首先,解释一下什么叫做按键抖动,如图,按键在按下和松开的那个瞬间存在大 ...

- 09B-独立按键消抖实验02——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习按键的设计 2.用模块化设计的方式实现每次按下按键0,4个LED显示状态以二进制加法格式加1,每次按下按键1,4个LED显示状态以二进制加法格式减 ...

- 基于FPGA的数字秒表(数码管显示模块和按键消抖)实现

本文主要是学习按键消抖和数码管动态显示,秒表显示什么的,个人认为,拿FPGA做秒表真是嫌钱多. 感谢 感谢学校和至芯科技,笔者专业最近去北京至芯科技培训交流了一周.老师的经验还是可以的,优化了自己的代 ...

- 按键消抖——task任务和仿真平台搭建

一.按键抖动原理 按键抖动原理:按键存在一个反作用弹簧,因此当按下或者松开时均会产生额外的物理抖动,物理抖动会产生电平的抖动. 消抖方法:一般情况下,抖动的总时间会持续20ms以内,按下按键后,等20 ...

随机推荐

- 使用allatori混淆代码

引言 为了保密需要,我们开发出来的程序在实际部署之前,需要先将jar包的代码进行混淆,让用户使用反编译也无法获得源码. allatori就是这样一个混淆java jar包代码的工具. 操作步骤 Ste ...

- Linux网卡绑定bond0-实验

虚拟机添加网卡 ip addr 查看新增的网卡是否读取 添加bonding接口 [root@centos8~]$nmcli con add type bond con-name mybond0 ifn ...

- 项目实战:rsync+sersync实现数据实时同步

一.组网介绍 本次实验使用两台主机: qll251 角色:Rsync server + Sersync server qll252 角色: Rsync client 本次实验采用CentOS7.7系统 ...

- Linux中几个正则表达式的用法

开源Linux 长按二维码加关注~ 上一篇:盘点提高国内访问Github的速度的9种方案 正则表达式就是用于匹配每行输入的一种模式,模式是指一串字符序列.拥有强大的字符搜索功能.也非常方便的搜索过滤出 ...

- DH问题汇总

本节内容主要转载于:弄清楚DL,D-H,CDH problem,CDH assumption,DDH,BDDH,BCDH. DLP(Discrete Logarithm Problem) 在乘法群\( ...

- 机器学习实战-k近邻算法

写在开头,打算耐心啃完机器学习实战这本书,所用版本为2013年6月第1版 在P19页的实施kNN算法时,有很多地方不懂,遂仔细研究,记录如下: 字典按值进行排序 首先仔细读完kNN算法之后,了解其是用 ...

- vue大型电商项目尚品汇(前台篇)day02

现在正式回归,开始好好做项目了,正好这一个项目也开始慢慢的开始起色了,前面的准备工作都做的差不多了. 而且我现在也开始慢慢了解到了一些项目才开始需要的一些什么东西了,vuex.router这些都是必备 ...

- 渗透:aircrack-ng

ircrack- NG是一个完整的工具来评估Wi-Fi网络安全套件,功能包括: 监控:数据包捕获和导出数据到文本文件,以供第三方工具进一步处理. 攻击:通过数据包注入回放攻击,去认证,伪造接入点等. ...

- C# 类继承中的私有字段都去了哪里?

最近在看 C++ 类继承中的字段内存布局,我就很好奇 C# 中的继承链那些 private 字段都哪里去了? 在内存中是如何布局的,毕竟在子类中是无法访问的. 一:举例说明 为了方便讲述,先上一个例子 ...

- CabloyJS一站式助力微信、企业微信、钉钉开发 - 企业微信篇

前言 现在软件开发不仅要面对前端碎片化,还要面对后端碎片化.针对前端碎片化,CabloyJS提供了pc=mobile+pad的跨端自适应方案,参见:自适应布局:pc = mobile + pad 在这 ...