[转帖]CPU 的缓存

缓存这个词想必大家都听过,其实缓存的意义很广泛:电脑整机最大的缓存可以体现为内存条、显卡上的显存就是显卡芯片所需要用到的缓存、硬盘上也有相对应的缓存、CPU有着最快的缓存(L1、L2、L3缓存等),缓存就是数据交换的缓冲区(称作Cache)。缓存往往都是RAM(断电即掉的非永久储存),它们的作用就是帮助硬件更快地响应。我们今天就来讲一下,关于最快的缓存——CPU缓存的那些事。

CPU缓存是什么?

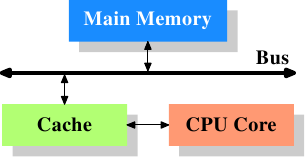

CPU缓存的定义为CPU与内存之间的临时数据交换器,它的出现是为了解决CPU运行处理速度与内存读写速度不匹配的矛盾——缓存的速度比内存的速度快多了。CPU缓存一般直接跟CPU芯片集成或位于主板总线互连的独立芯片上。(现阶段的CPU缓存一般直接集成在CPU上)CPU往往需要重复处理相同的数据、重复执行相同的指令,如果这部分数据、指令CPU能在CPU缓存中找到,CPU就不需要从内存或硬盘中再读取数据、指令,从而减少了整机的响应时间。

CPU-缓存-主内存图示,图片来自:CPU Caches

CPU缓存速度和内存速度差多少?

我们来简单地打个比方:如果CPU在L1一级缓存中找到所需要的资料要用的时间为3个周期左右,那么在L2二级缓存找到资料的时间就要10个周期左右,L3三级缓存所需时间为50个周期左右;如果要到内存上去找呢,那就慢多了,可能需要几百个周期的时间。

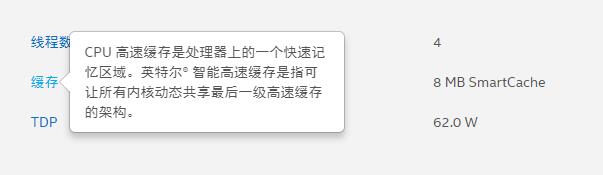

I3-8300处理器技术规格

对CPU缓存有一定了解了吗,让我们再深入一点。以Intel为例,Intel官网上产品-处理器界面内对缓存的定义为:“CPU高速缓存是处理器上的一个快速记忆区域。英特尔智能高速缓存(SmartCache)是指可让所有内核动态共享最后一级高速缓存的架构。”这里就提及到了最后一级高速缓存的概念,即为CPU缓存中的L3(三级缓存),那么我们继续来解释一下什么叫三级缓存,分别又是指哪三级缓存。

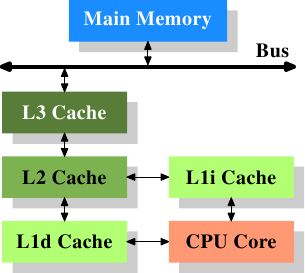

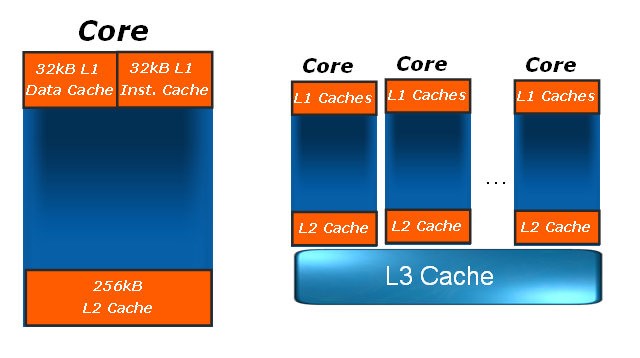

CPU-缓存-主内存图示,图片来自:CPU Caches

三级缓存(L1、L2、L3)是什么?

以近代CPU的视角来说,三级缓存(包括L1一级缓存、L2二级缓存、L3三级缓存)都是集成在CPU内的缓存,它们的作用都是作为CPU与主内存之间的高速数据缓冲区,L1最靠近CPU核心;L2其次;L3再次。运行速度方面:L1最快、L2次快、L3最慢;容量大小方面:L1最小、L2较大、L3最大。CPU会先在最快的L1中寻找需要的数据,找不到再去找次快的L2,还找不到再去找L3,L3都没有那就只能去内存找了。L1、L2、L3可以说是各有特点,下面我们就分开来讲一下。

一级缓存(L1 Cache)

一级缓存这个名词出现应该是在Intel公司Pentium处理器时代把缓存开始分类的时候,当时在CPU内部集成的CPU缓存已经不能满足整机的性能需求,而制造工艺上的限制不能在CPU内部大幅提高缓存的数量,所以出现了集成在主板上的缓存,当时人们把CPU内部集成的CPU缓存成为一级缓存,在CPU外部主板上的缓存称为二级缓存。

Intel Pentium 4

而一级缓存其实还分为一级数据缓存(Data Cache,D-Cache,L1d)和一级指令缓存(Instruction Cache,I-Cache,L1i),分别用于存放数据及执行数据的指令解码,两者可同时被CPU访问,减少了CPU多核心、多线程争用缓存造成的冲突,提高了处理器的效能。一般CPU的L1i和L1d具备相同的容量,例如I7-8700K的L1即为32KB+32KB。

二级缓存(L2 Cache)

随着CPU制造工艺的发展,本来处于CPU外部的二级缓存也可以轻易地集成进CPU内部,这种时候再用缓存是否处于CPU内部来判断一二级缓存已经不再确切。集成进CPU的L2二级缓存运行速率渐渐可以跟上CPU的运行速度了,,其主要作用为当CPU在L1中没读取到所需要的数据时再把数据展示给CPU筛选(CPU未命中L1的情况下继续在L2寻求命中,缓存命中的工作原理我们稍后再讲)。

L2二级缓存比L1一级缓存的容量要更大,但是L2的速率要更慢,为什么呢?首先L2比L1要更远离CPU核心,L1是最靠近CPU核心的缓存,CPU需要读取L2的数据从物理距离上比L1要更远;L2的容量比L1更大,打个简单的比喻,在小盒子里面找东西要比在大房间里面找要方便快捷。这里也可以看出,缓存并非越大越好,越靠近CPU核心的缓存运行速率越快越好,非最后一级缓存的缓存容量自然是够用即可。

Core Duo酷睿双核处理器

L2二级缓存实际上就是L1一级缓存跟主内存之间的缓冲器,在2006年的时间点上,Intel和AMD当家在售的几款处理器可以看出他们对最后一级缓存不同的见解:Intel Core Duo不同于它的前辈Pentium D、EE,采用了双核心共享的2M L2二级缓存,是属于当时最先二级缓存架构,即“Smart Cache”共享缓存技术,这种技术沿用到以后的Intel推出的所有多核心处理器上;而AMD Athlon 64 X2处理器则是每个CPU核心都具备独立的二级缓存,Manchester核心的处理器为每核心512KB、Toledo核心为每核心1MB,两个核心之间的缓存的数据同步是通过CPU内置的SRI(系统请求接口)控制,这样的数据延迟及占用资源情况都要比Intel的Pentium D、EE核心要好,但还是比不上Core为代表的Smart Cache缓存共享。

三级缓存(L3 Cache)

最初出现L3三级缓存的应该是AMD的K6-III处理器,当时受限于制造工艺,L3只能集成在主板上。然后Intel首次出现L3三级缓存的是Itanium安腾服务器处理器,接着就是P4EE和至强MP。L3三级缓存的出现其实对CPU性能提升呈一个爬坡曲线——L3从0到2M的情况CPU性能提升非常明显,L3从2M到6M提升可能就只有10%不到了,这是在近代CPU多核共享L3的情况下;当L3集成进CPU正式成为CPU内部缓存后,CPU处理数据时只有5%需要在内存中调用数据,进一步地减少了内存延迟,使系统的响应更为快速。

Intel Nehalem L3 SmartCache示意图

同理,L3即为L2与主内存之间的缓冲器,主要体现在提升处理器大数据处理方面的性能,对游戏表现方面有较大的帮助。那么也许有人就会问了,是不是选择CPU的时候看准L3买,哪个CPU的L3大就买哪个?非也,只有同架构的情况下这种比较才具有意义,先举个比较久远的例子:Intel具备1MB L3的Xeon MP处理器仍然不是AMD没有L3的皓龙处理器对手,再来个现有的:Intel I7-8700K 12MB L3和AMD Threadripper 1950X 32MB L3相比,自然是32MB比12MB大,但是平均下来也是一个核心2MB L3,性能就见仁见智了。

CPU缓存是怎样帮助CPU工作的呢

知道了L1、L2、L3的由来,我们再深入地了解一下CPU缓存是怎么帮助CPU提高工作效率的。

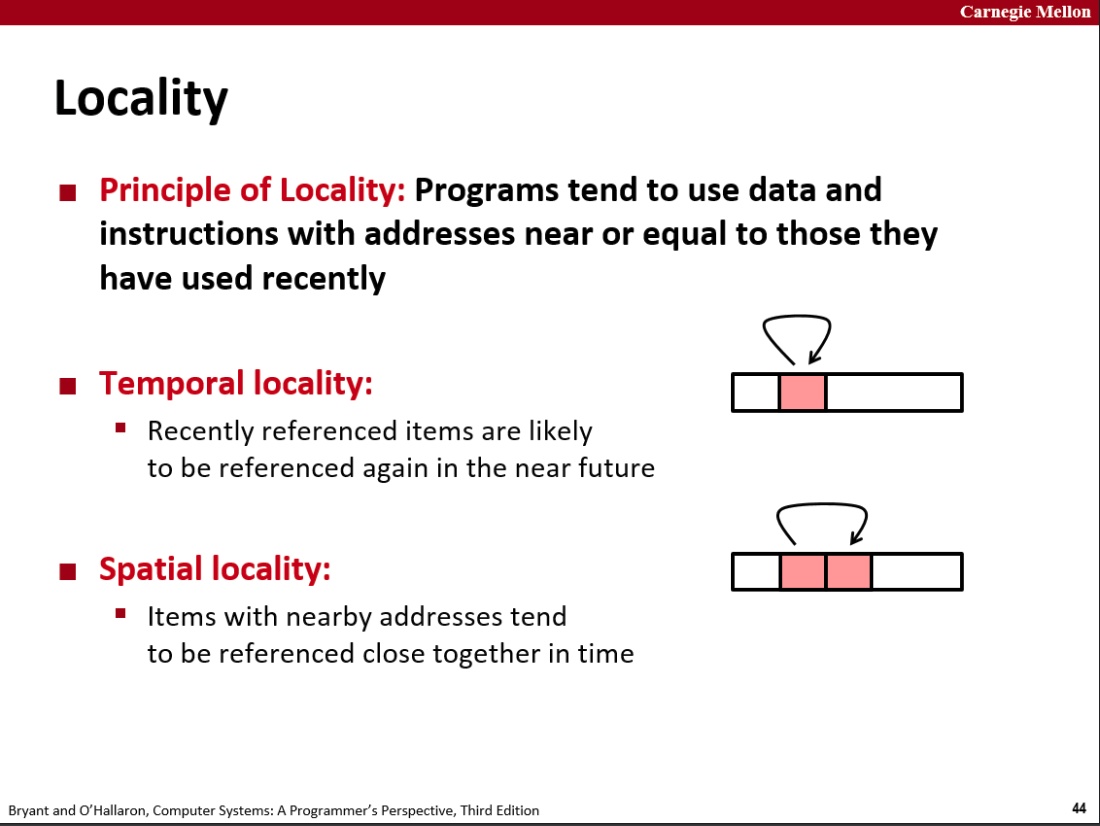

局限性原理,图片来自:CMU

由于数据的局限性,CPU往往需要在短时间内重复多次读取数据,内存的运行频率自然是远远跟不上CPU的处理速度的,怎么办呢?缓存的重要性就凸显出来了,CPU可以避开内存在缓存里读取到想要的数据,称之为命中(hit)。L1的运行速度很快,但是它的数据容量很小,CPU能在L1里命中的概率大概在80%左右——日常使用的情况下;L2、L3的机制也类似如此,这样一来,CPU需要在内存中读取的数据大概为5%-10%,其余数据命中全部可以在L1、L2、L3中做到,大大减少了系统的响应时间,总的来说,所有CPU读取数据的顺序都是先缓存再内存。

L1、L2、L3缓存跟内存速度相差很大,它们构成上的不同导致了其速度的差距,那么CPU缓存和内存分别是怎样构成的呢?

缓存SRAM与内存DRAM的区别

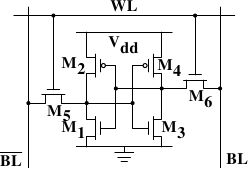

CPU缓存基本由SRAM(Static RAM,静态RAM)构成,内存的DRAM其实是SDRAM(同步动态随机储存器),是DRAM(Dynamic RAM,动态)的一种。

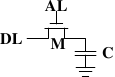

DRAM

DRAM只含一个晶体管和一个电容器,集成度非常高,可以轻松做出大容量(内存),但是因为靠电容器来储存信息,所以需要不断刷新补充电容器的电荷,充电放电之间的时间差导致了DRAM比SRAM的反应要缓慢得多。

SRAM

SRAM相比DRAM的复杂度就高了不止一筹,所以导致SRAM的集成度很低——前期CPU缓存不能集成进CPU内部也有这个原因。SRAM的特点就是快,有电就有数据,不需要刷新时间所以凸显其数据传输速度很快,缺点就是占据面积大、成本低。假如一个DRAM占据一个单位的地方,一个SRAM就要占据六个单位的地方,差别还是挺大的。

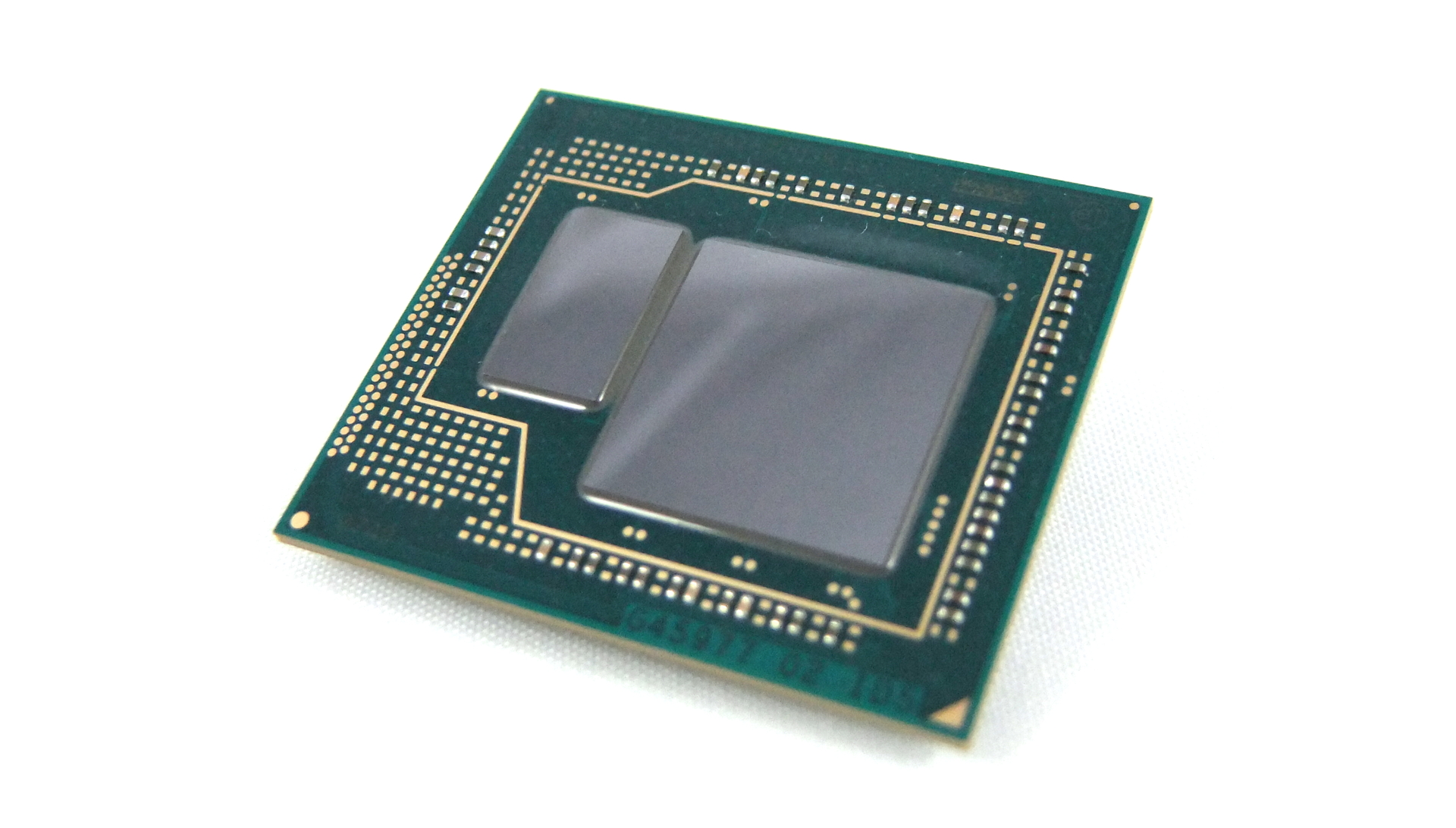

番外:L4四级缓存和eDRAM

I7-4750H

并不是每个CPU都会使用SRAM作为CPU缓存,IBM的Power系列处理器就使用了eDRAM作为CPU缓存;我们再看看Intel Haswell I7-4750H这个CPU,其主要受关注的地方在于CPU内嵌入了128MB的eDRAM作为显存让核心显卡Iris Pro 5200使用,在不使用核心显卡的时候,128MB eDRAM将会成为处理器的L4四级缓存。当然了,I7-4750H多了L4之后在处理器性能上也没提高多少,eDram缓存的主要作用还是在于给核心显卡当显存上。

用着旧机不爽的你,是否准备购买一波新装备啦,想要各类硬件推荐的请找小超哥(微信9501417),也可以让小超哥拉你进去超能群与其他网友一起聊哦~

[转帖]CPU 的缓存的更多相关文章

- 浅谈CPU三级缓存和缓存命中率

CPU: CPU缓存(Cache Memory)是位于CPU与内存之间的临时存储器,它的容量比内存小的多但是交换速度却比内存要快得多.缓存的出现主要是 为了解决CPU运算速度与内存读写速度不匹配的矛盾 ...

- [转帖]CPU Cache 机制以及 Cache miss

CPU Cache 机制以及 Cache miss https://www.cnblogs.com/jokerjason/p/10711022.html CPU体系结构之cache小结 1.What ...

- Java高并发--CPU多级缓存与Java内存模型

Java高并发--CPU多级缓存与Java内存模型 主要是学习慕课网实战视频<Java并发编程入门与高并发面试>的笔记 CPU多级缓存 为什么需要CPU缓存:CPU的频率太快,以至于主存跟 ...

- 聊聊高并发(三十四)Java内存模型那些事(二)理解CPU快速缓存的工作原理

在上一篇聊聊高并发(三十三)从一致性(Consistency)的角度理解Java内存模型 我们说了Java内存模型是一个语言级别的内存模型抽象.它屏蔽了底层硬件实现内存一致性需求的差异,提供了对上层的 ...

- Java内存模型(二)volatile底层实现(CPU的缓存一致性协议MESI)

CPU的缓存一致性协议MESI 在多核CPU中,内存中的数据会在多个核心中存在数据副本,某一个核心发生修改操作,就产生了数据不一致的问题,而一致性协议正是用于保证多个CPU cache之间缓存共享数据 ...

- 并发与高并发(三)-CPU多级缓存の乱序执行优化

一.CPU多级缓存-乱序执行优化 处理器或编译器为提高运算速度而做出违背代码原有顺序的优化. 重排序遵循原则as-if-serial as-if-serial语义:不管怎么重排序(编译器和处理器为了提 ...

- 并发编程二、CPU多级缓存架构与MESI协议的诞生

前言: 文章内容:线程与进程.线程生命周期.线程中断.线程常见问题总结 本文章内容来源于笔者学习笔记,内容可能与相关书籍内容重合 偏向于知识核心总结,非零基础学习文章,可用于知识的体系建立,核心内容 ...

- java并发编程(三)cpu cache & 缓存一致性

一 cpu cache 1. cache的意义 为什么需要CPU cache?因为CPU的频率太快了,快到主存跟不上,这样在处理器时钟周期内,CPU常常需要等待主存,浪费资源.所以cache的出 ...

- cpu多级缓存

CPU cache: CPU的频率太快,主存跟不上,在处理器时钟周期内,CPU需要等待主存,浪费资源.cpu cache的出现,缓解了cpu与主存之间速度不匹配的问题. CPU cache的特性: 1 ...

随机推荐

- 【BZOJ1053】[HAOI2007]反素数

[BZOJ1053][HAOI2007]反素数 题面 bzoj 洛谷 题解 可以从反素数的定义看出小于等于\(x\)的最大反素数一定是约数个数最多且最小的那个 可以枚举所有的质因数来求反素数,但还是跑 ...

- Openstack入门篇(十)之nova服务(计算节点)的部署与测试

1.安装服务软件包 [root@linux-node2 ~]# yum install -y centos-release-openstack-newton [root@linux-node2 ~]# ...

- springmvc配置中,mapper一直依赖注入不进去的问题记录

问题还原: service层在引用mapper层接口时,一直依赖注入不进去.查看spring-context.xml配置,也未发现异常[因为以前就是这么配置],但是始终无法注入. 原因: 问题不出在s ...

- python 利用urllib 获取办公区公网Ip

import json,reimport urllib.requestdef GetLocalIP(): IPInfo = urllib.request.urlopen("http://ip ...

- arpspoof+driftnet+ ARP欺骗简单图片抓取

arpspoof+driftnet+ ARP欺骗简单图片抓取 driftnet是一款简单而使用的图片捕获工具,可以很方便的在网络数据包中抓取图片.该工具可以实时和离线捕获指定数据包中是图片 环境 受害 ...

- PKCS#7

1.名词解释 数字签名:在ISO7498-2标准中定义为:"附加在数据单元上的一些数据,或是对数据单元所作的密码变换,这种数据和变换允许数据单元的接收者用以确认数据单元来源和数据单元的完整性 ...

- Hbase基本用法

hbase 一些重要的解释(杂) 访问habse三种方式 访问hbase table中的行,只有三种方式: 1 通过单个row key访问 2 通过row key的range 3 全表扫描 Row k ...

- egret性能优化总结

## 来自官方的优化建议 详见:http://edn.egret.com/cn/article/index/id/287 (1) 少使用Alpha混合. (2) 显式停止计时器,让它们准备好进行垃圾回 ...

- windows 无法链接 \\ , 拼写错误或者网络有问题,解决方法

1. 楼主首先在网上搜索了一遍问题, 比较全面的回答链接如下http://blog.csdn.net/newizan/article/details/50313137 然而并没有解决问题, 于是反思了 ...

- 使用Python批量修改数据库执行Sql文件

由于上篇文章中批量修改了文件,有的时候数据库也需要批量修改一下,之前的做法是使用宝塔的phpMyAdmin导出一个已经修改好了的sql文件,然后依次去其他数据库里导入,效率不说极低,也算低了,且都是些 ...