Normal synchronous FIFO mode 和 Show-ahead synchronous FIFO mode

FIFO是先进先出,可以用fifo来处理跨时钟域的数据传输问题,用到的地方特别多,一定要搞会。

在学习调用fifo的IP核中发现有normal synchronous FIFO mode 和 Show-ahead synchronous FIFO mode这两种模式,就研究一下。

研究 IP 核最方便的方式就是用 modesim 仿真一下,这样关系就会很明了。

下面的两幅图是我用 Time_Gen 软件自己总结画的,并不是 modesim 的仿真图。

假定存入fifo的第一个数是01,第二个数是02,第三个数是03,以此类推。。。

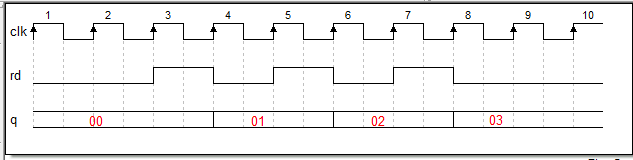

clk是读时钟,rd是读使能,q是fifo的数据输出端

normal mode,只有在读使能信号有效的时候,才会在读时钟上升沿来的时候输出第一个数01。

Show-ahead 模式的输出要比 normal 模式的输出早一拍,意思是只要FIFO中有数据,他就会把第一个数据输出,

当第一个读使能信号来的时候,则会在读时钟上升沿的时候输出第二个数据02。

Normal mode Show-ahead mode

既然二者的区别是数据输出相差一拍,因此在设计 fifo 的时候就要根据不同的模式进行设计

下面举个例子,该代码实现了100Mhz 与 80Mhz 不同时钟域的数据传输问题

因为不同时钟域的频率不同,在进行数据传输的时候如果不进行处理必然会有数据丢失

FIFO 可以缓存数据,因此我们可以先把数据放在 fifo 里,再进行传输

当fifo中的数据 resudw>=某个数的时候,就不允许往 fifo 中写入数据,当 FIFO 空的时候也不允许再读数据。

module fifo(

rst_n ,

clk_in , //100Mhz ,fifo写时钟

data_in , //输入的数据

data_in_vld,//输入数据有效指示信号 clk_out , //80Mhz ,fifo读时钟

data_out , //输出的数据

data_out_vld,//输出数据有效指示信号

b_rdy //当为高,表示可以接收从fifo中读的数据,反之则不行 ); input rst_n ,clk_in,clk_out,b_rdy;

input [:] data_in ;

input data_in_vld ;

output[:] data_out ;

output[:] data_out_vld;

reg wr_ff0;

wire wr_ff1;

wire[:] q;

reg[:] data_out;

reg data_out_vld;

reg rd_ff0;

wire rdempty ;

wire wrfull ;

wire[:] wrusedw;

//调用IP核生成位宽为16 位,深度为64的FIFO, Show-ahead模式

my_fifo u1_fifo(

.data (data_in),

.rdclk(clk_out),

.rdreq(rd_ff0),

.wrclk(clk_in),

.wrreq(wr_ff1),

.q (q),

.rdempty(rdempty),

.wrfull (wrfull ),

.wrusedw(wrusedw)

);

//----------------------------------------------------------------------

//写满保护

always @(*)begin

if(wrusedw>=) begin

wr_ff0<=;

end

else

wr_ff0<=;

end

assign wr_ff1 = (data_in_vld && wr_ff0)?'b1:1'b0; //rd_ff0

always @(*)begin

if(b_rdy==&&rdempty== )begin

rd_ff0<=;

end

else

rd_ff0<=;

end

//-------------------------------------------------------------

//如果是Show-ahead 模式入,此时data_out与data_out_vld是对齐的

//如果是normal 模式,则需要将rd_ff0在多打一拍,然后将rd_ff1值给data_out_vld才能对齐

always @(posedge clk_out or negedge rst_n)begin

if(rst_n=='b0)begin

data_out<=;

end

else begin

data_out<=q;

end

end always @(posedge clk_out or negedge rst_n)begin

if(rst_n=='b0)begin

data_out_vld<=;

end

else begin

data_out_vld<=rd_ff0;

end

end

endmodule

文章出处:http://www.cnblogs.com/aslmer/p/5872412.html

Normal synchronous FIFO mode 和 Show-ahead synchronous FIFO mode的更多相关文章

- 同步fifo与异步fifo

参考以下帖子: https://blog.csdn.net/hengzo/article/details/49683707 https://blog.csdn.net/Times_poem/artic ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- IP核——FIFO

一.Quartus 1.打开Quartus ii,点击Tools---MegaWizard Plug-In Manager 2.弹出创建页面,选择Creat a new custom megafunc ...

- 详解三种缓存过期策略LFU,FIFO,LRU(附带实现代码)

在学操作系统的时候,就会接触到缓存调度算法,缓存页面调度算法:先分配一定的页面空间,使用页面的时候首先去查询空间是否有该页面的缓存,如果有的话直接拿出来,如果没有的话先查询,如果页面空间没有满的时候, ...

- LATTICE 存储之FIFO的使用

坑,,以后填 对于Lattice 的 FIFO 存储器分为两种,见下图: 这两个的主要区别是一个后面加DC一个不加,那这个DC是什么意思呢??DC这里是Dual Clock的意思,也就是双时钟的意 ...

- FIFO

FIFO存储器 FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序 ...

- Verilog学习笔记简单功能实现(八)...............异步FIFO

基本原理: 1.读写指针的工作原理 写指针:总是指向下一个将要被写入的单元,复位时,指向第1个单元(编号为0). 读指针:总是指向当前要被读出的数据,复位时,指向第1个单元(编号为0). ...

- FIFO学习心得

1,名字.FIFO=First in first out. 2,特点.顺序读入,顺序读出,先入先出. 3,用途.数据缓冲.使两个数据传输速率不一样的设备相匹配. 4,参数. ①,THE WIDTH和T ...

随机推荐

- Html+css实现带图标的控件

</pre><pre name="code" class="html"><!DOCTYPE html> <html l ...

- sk-learning(1)

sk-learning学习笔记(1) 简介 scikit learning 是一个python的机器学习库,内置许多机器学习的算法诸如svm.随机森林.逻辑回归.贝叶斯网络等算法.覆盖了分类.聚类.回 ...

- File 与 Log #3--动态加入控件,[图片版]访客计数器(用.txt档案来记录)

File 与 Log #3--动态加入控件,[图片版]访客计数器(用.txt档案来记录) 以前的两篇文章(收录在书本「上集」的第十七章) 请看「ASP.NET专题实务」,松岗出版 File 与 Log ...

- JIRA Plugin Development——Configurable Custom Field Plugin

关于JIRA Plugin开发的中文资料相当少,这可能还是由于JIRA Plugin开发在国内比较小众的原因吧,下面介绍下自己的一个JIRA Plugin开发的详细过程. 业务需求 创建JIRA IS ...

- 学习Rust Book之写Cargo配置文件

不知道为什么这个文件就是编译不过 [package] name = "hello_world" version = "0.0.1" author = " ...

- 输出流缓冲的意义 何时缓冲 Stdout Buffering

From : https://eklitzke.org/stdout-buffering 译者:李秋豪 大多数编程语言默认提供了i/o缓冲特性,因为这会使得输出更加有效率.这些缓冲功能大都是默默工作& ...

- Oracle Hint 之 Append

1 描述 所谓直接路径操作,就是绕过buffer cache,直接将数据插入到表所在的数据文件中: 假如有表A,要将A中的数据插入到表B,在普通的间接插入下,先将A中的数据块传进buffer cach ...

- caller、callee的用法及区别

1 :caller 返回一个调用当前函数的引用 如果是由顶层调用的话 则返回null (举个栗子哈 caller给你打电话的人 谁给你打电话了 谁调用了你 很显然是下面a函数的执行 只有在打电话的时 ...

- madplay移植

移植前需求准备: a. 源码包: 1. libid3tag-0.15.1b.tar.gz 2. libmad-0.15.1b.tar.gz 3. madplay-0.15.2b.tar.gz 4. z ...

- 【计数】cf938E. Max History

发现有一种奇怪的方法不能快速预处理? 复习一下常见的凑组合数的套路 You are given an array a of length n. We define fa the following w ...