verilog HDL -模块代码基本结构

1--verilog HDL 语言的预编译指令作用:指示在编译verliog HDL源代码前,需要执行哪些操作。

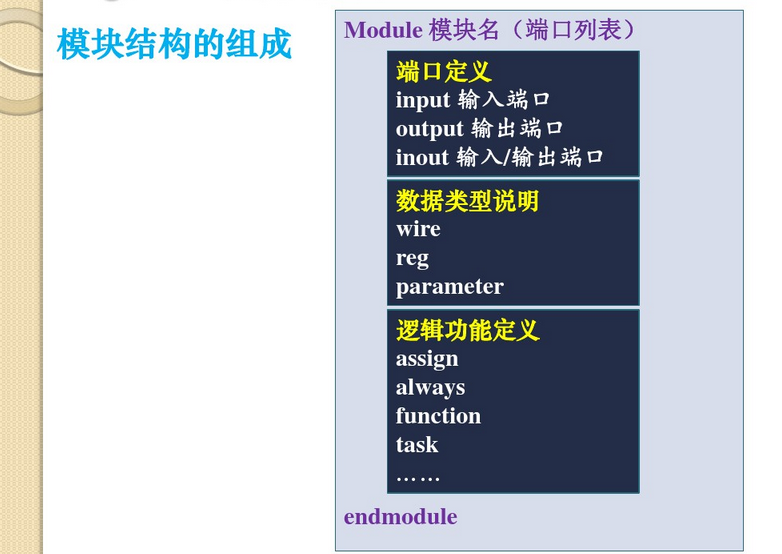

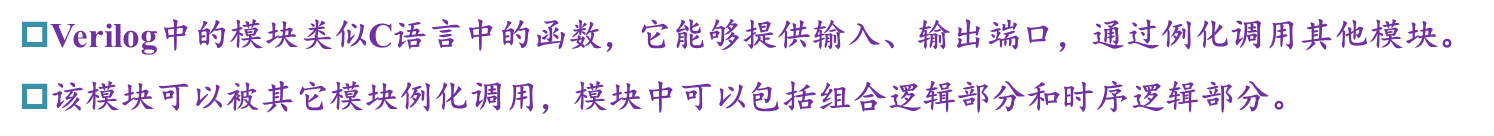

2--模块内容是嵌在module 和endmodule两个语句之间。每个模块实现特定的功能,模块可进行层次的嵌套,因此可以将大型的数字电路设计分割成大小不一的小模块来实现特定的功能,最

后通过由顶层模块调用子模块来实现整体功能。

3--模块包括接口描述部分和逻辑功能描述部分。这可以把模块与器件相类比。

4-verilog hdl语言支持的并行语句主要有一下四种:

连续赋值语句

模块实例化语句

initial语句

always语句

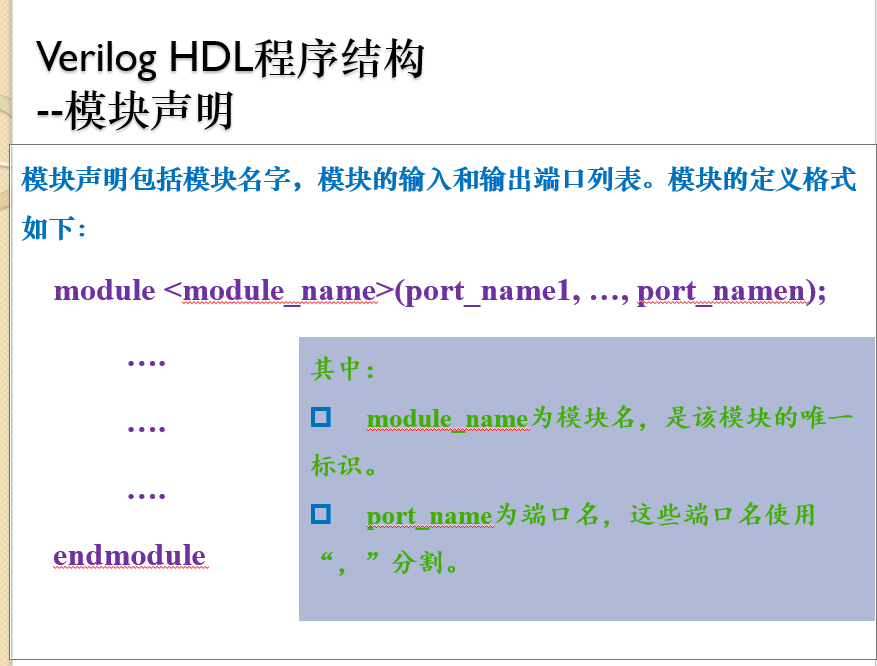

模块引用方式:

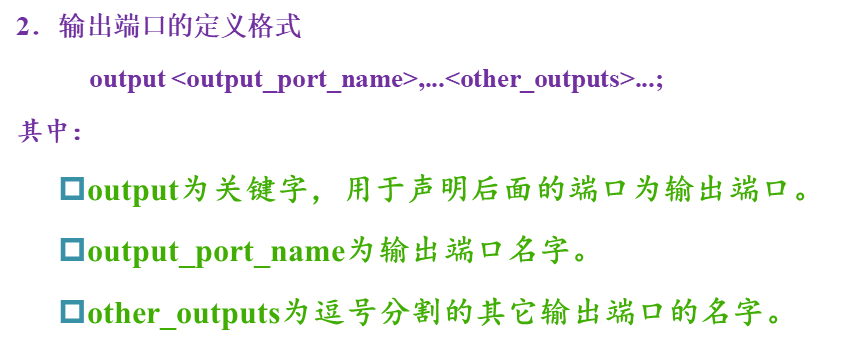

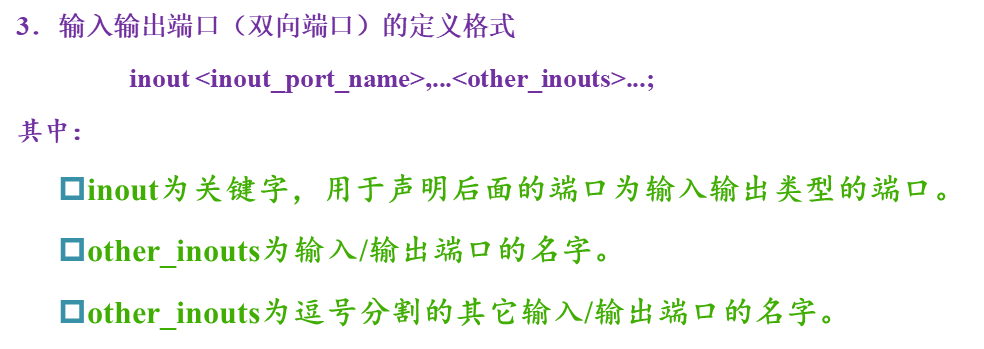

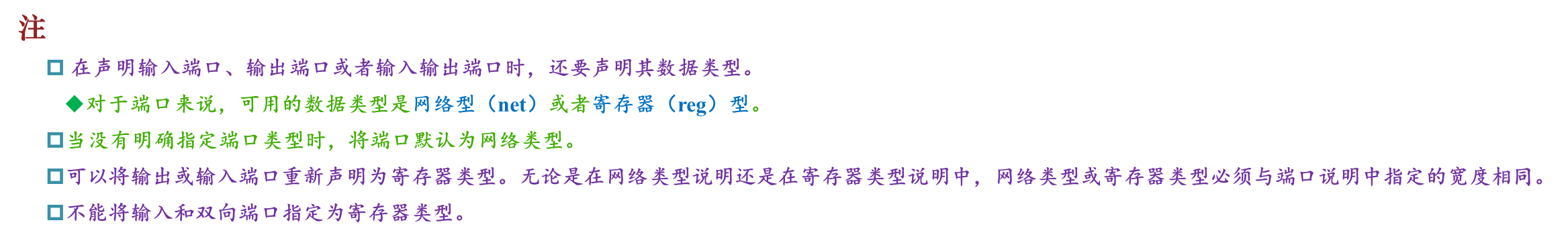

端口定义:

事件:当线网型或寄存器型信号的值发生变化时,对电路来说就是产生了一个事件,就需要进行相应的计算。

事件在代码中以@(时间列表)形式出现,事件列表可以有多个,用or分开,也可以用“,”分开,他们之间是“或”的关系。也就是说只要有一个事件产生,就会执行进程语句。事件分为电平信号和边沿信号两种。(posedge:上升沿事件,negedge:下降沿事件。)

【进程:行为模型的本质是进程。一个进程可以被看做是一个独立的运行单元,它可能很简单,也可能很复杂,我们可以将数字系统的行为看作很多有机结合的进程的集合。

在Verilog HDL中,描述进程的基本语句是always和initial。Always过程反复执行其中的块语句,而initial过程中的语句块只执行一次。除了always和initial过程块外,一个assign赋值语句、一个实例元件的调用都可以看作是一个进程。

进程的特点:

1-进程只有两种状态,即执行态和等待状态。进程是否进入执行态,取决于是否满足特定的条件,如敏感变量是否发生变化。一旦满足条件,进程即进入执行状态。当该进程执行完毕或遇到停止语句后,即停止执行,自动返回到起始语句,进入等待状态。

2-进程一般由敏感信号的变化来启动

3-各个进程之间通过信号线进行通信。多个进程之所以能同步并发运行,一个很重要的原因就是有进程之间的信号线的通信和协议。

4-一个进程中只允许描述对应于一个时钟信号的同步时序逻辑。

5-进程之间是并发执行的。两个或更多个“always”过程块、“assign”持续赋值语句、实例元件调用等操作都是同时执行的。】

always语句:(可综合)

特点:

1-循环执行

2-可综合

【综合:将用行为和功能层表达的电子系统转换成低层次的便于具体实现的模块组合装备的过程。

综合过程将把软件设计的HDL描述与硬件结构挂钩,是将软件转化为硬件电路的关键步骤,是文字描述与硬件相结合的一座桥梁。综合就是将电路的高级语言(如行为描述)转化为低级的,可以FPGA/CPLD的基本结构相映射的网表文件或程序。

当输入的hdl文件在eda工具中检测无误后,首选面临的就是逻辑综合,因此要求hdl源文件中的语句都是可综合的。】

3-必须有时序控制

4-在0时刻开始执行,可以有一条或者多条顺序语句。

使用方法:

语法格式:always

[时序控制]顺序语句;

时序控制可以是以时间刻度为单位的时间延时数字,也可以是信号变化事件条件。

当顺序语句有多条时,可以使用“begin”-“end”字符对进行组织。

【begin -- end就是一个模块 (相当于 C语音的一段程序)的起始和结束的标记。非常类似于 C语言中的 大括号 ({……})。】

注意:在不同的always逻辑块中,对同一个reg变量进行赋值,会冲突导致报错!

赋值操作符:

意义是更新被赋值数据对象的值。

1,赋值操作符 <=:

该操作符在进程块中使用,是非阻塞赋值,由于在进程中使用,所以被赋值的数据对象必须是reg型。

2,赋值操作符=:

该操作符在进程或者assign连续赋值语句中使用。被赋值数据对象可以是reg型或wire型,其中在进程块中的赋值方式是阻塞赋值。

*********************************************************************************************************************************************************

学习了上面的知识点,应该就能看懂下面的代码了。

'timescale 1ns/1ps //预编译指令定义了时间单位为1ns,时间精度为1ps module led_test(clk,rst_n,led); input clk;

input rst_n;

output [:] led; //寄存器型数据对象的定义

reg [:] timer;

reg [:] led; always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

timer <=;

else if(timer=='d199_999_999)

timer<=;

else

timer<=timer+'b1;

end always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

led<='b0000;

else if(timer=='d49_999_999)

led<='b0001;

else if(timer=='d99_999_999)

led<='b0010;

else if(timer=='149_999_999)

led<='b0100;

else if(timer=='d199_999_999)

led<='b1000;

end endmodule

ok,今天的学习结束!

verilog HDL -模块代码基本结构的更多相关文章

- Verilog HDL基础语法讲解之模块代码基本结构

Verilog HDL基础语法讲解之模块代码基本结构 本章主要讲解Verilog基础语法的内容,文章以一个最简单的例子"二选一多路器"来引入一个最简单的Verilog设计文件的 ...

- Verilog HDL模块的结构

一个设计是由一个个模块(module)构成的.一个模块的设计如下: 1.模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的功能,模块可进行层次的嵌套,因此可以将大型的数字 ...

- 自己动手写处理器之第二阶段(2)——Verilog HDL简单介绍

将陆续上传本人写的新书<自己动手写处理器>(尚未出版),今天是第六篇.我尽量每周四篇 2.3 Verilog HDL简单介绍 本书实现的OpenMIPS处理器是使用Verilog HDL编 ...

- 你知道Verilog HDL程序是如何构成的吗

本节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点. 二十进制编码器及Verilog HDL描述 二十进制编码器是数字电路中常用的电路单元 ...

- Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出. 一.Verilog ...

- 浅谈Verilog HDL代码编写风格

消失了好久,没有写文章,也没有做笔记,因为最近再赶一个比赛,时间很紧,昨天周六终于结束了,所以趁着周末这会儿有时间,写点东西,记录下来.首先我学习FPGA才一年多,我知道自己没有资格谈论一些比较深层次 ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

- 写自己的第二级处理器(3)——Verilog HDL行为语句

我们会继续上传新书<自己动手写处理器>(未公布),今天是第七章,我每星期试试4 2.6 Verilog HDL行为语句 2.6.1 过程语句 Verilog定义的模块一般包含有过程语句,过 ...

随机推荐

- springboot学习目录

1.spring boot 简单示例 一个简单的springboot 例子 https://www.cnblogs.com/shoshana-kong/p/9641696.html 2. sprin ...

- 批量IP自动netcat脚本

批量IP自动netcat脚本nc.sh 在同一目录新建一个名为ncip的文件,并以每行一个IP的方式罗列.使用sh命令执行nc.sh.此例中是测试22端口访问情况. #!/bin/bash IP_LI ...

- jsonArray返回

dao <select id="selectShopInfo" resultType="java.util.HashMap"> SELECT * F ...

- Object.defineProperty(o,p,descriptor ) 理解应用

1. Object.defineProperty 在一个对象上定义一个新属性,或修改一个已经存在的属性, 最终返回这个对象. var __define = this.__define || func ...

- Python常用内置函数介绍

Python提供了一个内联模块buildin.内联模块定义了一些开发中经常使用的函数,利用这些函数可以实现数据类型的转换.数据的计算.序列的处理等功能.下面将介绍内联模块中的常用函数. Python内 ...

- python入门(四):字符串、编码、random

1.字符串 字符串基本有两种类型,str和bytes >>> s="a" >>> type(s) <class 'str'> ...

- python入门(三):循环

1.for i in xxx xxx: 序列(列表,元祖,字符串) xxx: 可迭代对象 >>> for i in "abc": ... print(i) ...

- window.innerWidth和document.body.clientWidth的区别

<!DOCTYPE html> <html lang="en"> <head> <meta charset="UTF-8&quo ...

- python argparse(参数解析)模块学习(一)

class ArgumentParser(_AttributeHolder, _ActionsContainer): """Object for parsing comm ...

- python 文件读写方式

一.普通文件读写方式 1.读取文件信息: with open('/path/to/file', 'r') as f: content = f.read() 2.写入文件中: with open('/U ...