有限状态机HDL模板

逻辑设计, 顾名思义, 只要理清了 逻辑 和 时序, 剩下的设计只是做填空题而已。

下面给出了有限状态机的标准设计,分别为 VHDL 和 Verilog 代码

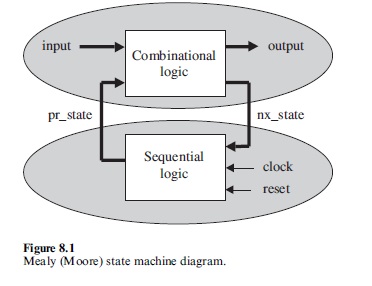

1 有限状态机

2 VHDL模板一

library IEEE;

use ieee.std_logic_1164.all; --! 1) 端口定义

entity <entity_name> is

port

(

DIN : in <data_type>;

RST : in std_logic;

CLK : in std_logic;

DOUT : out <data_type>

);

end <entity_name>; --! 2) 状态定义

architecture <arch_name> of <entity_name> is type state is (IDLE, ST1, ST2, ...);

signal c_state, n_state : state; begin --! 3) 时序逻辑

pfsmsyn: process (rst, clk)

begin

if (rst = '') then

c_state <= IDLE;

elsif (clk'event and clk='') then

c_state <= n_state;

endif;

end process; --! 4) 组合逻辑

pfsmlogic: process (din, c_state)

begin

case c_state is

when IDLE =>

if (din = ...) then

dout <= <value>; -- 输出

c_state <= state1; -- 状态

else ...

end if;

when ST1 =>

... ...

... ...

... ...

when others =>

... ... end case;

end process; end <arch_name>;

3 Verilog模板一

// 1) 端口声明

module fsm(clk, rst, ctrl, dout);

input clk, rst, ctrl;

output [n-:] dout; // n 取决于输出值的位数

reg [n-:] dout; // 2) 状态定义

parameter IDLE = , ST1 = , ST2 = , ST3 = , ....;

reg [m-:] c_state, n_state; // m 取决于‘“状态”数量的位数 // 3) 时序逻辑

always @ (posedge clk or posedge rst)

begin: SEQ

if (rst)

c_state = IDLE;

else

c_state = n_state;

end // 4) 组合逻辑

module @ (ctrl or c_state)

begin: COMB

case (c_state)

IDLE: begin

dout = <value0>;

n_state = ST1;

end

ST1: begin

dout = <value1>;

n_state = ST2;

end

ST2:

. . . . . .

. . . . . .

. . . . . .

endcase

end endmodule

参考资料:

<Circuit Design with VHDL> chapter 8 State Machines

<HDL Chip Design>

有限状态机HDL模板的更多相关文章

- 基于Unity有限状态机框架

这个框架是Unity wiki上的框架.网址:http://wiki.unity3d.com/index.php/Finite_State_Machine 这就相当于是“模板”吧,自己写的代码,写啥都 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 有限状态机FSM(自动售报机Verilog实现)

有限状态机FSM(自动售报机Verilog实现) FSM 状态机就是一种能够描述具有逻辑顺序和时序顺序事件的方法. 状态机有两大类:Mealy型和Moore型. Moore型状态机的输出只与当前状态有 ...

- 如何高效的编写Verilog HDL——进阶版

博主之前写过一篇文章来谈论如何高效的编写Verlog HDL——菜鸟版,在其中主要强调了使用Notepad++来编写Verilog HDL语言的便捷性,为什么说是菜鸟版呢,因为对于新手来说,在还没有熟 ...

- gVim编辑器 模板篇

上文介绍了gVim的常用操作,这次总结一下我自己常用的模板. 安装和配置好gVim后,在Program Files (x86)\Vim目录下有个“_vimrc”文件,双击选择gVim软件打开,在里面添 ...

- html5引擎开发 -- 引擎消息中心和有限状态机 - 初步整理 一

一 什么是有限状态机 FSM (finite-state machine),又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型.他对于逻辑以及 ...

- 转载.怎样在Quartus II中转化HDL文件为bsf文件?

步骤1 新建或打开Quartus II工程,用QII自带文本编辑器打开HDL文件. 图1 用QII自带的文本编辑器打开HDL文件 步骤2 选择File>Create / Update>Cr ...

- 算法复习——网络流模板(ssoj)

题目: 题目描述 有 n(0<n<=1000)个点,m(0<m<=1000)条边,每条边有个流量 h(0<=h<35000),求从点 start 到点 end 的最 ...

- win7+vim搭建+verilog HDL IDE

参考地址:http://www.huangdc.com/421 参考文章为2016年,部分更新贴于文章内了 安装下载vim vim在win下叫gvim,下载地址:https://www.vim.org ...

随机推荐

- .NET向APNS苹果消息推送通知

一.Apns简介: Apns是苹果推送通知服务. 二.原理: APNs会对用户进行物理连接认证,和设备令牌认证(简言之就是苹果的服务器检查设备里的证书以确定其为苹果设备):然后,将服务器的信息接收并且 ...

- percona 5.6升级到5.7相关error及解决方法

今早,把开发环境的mysql升级到了5.7.15,5.6数据导入后,启动一切正常,检查.err日志,发现有如下异常: 2016-10-31T00:29:33.187073Z 0 [Warning] S ...

- css百宝箱

关于css百宝箱? 在前端学习中,总会遇到零星的知识点,小技巧,这些知识点小到不至于用一片博客写出来,遇到时网上查询一下或许也能搞定,但不一定能记住,所以这篇博客就用来记录那些散落的知识点,积少成多, ...

- 说反话(c++实现)

描述:给定一句英语,要求你编写程序,将句中所有单词的顺序颠倒输出. 输入:测试输入包含一个测试用例,在一行内给出总长度不超过80的字符串.字符串由若干单词和若干空格组成,其中单词是由英文字母(大小写有 ...

- CSS3随内容自动伸缩的背景

CSS3给我们带来一个非常实用的新属性:border-image,利用这个属性我们可以做出随着内容的增减自动伸缩的背景.废话不多说,看代码! HTML: <ol> <li>第一 ...

- mysql实时同步到mssql的解决方案

数据库在应用程序中是必不可少的部分,mysql是开源的,所以很多人它,mssql是微软的,用在windows平台上是非常方便的,所以也有很多人用它.现在问题来了,如何将这两个数据库同步,即数据内容保持 ...

- Atitit.工作流系统的本质是dsl 图形化的dsl 4gl

Atitit.工作流系统的本质是dsl 图形化的dsl 4gl 1. 工作流系统的本质是dsl 图形化的dsl 4gl1 2. 为什么每个项目系统都需要工作流1 3. 工作流dsl与java .n ...

- SAP ST05数据跟踪使用

有时我们想知道SAP操作,对数据库中的那些表进行的增删查改. 可以使用ST05跟踪SQL语句. ST05功能界面如下: 1---激活跟踪 2---结束跟踪 3---显示跟踪结果. 如果想跟踪SQL语句 ...

- [leetcode] Reverse Bits

Reverse Bits Reverse bits of a given 32 bits unsigned integer. For example, given input 43261596 (re ...

- Android——五大布局

Android的五大布局分为: 线性布局 相对布局 帧布局 绝对布局 表格布局 一.线性布局 线性布局在开发中使用最多,具有垂直方向与水平方向的布局方式 通过设置属性"android:ori ...