电赛总结(四)——波形发生芯片总结之AD9834

一、特性参数

1、2.3V~5.5V供电

2、输出频率高达37.5MHz

3、正弦波、三角波输出

4、提供相位调制和频率调制功能

5、除非另有说明,VDD = 2.3 V至5.5 V,AGND = DGND = 0 V,TA = TMIN至TMAX,RSET = 6.8 k,RLOAD = 200 (对于IOUT和IOUTB)。

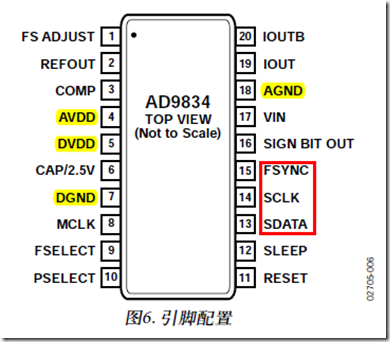

二、芯片管脚图

三、管脚功能说明

| 管脚名称 | 功能 |

| FS ADJUST |

此引脚和AGND之间连接一个电阻(RSET),从而决定满量程DAC电流的幅度。RSET与满量程电流之间的关系如下: IOUT FULL SCALE = 18 × FSADJUST/RSET |

| REFOUT | 基准电压输出。AD9834通过此引脚提供1.20 V内部基准电压源。 |

| COMP | DAC偏置引脚。此引脚用于对DAC偏置电压进行去耦。 |

| VIN |

比较器输入。可利用比较器从正弦DAC输出产生方波。DAC输出应经过适当滤波,然后再施加于比较器,以改善抖动性能。当控制寄存器中的Bit OPBITEN和Bit SIGN/PIB置1时,比较器输入端连接到VIN。 |

|

IOUT, |

电流输出。这是高阻抗电流源。应在IOUT和AGND之间连接一个标称值为200 的负载电阻。IOUTB最好应通过一个大小为200 的外部负载电阻连接到AGND,但也可直接与AGND相连。此外还建议通过一个20 pF电容连接到AGND,以防止出现时钟馈通。 |

| AVDD | 模拟部分的正电源。AVDD的值范围为2.3 V至5.5 V。应在AVDD和AGND之间连接一个0.1uF去耦电容。 |

| DVDD | 数字部分的正电源。DVDD的值范围为2.3 V至5.5 V。应在DVDD和DGND之间连接一个0.1uF去耦电容。 |

| CAP/2.5V |

数字电路采用2.5 V电源供电。当DVDD超过2.7 V时,此2.5 V利用片内调节器从DVDD产生。该调节器需要在CAP/2.5 V至DGND之间连接一个典型值为100 nF的去耦电容。如果DVDD小于或等于2.7 V,则CAP/2.5 V应与DVDD直接相连。 |

| DGND | 数字地。 |

| AGND | 模拟地。 |

| MCLK |

数字时钟输入。DDS输出频率是MCLK频率的一个分数,分数的分子是二进制数。输出频率精度和相位噪声均由此时钟决定。 |

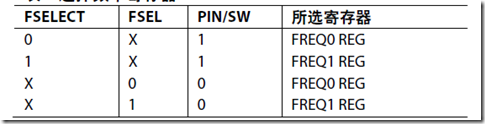

| FSELECT |

频率选择输入。FSELECT控制相位累加器中使用的具体频率寄存器(FREQ0或FREQ1)。可使用引脚FSELECT或BitFSEL来选择要使用的频率寄存器。使用Bit FSEL来选择频率寄存器时,FSELECT引脚应与CMOS高电平或低电平相连。 |

| PSELECT |

相位选择输入。PSELECT控制将增加到相位累加器输出的具体相位寄存器(PHASE0或PHASE1)。可使用引脚PSELECT或Bit PSEL来选择要使用的相位寄存器。当相位寄存器由Bit PSEL控制时,PSELECT引脚应与CMOS高电平或低电平相连 |

| RESET |

高电平有效数字输入。RESET可使相应的内部寄存器复位至0,以提供中间电平的模拟输出。RESET不影响任何可寻址寄存器。 |

| SLEEP | 高电平有效数字输入。当此引脚处于高电平时,DAC关断。此引脚功能与控制位SLEEP12相同。 |

| SDATA | 串行数据输入。16位串行数据字施加于此输入。 |

| SCLK | 串行时钟输入。数据在每个SCLK下降沿逐个输入AD9834。 |

| FSYNC |

低电平有效控制输入。这是输入数据的帧同步信号。当FSYNC变为低电平时,即告知内部逻辑,正在向器件 |

|

SIGN BIT |

逻辑输出。比较器输出通过此引脚提供,或者可通过此引脚输出NCO的MSB。通过将控制寄存器中的Bit |

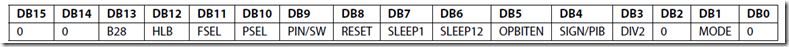

四、寄存器

一个16位的控制寄存器。设置好之后即可产生对应的波形

|

Bit |

名称 |

功能 |

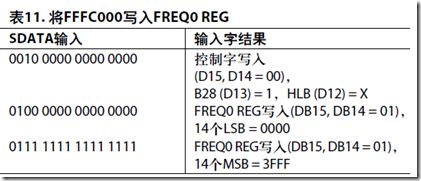

| DB13 | B28 |

B28 = 1可将一个完整字通过两次连续写入载入频率寄存器。第一次写入包含频率字的14个LSB,下次写入则包含14个MSB。每个16位字的前两位都是定义将载入该字的频率寄存器,因此对于两次连续写入是完全相同的。有关相应的地址,请参见表10。

在两个字均已载入后,即会写入频率寄存器。表11给出了一个完整28位写操作的示例。

不过,请注意,不允许向同一频率寄存器连续写入28位数据,而应在频率寄存器之间切换来执行此类功能。当B28 = 0时,28位频率寄存器用作两个14位寄存器,其中一个包含14个MSB,另一个则包含14个LSB。这意味着,可单独更新频率字的14个MSB而不影响14个LSB,反之亦然。要更新14个MSB或14个LSB,只需向相应的频率地址执行一次写入即可。控制位DB12 (HLB)告知AD9834要更新的位是14个MSB还是14个LSB。 |

| DB12 | HLB |

此控制位使用户可以连续载入频率寄存器的MSB或LSB而忽略余下的14位。如果无需完整的28位分辨率,这点将很有用。HLB应与DB13 (B28)一起使用。此控制位指示载入的14位是传输至所寻址频率寄存器的14个MSB还是14个LSB。DB13 (B28)必须设为0,以便能够单独地更改频率字的MSB和LSB。当DB13 (B28) = 1时,此控制位会被忽略。 HLB = 1允许写入所寻址频率寄存器的14个MSB。 |

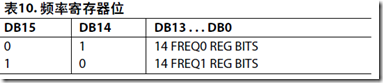

| DB11 | FSEL | FSEL bit定义相位累加器中使用的是FREQ0寄存器还是FREQ1寄存器。请参见表8来选择频率寄存器。 |

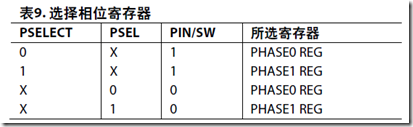

| DB10 | PSEL |

PSEL bit定义是将PHASE0寄存器还是PHASE1寄存器的数据增加到相位累加器的输出。请参见表9来选择相位寄存器。

|

| DB9 | PIN/SW |

可利用软件或硬件实现选择频率和相位寄存器、复位内部寄存器和关断DAC等功能。PIN/SW选择这些功能的控制源。 PIN/SW = 1表示将使用相应的控制引脚来控制此类功能。 |

| DB8 | RESET |

RESET = 1时可将内部寄存器复位至0,这对应于中间电平的模拟输出。 |

| DB7 | SLEEP1 |

当SLEEP1 = 1时,内部MCLK被禁用。由于NCO不再执行累加,因此DAC输出仍保持其预设值。 |

| DB6 | SLEEP12 |

SLEEP12 = 1关断片内DAC。当AD9834用于输出DAC数据的MSB时,这点很有用。 |

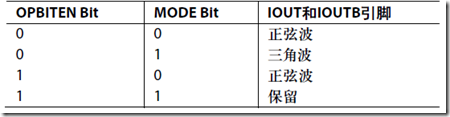

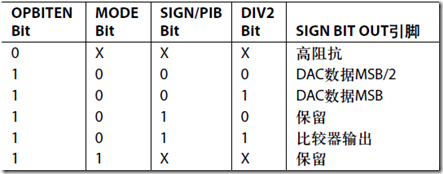

| DB5 | OPBITEN |

此bit的功能是控制是否通过SIGN BIT OUT引脚提供输出。如果用户不使用SIGN BIT OUT引脚,此bit应保持为0。 |

| DB4 | SIGN/PIB | 此bit的功能是控制将通过SIGN BIT OUT引脚提供的具体输出。 SIGN/PIB = 1时,片内比较器与SIGN BIT OUT相连。DAC的正弦波输出经过滤波后,便可将该波形施加于比较器来产生方波波形。见表17。  SIGN/PIB = 0时,DAC数据的MSB(或MSB/2)与SIGN BIT OUT引脚相连。Bit DIV2控制输出的是MSB还是MSB/2。 SIGN/PIB = 0时,DAC数据的MSB(或MSB/2)与SIGN BIT OUT引脚相连。Bit DIV2控制输出的是MSB还是MSB/2。 |

| DB3 | DIV2 |

DIV2应与SIGN/PIB和OPBITEN一起使用。见表17。 |

| DB2 | 保留 | 此位总是清0。 |

| DB1 | MODE |

此bit的功能是控制将通过IOUT引脚/IOUTB引脚提供的具体输出。如果控制位OPBITEN = 1,此位应清0。

|

| DB0 | 保留 | 此位总是清0。 |

五、STM32F103驱动代码

#ifndef __AD9834_H

#define __AD9834_H #include "stm32f10x.h"

#include "pbdata.h"

#include "gpio.h" #define FSYNC Pin9

#define SDATA Pin10

#define SCLK Pin11

#define RESET Pin12 #define FCLK 50 enum Phase

{

Sine,

Triangle,

Square

}; void Ad9834_init(enum Phase ph,u32 freq);

void Send_Phase(void);

void Ad9834_Send_Freq(u16 Freq_word);

void Ad9834_Send_Con(u16 Con_word); #endif /* __DAC_H */

#include "ad9834.h"

#include "math.h" void Ad9834_init(enum Phase ph,u32 freq)

{

u32 fre= (u32)freq / 20000.0 * pow(2,28) - 1; u16 fre_high = fre / 0x4000 + 0x4000;

u16 fre_low = fre % 0x4000 + 0x4000; set_out(GPIOG, FSYNC | SDATA | SCLK | RESET); set_outH(GPIOG,FSYNC);

set_outH(GPIOG,SCLK); set_outH(GPIOG,RESET);

delay_us(10);

set_outH(GPIOG,RESET);

delay_us(10);

set_outL(GPIOG,RESET);

delay_ms(10); if(ph==Sine)

{

Ad9834_Send_Con(0x2038);

}

else if(ph==Triangle)

{

Ad9834_Send_Con(0x2002);

}

else

{

Ad9834_Send_Con(0x2020);

}

delay_us(10);

Ad9834_Send_Freq(fre_low);

delay_us(10);

Ad9834_Send_Freq(fre_high); // Send_Phase();

} void Ad9834_Send_Con(u16 Con_word)

{

u8 i; set_outL(GPIOG,FSYNC);

set_outH(GPIOG,SCLK); for(i=0;i<16;i++)

{

if(Con_word & 0x8000)

{

set_outH(GPIOG,SDATA);

}

else

{

set_outL(GPIOG,SDATA);

}

Con_word<<=1; set_outL(GPIOG,SCLK);

delay_us(10);

set_outH(GPIOG,SCLK);

} set_outH(GPIOG,FSYNC); } void Ad9834_Send_Freq(u16 Freq_word)

{

u8 i;

set_outL(GPIOG,FSYNC);

set_outH(GPIOG,SCLK); for(i=0;i<16;i++)

{

if((Freq_word & 0x8000) == 0x8000)

{

set_outH(GPIOG,SDATA);

}

else

{

set_outL(GPIOG,SDATA);

} Freq_word<<=1; set_outL(GPIOG,SCLK);

delay_us(10);

set_outH(GPIOG,SCLK);

} set_outH(GPIOG,FSYNC); } void Send_Phase(void)

{

Ad9834_Send_Con(0xC000);

}

电赛总结(四)——波形发生芯片总结之AD9834的更多相关文章

- 电赛总结(四)——波形发生芯片总结之AD9854

一.特性参数 ·300M内部时钟频率 ·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作 ·正交的双通道12位D/A转换器 ·超高速 ...

- 电赛总结(四)——波形发生芯片总结之AD9851

一.特性参数 1.180 MHz时钟速率参考时钟具有6倍倍乘器.芯片具有高性能10位DAC和高速滞后比较器 2.+2.7 V至+5.25 V单电源工作 3.正常输出工作频率范围为 0-72MHz ; ...

- 【系列】关于NJUPT电赛自控方向第一次积分赛的总结

本人是NJUPT电子科学与技术专业大一摸鱼狗一枚.本博客旨在总结与分享个人准备电赛所学知识,同时也是为了防止遗忘,锻炼写文章的能力.目前电赛方向为自控方向.主要研究方向为单片机.图像处理.自动控制相关 ...

- TI MSP430工程配置及2019年电赛A题编程示例(使用430 F5529)

配置 第一步:右击工程,选择Options 第二步:在General Options的Target选项卡里选择对应的器件Device,这里是MSP430G2231 第三步:在Debugger里选择FE ...

- NOI.AC NOIP模拟赛 第四场 补记

NOI.AC NOIP模拟赛 第四场 补记 子图 题目大意: 一张\(n(n\le5\times10^5)\)个点,\(m(m\le5\times10^5)\)条边的无向图.删去第\(i\)条边需要\ ...

- noi2019模拟测试赛(四十七)

noi2019模拟测试赛(四十七) T1与运算(and) 题意: 给你一个序列\(a_i\),定义\(f_i=a_1\&a_2\&\cdots\&a_i\),求这个序列的所 ...

- 【春训团队赛第四场】补题 | MST上倍增 | LCA | DAG上最长路 | 思维 | 素数筛 | 找规律 | 计几 | 背包 | 并查集

春训团队赛第四场 ID A B C D E F G H I J K L M AC O O O O O O O O O 补题 ? ? O O 传送门 题目链接(CF Gym102021) 题解链接(pd ...

- 通过Dapr实现一个简单的基于.net的微服务电商系统(四)——一步一步教你如何撸Dapr之订阅发布

之前的章节我们介绍了如何通过dapr发起一个服务调用,相信看过前几章的小伙伴已经对dapr有一个基本的了解了,今天我们来聊一聊dapr的另外一个功能--订阅发布 目录:一.通过Dapr实现一个简单的基 ...

- 电赛总结(二)——AD芯片总结之AD7715

一.特性参数 1.16位无失真AD转换器 2.增益可调,在1,2,32,128可切换. 3.数字地和模拟地分开,可以减少噪声. 4.具有较大的输出电流,有比较好的带载能力. 二.管脚排列 三.引脚功能 ...

随机推荐

- Java设计原则:面向接口的设计

前言:在一个面向对象的系统中,系统的各种功能是由许许多多的不同对象协作完成的.在这种情况下,各个对象内部是如何实现对系统设计人员来说就不那么重要:而各个对象之间的协作关系则成为系统设计的关键.小到不同 ...

- linux下面覆盖文件,如何实现直接覆盖,不提示

转自:http://w-tingsheng.blog.163.com/blog/static/2505603420124309130528/ cp覆盖时,无论加什么参数-f之类的还是提示是否覆盖,当文 ...

- 【原创】angularjs1.3.0源码解析之directive

# Angular指令编译原理 前言 angular之所以使用起来很方便,是因为通常我们只需要在html里面引入一个或多个(自定义或内置的)指令就可以完成一个特定的功能(这也是angular推荐的方式 ...

- 2013 ACM/ICPC Asia Regional Chengdu Online 1004 Minimum palindrome

Minimum palindrome Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Other ...

- Nginx 开启PATHINFO支持ThinkPHP框架实例

ThinkPHP支持通过PATHINFO和URL rewrite的方式来提供友好的URL,只需要在配置文件中设置 'URL_MODEL' => 2 即可.在Apache下只需要开启mod_rew ...

- MYSQL主从数据库搭建

sc delete "服务名" 删除服务 环境: (以下是我这次搭建所使用的环境) 主数据库: 系统:ubuntu : MYSQL 5.1.63 :ip:192.1 ...

- 一个csrf实例漏洞挖掘带你了解什么是csrf

[-]CSRF是个什么鬼? |___简单的理解: |----攻击者盗用了你的身份,以你的名义进行某些非法操作.CSRF能够使用你的账户发送邮件,获取你的敏感信息,甚至盗走你的财产. |___CSRF攻 ...

- Mysql增删改

改 UPDATE tbl_name SET 字段名=值,...[WHERE 条件][ORDER BY 字段名称][LIMIT限制条数] --更新用户名为4位的用户,让其以有年龄-3 UPDATA SE ...

- 使用twisted.web实现代理服务器

简单的实现谷歌的代理: 架构就是下面这么简单. ================= my server outside GFW | <----------------------> ...

- django-cms 代码研究(五)深入(代码结构)

前言: 前戏已经做得比较充分了,下面我们开始步入正题. 代码结构: cms |--admin (猜测是admin界面的二次开发和改良) |--cache (猜测是缓存机制的处理) |--extensi ...