基于FPGA的电压表与串口通信(上)

实验原理

该实验主要为利用TLC549采集模拟信号,然后将模拟信号的数字量通过串口发送到PC上上位机进行显示,使用到的TLC549驱动模块在进阶实验已经使用到了,串口模块在基础实验也已经使用到了,本实验主要是做一个综合,将数据流进行一个整合。

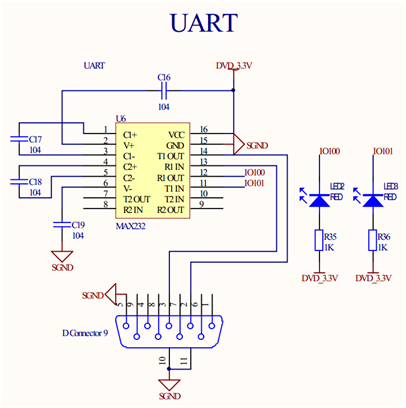

硬件原理图

实验代码

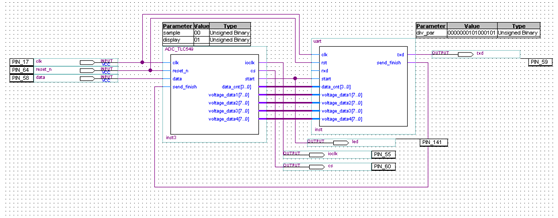

顶层文件

TLC549驱动

|

/******************************************************************************* **----------------------------文件信息-------------------------- ** 文件名称:ADC_TLC549.v ** 功能描述:使用AD芯片TLC549采集模拟信号 ** 操作过程:将模拟信号接到TLC549的输入管脚上 *******************************************************************************/ module ADC_TLC549 ( clk,//系统50MHZ时钟 reset_n,//复位 ioclk,//AD TLC549的时钟 data,//AD TLC549的数据口 cs,//AD TLC549的片选择 segcs,//数码管的为选择 段码 send_finish,//发送完成标志 start,//开始采集信号 data_cnt,//数据位标志 voltage_data1,//采集的电压数据 voltage_data2,//采集的电压数据 voltage_data3,//采集的电压数据 voltage_data4 //采集的电压数据 ); input clk;//系统50MHZ时钟 input reset_n;//复位 input data;//AD TLC549的数据口 input send_finish;//发送完成标志 output cs;//AD TLC549的数据口 output ioclk;//AD TLC549的时钟 output start;//开始采集信号 ] voltage_data1;//采集的电压数据 ] voltage_data2;//采集的电压数据 ] voltage_data3;//采集的电压数据 ] voltage_data4;//采集的电压数据 ] data_cnt;//数据位标志 ]segdata; ]segcs; ] voltage_data1;//采集的电压数据 ] voltage_data2;//采集的电压数据 ] voltage_data3;//采集的电压数据 ] voltage_data4;//采集的电压数据 ] data_cnt; // reg[7:0] voltage_data; ] segcs; ]segdata; reg start; reg cs,ioclk,clk1k,clk1ms; ] count; ] count1ms; ] cnt; ] number; ] state; ] dataout; ] tenvalue; parameter sample=2'b00, display=2'b01; /**********产生100k的采集时钟信号*********/ always@(posedge clk) begin ) count<=count+1'b1; else begin ; ioclk<=~ioclk; end end /*******产生周期为1ms即1kHz的信号*********/ always@(posedge clk) begin if(count1ms>25'd25000) begin clk1ms<=~clk1ms; ; end else count1ms<=count1ms+1'b1; end /*********AD采样程序**************/ always@(negedge ioclk ornegedge reset_n) begin if(reset_n ==1'b0) begin start<=1'b0; state<=sample; ;//关AD片选 ; ; ; end else begin case(state) sample: begin ; start<=1'b0; ],data}; if(cnt>4'd7) begin ; state<=display; end else begin cnt<=cnt+1'b1; state<=sample; end end display: begin ;//关AD片选 ;// //得到采集的数据 start<=1'b1; )+8'd48;//个位 )+8'd48;//十位 )+8'd48;//百位 )+8'd48;//千位 if(send_finish ==1'b1) state<=sample; else state<=display; end default: state<=display; endcase end end /***********2进制转十进制函数*************/ 位的数字 ] datain; begin case(datain) 4'b00000000: tendata=4'd0;//0 4'b00000001: tendata=4'd1;//1 4'b00000010: tendata=4'd2;//2 4'b00000011: tendata=4'd3;//3 4'b00000100: tendata=4'd4;//4 4'b00000101: tendata=4'd5;//5 4'b00000110: tendata=4'd6;//6 4'b00000111: tendata=4'd7;//7 4'b00001000: tendata=4'd8;//8 4'b00001001: tendata=4'd9;//9 4'b00001010: tendata=4'd10;// 4'b00001011: tendata=4'd11;// 4'b00001100: tendata=4'd12; 4'b00001101: tendata=4'd13; 4'b00001110: tendata=4'd14; 4'b00001111: tendata=4'd15; default:tendata=8'bzzzz_zzzz; endcase end endfunction /*********十进制转LED段选函数*********/ 位的数字 ] datain; begin case(datain) 4'd0: leddata=8'b11000000;//0 4'd1: leddata=8'b11111001;//1 4'd2: leddata=8'b10100100;//2 4'd3: leddata=8'b10110000;//3 4'd4: leddata=8'b10011001;//4 4'd5: leddata=8'b10010010;//5 4'd6: leddata=8'b10000010;//6 4'd7: leddata=8'b11111000;//7 4'd8: leddata=8'b10000000;//8 4'd9: leddata=8'b10010000;//9 4'd10: leddata=8'b10111111;//- 4'd11: leddata=8'b01111111;//. default:leddata=8'bzzzz_zzzz; endcase end endfunction /********数码管扫描函数*************/ always@(posedge clk1ms) begin ; else begin ; case(number) 4'd0: begin );//个位 segcs<=4'b1110; end 4'd1: begin );//十位 segcs<=4'b1101; end 4'd2: begin );//百位 segcs<=4'b1011; end 4'd3: begin );//千位 segcs<=4'b0111; end 4'd4: begin segdata<=leddata(4'd11);//. 显示小数点 segcs<=4'b0111; end endcase end end endmodule |

UART通信

|

/******************************************************************************* ** 文件名称:uart.v 位起始位,8个数据位,1个结束) *******************************************************************************/ module uart( clk, rst, rxd, txd, start, data_cnt, voltage_data1, voltage_data2, voltage_data3, voltage_data4, send_finish ); input clk;//系统50MHZ时钟 input rst;//复位 input rxd;//串行数据接收端 output txd;//串行数据发送端 input start;//开始采集信号 ] data_cnt;//数据位标志 ] voltage_data1;//采集的电压数据 ] voltage_data2;//采集的电压数据 ] voltage_data3;//采集的电压数据 ] voltage_data4;//采集的电压数据 output send_finish;//发送完成标志 倍波特率的时钟 ] div8_tras_reg;//该寄存器的计数值对应发送时当前位于的时隙数 ] state_tras;//发送状态寄存器 reg clkbaud_tras;//以波特率为频率的发送使能信号 倍波特率为频率的时钟,它的作用是将发送或接受一个bit的时钟周期分为8个时隙 reg trasstart;//开始发送标志 reg send_finish; reg txd_reg;//发送寄存器 ] rxd_buf;//接受数据缓存 ] txd_buf;//发送数据缓存 ] send_state;//发送状态寄存器 parameter div_par=16'h145; //分频参数,其值由对应的波特率计算而得,按此参数分频的时钟频率是波倍特率的8 的波特率,即分频出的时钟频率是9600*8 (CLK50M) assign txd = txd_reg; // assign send_state=data_cnt; 倍波特率的时钟*********/ always@(posedge clk ) begin if(!rst) ; elsebegin if(div_reg==div_par-1'b1) ; else div_reg<=div_reg+1'b1; end end always@(posedge clk) begin if(!rst) ; elseif(div_reg==div_par-1'b1) 倍波特率的时钟:clkbaud8x end // *******************************/ always@(posedge clkbaud8x ornegedge rst)//clkbaud8x begin if(!rst) ; elseif(trasstart) 倍波特率的时钟下加1循环 end always@(div8_tras_reg) begin ) 个时隙,发送使能信号有效,将数据发出 else ; end // *********发送数据模块***************/ always@(posedge clkbaud8x ornegedge rst)//clkbaud8x begin if(!rst) begin ;//发送寄存器置高 ;//开始发送标志置低 txd_buf<=8'h00;//发送缓存器清零 ;//发送状态寄存器清零 send_finish <=1'b0; send_state<=4'd0; end else if(start ==1'b1) case(state_tras) 4'b0000:begin//发送起始位 send_finish <=1'b0; if(!trasstart&&send_state<4'd7) ; elseif(send_state<4'd7)begin if(clkbaud_tras)begin ; state_tras<=state_tras+1'b1; end end elsebegin ; end end 位 if(clkbaud_tras)begin ]; ]; state_tras<=state_tras+1'b1; end end 位 if(clkbaud_tras)begin ]; ]; state_tras<=state_tras+1'b1; end end 位 if(clkbaud_tras)begin ]; ]; state_tras<=state_tras+1'b1; end end 位 if(clkbaud_tras)begin ]; ]; state_tras<=state_tras+1'b1; end end 位 if(clkbaud_tras)begin ]; ]; state_tras<=state_tras+1'b1; end end 位 if(clkbaud_tras)begin ]; ]; state_tras<=state_tras+1'b1; end end 位 if(clkbaud_tras)begin ]; ]; state_tras<=state_tras+1'b1; end end 位 if(clkbaud_tras)begin ]; ]; state_tras<=state_tras+1'b1; end end 4'b1001:begin//发送停止位 if(clkbaud_tras)begin ; txd_buf<=8'h00; state_tras<=state_tras+1'b1; end end 4'b1111:begin if(clkbaud_tras)begin state_tras<=state_tras+1'b1; send_state<=send_state+1'b1; ; case(send_state) 4'b0000: txd_buf<=voltage_data4;//个位 4'b0001: txd_buf<=8'd46;//小数点 4'b0010: txd_buf<=voltage_data3;//十位 4'b0011: txd_buf<=voltage_data2;//百位 4'b0100: txd_buf<=voltage_data1;//千位 4'b0101: txd_buf<=8'd86;//"V" 4'b0110: begin txd_buf<=8'd10;//换行符 send_finish <=1'b1; send_state<=4'b0000; end default: txd_buf<=8'd0; endcase end end default:begin if(clkbaud_tras)begin state_tras<=state_tras+1'b1; ; end end endcase end endmodule |

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

基于FPGA的电压表与串口通信(上)的更多相关文章

- 基于FPGA的电压表与串口通信(下)

实验操作 上电 接入5V电源,用配套的线,USB那端接电脑即可: 电源开关 按下电源开关 接串口线 接下载线 现在电脑装串口线驱动 R340qd.zip 双击进行安装 设置串口调试助手 Com1要根据 ...

- 基于Arduino和python的串口通信和上位机控制

引言 经常的时候我们要实现两个代码之间的通信,比如说两个不同不同人写的代码要对接,例如将python指令控制Arduino控件的开关,此处使用串口通信是非常方便的,下面笔者将结合自己踩过的坑来讲述下自 ...

- 基于FPGA的红外遥控解码与PC串口通信

基于FPGA的红外遥控解码与PC串口通信 zouxy09@qq.com http://blog.csdn.net/zouxy09 这是我的<电子设计EDA>的课程设计作业(呵呵,这个月都拿 ...

- VS2008基于对话框的MFC上位机串口通信(C++实现)简单例程

首先,在 vs2008 环境下创建 MFC 运用程序 设置项目名称为 ComTest(这个地方随意命名,根据个人习惯),点击确定后,点击下一步 出现如下界面 选择"基于对话框"模式 ...

- 纠错:基于FPGA串口发送彩色图片数据至VGA显示

今天这篇文章是要修改之前的一个错误,前面我写过一篇基于FPGA的串口发送图片数据至VGA显示的文章,最后是显示成功了,但是显示的效果图,看起来确实灰度图,当时我默认我使用的MATLAB代码将图片数据转 ...

- [python] 3 、基于串口通信的嵌入式设备上位机自动测试程序框架(简陋框架)

星期一, 20. 八月 2018 01:53上午 - beautifulzzzz 1.前言 做类似zigbee.ble mesh...无线网络节点性能测试的时候,手动操作然后看表象往往很难找出真正的原 ...

- 【Delphi】基于状态机的串口通信

通信协议 串行通信接口(如RS232.RS485等)作为计算机与单片机交互数据的主要接口,广泛用于各类仪器仪表.工业监测及自动控制领域中. 通信协议是需要通信的双方所达成的一种约定,它对包括数据格式. ...

- C#中缓存的使用 ajax请求基于restFul的WebApi(post、get、delete、put) 让 .NET 更方便的导入导出 Excel .net core api +swagger(一个简单的入门demo 使用codefirst+mysql) C# 位运算详解 c# 交错数组 c# 数组协变 C# 添加Excel表单控件(Form Controls) C#串口通信程序

C#中缓存的使用 缓存的概念及优缺点在这里就不多做介绍,主要介绍一下使用的方法. 1.在ASP.NET中页面缓存的使用方法简单,只需要在aspx页的顶部加上一句声明即可: <%@ Outp ...

- PC和FPGA间的串口通信实现

应用笔记 V1.0 2015/03/26 PC和FPGA间的串口通信实现 概述 本文将介绍PC和FPGA间的串口通信实现的基本思路和Verilog代码,对于通信而言,收发双方都要有相应的控制. ...

随机推荐

- [转]正确配置Linux系统ulimit值的方法

在Linux下面部署应用的时候,有时候会遇上Socket/File: Can't open so many files的问题:这个值也会影响服务器的最大并发数,其实Linux是有文件句柄限制的,而且L ...

- [Java入门笔记] Java语言简介

前言 学习Java有一段时间了,但是一直缺少一个系统的思想,现在重新通过书籍中.网上的文章,视频等资料,整理与回顾Java的知识点. 言归正传,让我们先从了解Java语言开始. Java语言的由来 J ...

- Linux中的SWAP交换分区

大多数 Linux 在系统安装时都会提醒并建议你划分一个 SWAP 交换分区,如果你是从 Windows 切换到 Linux 的新用户,兴许对这个 SWAP 会感到十分疑惑. SWAP 交换分区到底是 ...

- Windows 10 L2TP 809错误

今天不知道为什么,一直工作正常的L2TP不能连接了.我用的是Surface Pro 3,Windows 10 专业版,操作系统一直保持自动更新,而且最近也没有安装什么软件.点击连接后,等一段时间就报8 ...

- [转]关于信息安全认证CISP与CISSP的对比及分析

本文转自:https://www.douban.com/group/topic/89081816/ 最近好多信息安全行业或者打算转行的职场人在纠结学CISP还是学CISSP,我给大家就CISP和CIS ...

- [转]asp.net c# 网上搜集面试题目(附答案)

本文转自:http://www.cnblogs.com/hndy/articles/2234188.html 1.String str=new String("a")和String ...

- 学习图像算法阶段性总结 (附一键修图Demo) 2016.04.19更新demo

今天特别感慨,自己从决定研究图像处理,势必要做出一键修图算法. 经历了,三个多月的书籍积累,三个多月的算法调整以及优化. 人是一种奇怪的动物,当你做不到的时候,你以为做到了,自己会感觉很爽,很有成就感 ...

- Flex:自定义滚动条样式/隐藏上下箭头

Flex组件自定义滚动条的实现 .scrollBar{ downArrowUpSkin:Embed(source="img/mainLeftScrollBar/bar_bottom.png& ...

- uva131 The Psychic Poker Player

The Psychic Poker Player Time Limit: 3000MS 64bit IO Format: %lld & %llu Description In 5-ca ...

- Git版本恢复命令reset(转载)

本博文转载自:http://www.tech126.com/git-reset/: 如果看不懂的话,请在git下练习,如果练习后任然有不懂的,可以留言也可以发送邮件到luoquantao@126.co ...