FIFO的设计与仿真

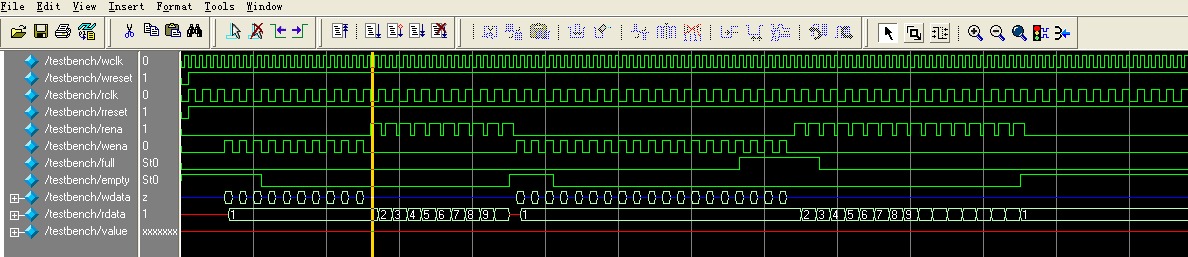

本设计参照齐威王大哥的设计,采用模块化的设计方法,每个模块简单易懂,并进行了每个模块的仿真。最后进行顶层设计,编写了测试激励在modisim上仿真正确,

下面给出代码和测试激励,附上一篇比较好的英文文献。

1 module yibu_fifo(wclk,wreset,wdata,wena,rclk,rena,rdata,rreset,full,empty);

2 parameter DSIZE = 8,

3 ASIZE = 4;

4 input wclk,wreset,rclk,rreset;

5 input wena,rena; //写控制信号 读控制信号

6 input [DSIZE-1:0] wdata; //写数据

7 output[DSIZE-1:0] rdata; //读数据

8 output full,empty ;//写满 读空

9 wire [ASIZE:0] wzz, wzz_syn,rzz,rzz_syn; //特别注意

10 wire [ASIZE-1:0] raddr,waddr; //特别注意

11 fifomem U1(rdata, wdata, waddr, raddr, wena,full, wclk);

12 w_full U2(full, waddr, wzz, rzz_syn, wena, wclk, wreset);

13 r_empty U3(empty, raddr, rzz, wzz_syn, rena, rclk, rreset);

14 syn_w2r U4(wzz,rclk,rreset,wzz_syn);

15 syn_r2w U5(wclk,wreset,rzz,rzz_syn);

16 endmodule

module fifomem (rdata, wdata, waddr, raddr, wena,full, wclk);

parameter DSIZE = 8,

ASIZE = 4;

input wclk;

input [DSIZE-1:0] wdata;

input wena,full;

output [DSIZE-1:0] rdata;

input [ASIZE-1:0] waddr;

input [ASIZE-1:0] raddr;

reg [DSIZE-1:0] mem[0:(1<<ASIZE)-1]; //register

assign rdata=mem[raddr]; //read

always @(posedge wclk) //write

if (wena && !full)

mem[waddr] <= wdata;

endmodule

module r_empty(empty, raddr, rzz, wzz_syn, rena, rclk, rreset);

parameter DSIZE = 8,

ASIZE = 4; //

input rclk, rreset,rena;

input [ASIZE:0] wzz_syn;

output [ASIZE:0] rzz;

output [ASIZE-1:0] raddr;

output empty;

reg empty;

reg [ASIZE:0] rzz;

reg [ASIZE:0] rbin;

wire [ASIZE:0] rgraynext,rbinnext;

//-------------empty产生与raddr产生-------------------

always @(posedge rclk or negedge rreset) // GRAYSTYLE2 pointer

begin

if (!rreset)

{rbin, rzz} <= 0;

else

{rbin, rzz} <= {rbinnext, rgraynext};

end

// Memory read-address pointer (okay to use binary to address memory)

assign raddr = rbin[ASIZE-1:0];

assign rbinnext = rbin + (rena & ~empty);

assign rgraynext = (rbinnext>>1) ^ rbinnext; // FIFO empty when the next rptr == synchronized wptr or on reset

assign rempty_val = (rgraynext == wzz_syn);

always @(posedge rclk or negedge rreset)

begin

if (!rreset)

empty <= 1'b1;

else

empty <= rempty_val;

end

endmodule

module w_full(full, waddr, wzz, rzz_syn, wena, wclk, wreset);

parameter DSIZE = 8,

ASIZE = 4;

input wclk,wreset;

input wena;

input [ASIZE:0] rzz_syn;

output [ASIZE:0] wzz;

output full;

output [ASIZE-1:0] waddr;

reg full;

reg [ASIZE:0] wzz;

reg [ASIZE:0] wbin;

wire [ASIZE:0] wgraynext,wbinnext;

//---------------full产生与waddr产生--------------------

always @(posedge wclk or negedge wreset)

if (!wreset)

{wbin, wzz} <= 0;

else

{wbin, wzz} <= {wbinnext, wgraynext};

// Memory write-address pointer (okay to use binary to address memory)

assign waddr = wbin[ASIZE-1:0];

assign wbinnext = wbin + (wena & ~full); assign wgraynext = (wbinnext>>1) ^ wbinnext; //bin to g

assign wfull_val = (wgraynext=={~rzz_syn[ASIZE:ASIZE-1], rzz_syn[ASIZE-2:0]}); // full always @(posedge wclk or negedge wreset)

if (!wreset)

full <= 1'b0;

else

full <= wfull_val;

endmodule

module syn_r2w(wclk,wreset,rzz,rzz_syn);

parameter DSIZE = 8,

ASIZE = 4;

input wclk,wreset;

input [ASIZE:0] rzz;

output [ASIZE:0] rzz_syn;

reg [ASIZE:0] rzz_syn;

reg [ASIZE:0] rzz_syn_1; //两级同步

always @(posedge wclk or negedge wreset)

if(!wreset)

{rzz_syn,rzz_syn_1} <= 0;

else

{rzz_syn,rzz_syn_1} <= {rzz_syn_1,rzz};

endmodule

module syn_w2r (wzz,rclk,rreset,wzz_syn);

parameter DSIZE = 8,

ASIZE = 4;

input rclk,rreset;

input [ASIZE:0] wzz;

output [ASIZE:0] wzz_syn;

reg [ASIZE:0] wzz_syn;

reg [ASIZE:0] wzz_syn_1; //两级同步

always @(posedge rclk or negedge rreset)

if (!rreset)

{wzz_syn,wzz_syn_1} <= 0;

else

{wzz_syn,wzz_syn_1} <= {wzz_syn_1,wzz};

endmodule

module testbench;

reg wclk,wreset;

reg rclk,rreset;

reg rena;

reg wena;

wire full;

wire empty;

reg [7:0] wdata;

wire [7:0] rdata;

reg [7:0] value;

yibu_fifo FIFO(wclk,wreset,wdata,wena,rclk,rena,rdata,rreset,full,empty);

// read

task read_word;

begin

@(negedge rclk);

rena = 1;

@(posedge rclk)

#5;

rena = 0;

end

endtask

//write

task write_word;

input [7:0] value;

begin

@(negedge wclk);

wdata = value;

wena = 1;

@(posedge wclk);

#5;

wdata = 8'hzz;

wena = 0;

end

endtask

//write clock

initial begin

wclk = 0;

forever begin

#5 wclk = 1;

#5 wclk = 0;

end

end

//read clock

initial begin

rclk = 0;

forever begin

#10 rclk = 1;

#10 rclk = 0;

end

end

// process

initial

begin

test1;

end

task test1;

begin

wdata = 8'hzz;

wena = 0;

rena = 0;

wreset = 0;

rreset= 0;

#10 wreset = 1;rreset=1;

#50;

//写入10个数据

write_word (8'h01);

write_word (8'h02); //正常

write_word (8'h03);

write_word (8'h04);

write_word (8'h05);

write_word (8'h06);

write_word (8'h07);

write_word (8'h08);

write_word (8'h09);

write_word (8'h0A);

repeat (10)

begin

read_word; // read 10

end

write_word (8'h01);

write_word (8'h02);

write_word (8'h03);

write_word (8'h04);

write_word (8'h05);

write_word (8'h06);

write_word (8'h07);

write_word (8'h08);

write_word (8'h09);

write_word (8'h0A);

write_word (8'h0B);

write_word (8'h0C);

write_word (8'h0D);

write_word (8'h0E);

write_word (8'h0F);

write_word (8'h10);

write_word (8'h11);

write_word (8'h12);

write_word (8'h13); // 写满溢出

repeat (16)

begin

read_word; // 读空

end

end

endtask

endmodule

2013-03-24

2013-03-24

英文文献http://www.sunburst-design.com/papers/

FIFO的设计与仿真的更多相关文章

- 异步fifo的设计

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 一.FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数:fifo深度(简单来说就是需要存多少个数据) ...

- 异步fifo的设计(FPGA)

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 一.FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数:fifo深度(简单来说就是需要存多少个数据) ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- Fixed-Point Designer(设计、仿真和分析定点系统)

Fixed-Point Designer™ 提供开发定点和单精度算法所需的数据类型和工具,以在嵌入式硬件上进行性能优化.Fixed-Point Designer 会分析您的设计并提供建议的数据类型和属 ...

- 基于TDA4863-2的单级PFC反激LED电源设计与仿真

LED是一个非线性器件,正向电压的微小变化会引起电流的巨大变化:LED是一个半导体二极管,其伏安特性随温度变化而变化(-2mV/℃),假如温度升高,在恒压驱动下LED的电流会增加.长期超过额定电流工作 ...

- 同步FIFO的设计

module scfifo #( , ) ( input clk, input rst_n, input wren, input rden, :] din, :] dout, output full, ...

- Verilog设计异步FIFO

转自http://ninghechuan.com 异步FIFO有两个异步时钟,一个端口写入数据,一个端口读出数据.通常被用于数据的跨时钟域的传输. 同步FIFO的设计.一个时钟控制一个计数器,计数器增 ...

- 基于FPGA的异步FIFO设计

今天要介绍的异步FIFO,可以有不同的读写时钟,即不同的时钟域.由于异步FIFO没有外部地址端口,因此内部采用读写指针并顺序读写,即先写进FIFO的数据先读取(简称先进先出).这里的读写指针是异步的, ...

- FIFO设计思考之一

不管同步FIFO还是异步FIFO,设计难点是full/empty状态flag的正确性. 要保证任何情况 FULL时NO WRITE,EMPTY时NO READ.overflow / underflow ...

随机推荐

- Linux ping 不通 域名 添加DNS

修改路由配置文件 vi /etc/resolv.conf # Generated by NetworkManager #NDS nameserver 192.168.32.2 redhat7 系统优化 ...

- 05003_Linux的基本命令

1.目录结构 Linux的目录结构:Linux各目录及每个目录的详细介绍 链接:Linux各目录及每个目录的详细介绍 密码:84ab 2.LInux的基本命令 (1)目录切换命令 ①root是超级管理 ...

- 2015 Multi-University Training Contest 3 hdu 5326 Work

Work Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others)Total Submis ...

- 50个经典Sql语句

50个经典Sql语句 --1.学生表 Student(S,Sname,Sage,Ssex) --S 学生编号,Sname 学生姓名,Sage 出生年月,Ssex 学生性别 --2.课程表 Cours ...

- Java设置Client Socket链接Server超时时间

Java设置Client Socket链接Server超时时间 学习了:http://blog.csdn.net/tterminator/article/details/52494141 http:/ ...

- Android configChanges使用方法

1. 在manifest文件里使用activity的默认属性.横屏竖屏时,惠重复调用onDestory和onCreate 造成不必要的开销.Android默认如此应该是为了适配不同的xml布局 ...

- 使用React Hook后的一些体会

一.前言 距离React Hook发布已经有一段时间了,笔者在之前也一直在等待机会来尝试一下Hook,这个尝试不是像文档中介绍的可以先在已有项目中的小组件和新组件上尝试,而是尝试用Hook的方式构建整 ...

- angularjs 表单校验

<!DOCTYPE HTML> <html ng-app="myApp"> <head> <meta http-equiv="C ...

- android删除表和清空表

删除某一表: //删除某一个表 public void dropTable(SQLiteDatabase db){ db.execSQL("drop from tab_name") ...

- [HNOI2008] GT考试(DP+矩阵快速幂+KMP)

题目链接:https://www.luogu.org/problemnew/show/P3193#sub 题目描述 阿申准备报名参加 GT 考试,准考证号为 N 位数 X1,X2…Xn(0 <= ...