【CPU】理解CPU

CPU,全称Central Processing Unit,即中央处理器。

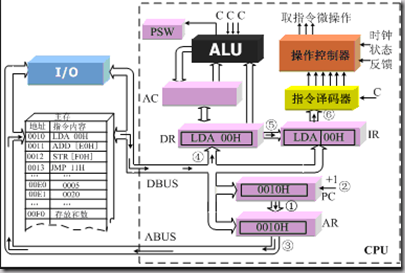

何为CPU? 计算机必须能够自动地从主存中取出一条条指令执行,专门来执行指令的就是CPU。

一、指令的执行过程

为了理解CPU的工作原理,我们首先了解一下指令的执行过程:

(1)取指令并计算下一条地址。(程序计数器PC、指令寄存器IR)

应该明确的是,指令存放在地址连续的内存空间中,其地址是由PC即程序计数器给出。故指令执行的第一步就是根据这个PC中的地址去内存中找到指令,并取出它,放在一个指令寄存器(IR)中,以供后续操作。然后,计算下一条指令地址,赋给PC。

(2)对指令操作码进行译码。(指令译码器)

不同指令的操作码不同,实现的功能也不同。这个过程就是根据不同的指令中包含的操作码(op),产生不同的控制信号,在物理逻辑上,控制实现不同的操作。

(3)计算源操作数地址并取源操作数。

简单讲就是,根据具体指令,确定寻址方式,再根据寻址方式去确定源操作数地址计算方式,再根据这个地址去找源操作数,找到后取它。

(4)数据操作。

对源操作数进行具体的数据操作。如可能是进行加减乘除运算。

(5)目的操作数地址计算并存结果。

与(3)对应,根据寻址方式计算目的操作数地址,再将(4)的结果写入目的地址处。

需要说明的是,对所有指令,(1)(2)过程都是必不可少的,而(3)(4)(5)则由具体的指令操作码产生的控制信号控制,可能有也可能不执行。如jump跳转指令就无需(3)-(5)。

二、CPU的基本功能和基本组成概述

不管CPU多复杂,其组成部分我都可以分成控制部件(control unit)和数据通路(datapath)。先对这两个概念简单的了解:

1. 数据通路

数据通路是指指令执行过程中数据所经过的路径,包括路径上的部件,如ALU(算数部件)、通用寄存器、状态寄存器等等。数据通路由控制部件进行控制。形象的说,datapath是数据流动的“路”,当然路上有许多“关卡”,“关卡”的开关由控制部件决定,而控制部件又是由指令产生的控制信号决定的。

2.控制部件

如上面提到的,控制部件根据具体指令功能的不同,产生对数据通路的控制信号,并正确控制指令的执行过程。

一个简易的CPU逻辑图是这样的:

(图片来自网络)

可以从图中大概看到,主要控制逻辑是:

程序计数器PC,即指令计数器,指令指针IP,存放指令的地址。顺序执行时,PC中拿出来地址,通过地址线,去拿地址,然后根据地址,指令寄存器通过数据线去取出这条指令,并存放在指令寄存器IR中,指令寄存器将指令传送指令译码器,译码器将操作码OP译码,传送给操作控制信号形成部件,并生成相应的控制信号。

上述过程是在时序信号的控制下进行的;这个时序信号,是由专门的“时序信号产生部件”产生,而这个部件最终由“脉冲源”与“启停控制线”控制。即,脉冲源产生一定频率的脉冲信号,作为整个机器的时钟脉冲,这是整个CPU的基准信号。启停控制线是在需要时开放或封锁脉冲源的部件,以此来控制时序信号的产生和停止。而时序信号产生部件就是以时钟脉冲为基准,产生不同指令对应的周期、节拍、工作脉冲等时序信号,实现对机器指令执行过程的控制。

生成控制信号后,则会根据这个信号,去控制其他逻辑部件,如取操作数、运算、送目的地址等。

三、CPU数据通路

上面提到了,数据通路就是数据存储、处理和传送的途径。讨论实现的控制部件是更加深入的学习内容,对于理解CPU逻辑,仅仅需要知道它完成了什么功能;而数据通路的理解是彻底理解CPU工作流程的不可或少的部分。下面详细分析数据通路。

指令执行过程中用到的元件有两类:组合逻辑元件(操作元件如ALU),和存储元件(也称状态元件,如通用寄存器)。

1. 组合逻辑元件

即输出只取决于当前的输入的元件。如加法器、多路选择器、算术逻辑部件、译码器等等。他们有的需要控制信号参与,有的则不需要,但他们的共同之处就在于,给定输入,立马得到输出。

2. 状态元件

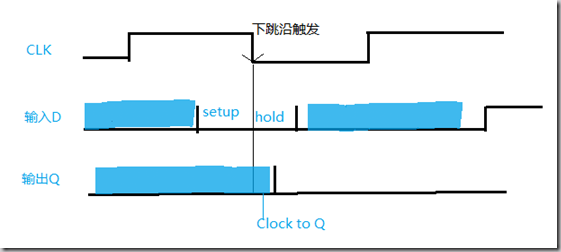

具有存储功能的元件,输入状态在时钟控制下被写入到电路,并保持输出值不变,直到下一个时钟到达。输入状态由时钟决定何时被写入,输出状态随时可以读出。通过下面的例子分析,相信你能更好的理解。

下面是一个简单的状态单元:D触发器,时钟输入clk控制时钟到达,状态输入D和状态输出Q。

示意图

逻辑示意图

上面的图示,假定触发在时钟信号下跳沿进行,即当时钟信号下跳时,输入D被写入电路。而这一过程(输入被允许写入电路)之前,有一个setup time(建立时间),即,输入D的状态要保持稳定有效,稳住输入信号,在时钟信号下跳沿到来一段时间内,有一个Hold time(保持时间),即这段时间内,输入端D要保持稳定不变,这是为了等待输出端Q的延迟(为了确保Q是输入D的正确输出)。即下跳沿来临之时,输出端Q仍然有一个Clock to Q time,即锁存延迟,即在hold time内,输出经过Clock to Q time开始生效。Clock time就是输出开始生效的点。

3. 数据通路与时序控制

每个指令的执行过程,都有若干个操作步骤,而这些操作步骤,是有先后顺序的。为了使得正确的执行指令,CPU必须按照时序产生正确的控制信号。不同指令对应的操作步骤所需要的时间长短不一,控制他们考虑合适的时序方式。

1)早期计算机的三级时序控制系统

早期采用机器周期、节拍、脉冲三级时序对数据通路操作进行定时控制。一个指令可以分为取指令、读取操作、执行、写结果等多个基本操作步骤(每个步骤都是一个操作周期),这称为机器周期。需要说明的是,每个机器周期长短不同,比如读写的周期必定比在CPU中操作的周期长。所以,机器周期的长短由工作周期中最长的那个为基础来确定,如以主存工作周期确定。

一个机器周期内同样也要进行若干步动作。比如存储器读写操作中,又必须有发送地址、发读写命令、检测数据有无完备、取数据等等。因此一个机器周期划分为若干个节拍,使得一个动作在一个街拍内完成。

为了产生操作控制信号,并使某些操作在一排时间内配合工作,在一个节拍内设置一个或多个工作脉冲。例如,在一个节拍内完成动作:将一个寄存器的内容传送到另一个寄存器。这时就需要设置先后两个脉冲,以产生打开数据通路脉冲的接受脉冲。

这就是三级时序系统,不过我是没见过这种机器了,因为早已经淘汰了。

2)现代计算机的时钟信号

机器周期的概念已经消失了,现代计算机整个数据通路中的定时信号就是时钟,一个时钟周期就是一个节拍。其工作流程在上面状态元件讲述中已经阐明。

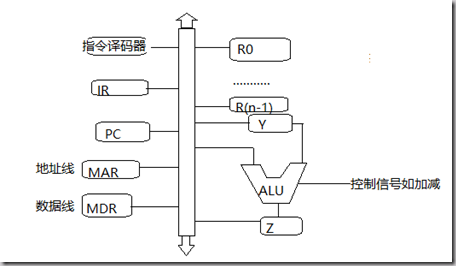

4. 单总线数据通路

意如其名,在CPU内部,将ALU以及所有寄存器通过一条内部的公共总线连接起来,就是单总线数据通路。注意不要把它与外部连接存储器、CPU、IO的外部系统总线混淆。图示如下:

中间就是内部总线。这种结构下,同一时刻仅有一个元件可以将数据传送到总线上,因而效率不高。

对于ALU运算,则必须设置缓存(临时)寄存器Y和Z,因为同一时刻仅有一个元件可以将数据传送到总线上,所以对于两个源操作数的操作,设置Y以缓存一个操作数,设置Z以传送到总线上进而送目标地址。这其中的每一步都是在时钟控制下进行的。

5. 三总线数据通路

提高性能,必须使得每条指令的时钟周期尽量少。为了克服单总线数据通路同一时刻仅仅有一个数据在总线上的缺点,可以采用多总线数据通路。

如三总线数据通路,就可以设置所有通用寄存机在一个“双口寄存器堆”总,允许两个寄存器的内容同时输出到两个不同的总线。

同样的,在ALU运算时,由于有多个总线可以同时传送多个数据,就无需再设置临时缓冲寄存器了。

四、总结

我以一个计算机系学生的角度看待CPU,并没有去通识性的讨论CPU的发展历史、性能和选购,旨在学习基本的底层知识,在高级程序设计当道的同时,学习底层,更好、系统的理解计算机。受知识水平所限,难免有谬误、不当之处,请大家批评指正。

【参考】计算机组成与系统结构(第二版) 袁春风老师主编

【CPU】理解CPU的更多相关文章

- 理解CPU内存管理

概述:从设计层面理解CPU的内存模式,包括段式内存管理.页式内存管理以及虚拟化扩展内存管理.实际上,硬件支持与软件实现从来就不是能分开讲的,比如,Intel CPU架构师在选择CPU的硬件特性时,必然 ...

- 从Java视角理解CPU缓存(CPU Cache)

从Java视角理解系统结构连载, 关注我的微博(链接)了解最新动态众所周知, CPU是计算机的大脑, 它负责执行程序的指令; 内存负责存数据, 包括程序自身数据. 同样大家都知道, 内存比CPU慢很多 ...

- 深入理解CPU和异构计算芯片GPU/FPGA/ASIC (上篇)

王玉伟,腾讯TEG架构平台部平台开发中心基础研发组资深工程师,专注于为数据中心提供高效的异构加速云解决方案.目前,FPGA已在腾讯海量图片处理以及检测领域已规模上线. 随着互联网用户的快速增长,数据体 ...

- 如何理解CPU上下文切换(二)

如何理解CPU上下文切换(二) 1.引 你们好,可爱的小伙伴们.^_^ 多个进程竞争CPU就是一个经常被我们忽视的问题. 你们一定很好奇,进程在竞争CPU的时候并没有真正运行,为什么还会导致系统的负载 ...

- 性能测试必备知识(5)- 深入理解“CPU 上下文切换”

做性能测试的必备知识系列,可以看下面链接的文章哦 https://www.cnblogs.com/poloyy/category/1806772.html 前言 上一篇文章中,举例了大量进程等待 CP ...

- 深入理解CPU和异构计算芯片GPU/FPGA/ASIC (下篇)

3.2.1 CPU计算能力分析 这里CPU计算能力用Intel的Haswell架构进行分析,Haswell架构上计算单元有2个FMA(fused multiply-add),每个FMA可以对256bi ...

- 从Java视角理解CPU缓存和伪共享

转载自:http://ifeve.com/from-javaeye-cpu-cache/ http://ifeve.com/from-javaeye-false-shari ...

- 性能测试必备知识(7)- 深入理解“CPU 使用率”

做性能测试的必备知识系列,可以看下面链接的文章哦 https://www.cnblogs.com/poloyy/category/1806772.html 回顾 CPU 使用率是单位时间内 CPU 使 ...

- [转]物理CPU、CPU核数、逻辑CPU、超线程

转自:http://wulc.me/2016/01/06/物理CPU.CPU核数.逻辑CPU.超线程/ 基本概念 物理CPU: 物理CPU就是插在主机上的真实的CPU硬件,在Linux下可以数不同的p ...

随机推荐

- Gym101138D Strange Queries/BZOJ5016 SNOI2017 一个简单的询问 莫队、前缀和、容斥

传送门--Gym 传送门--BZOJ THUWC2019D1T1撞题可还行 以前有些人做过还问过我,但是我没有珍惜,直到进入考场才追悔莫及-- 设\(que_{i,j}\)表示询问\((1,i,1,j ...

- 小程序解决方案 Westore - 组件、纯组件、插件开发

数据流转 先上一张图看清 Westore 怎么解决小程序数据难以管理和维护的问题: 非纯组件的话,可以直接省去 triggerEvent 的过程,直接修改 store.data 并且 update,形 ...

- 朱晔的互联网架构实践心得S1E4:简单好用的监控六兄弟

朱晔的互联网架构实践心得S1E4:简单好用的监控六兄弟 [下载本文PDF进行阅读] 这里所说的六兄弟只指ELK套件(ElasticSearch+Logstash+Kibana)以及TIG套件(Tele ...

- js中布尔值为false的六种情况

下面6种值转化为布尔值时为false,其他转化都为true 1.undefined(未定义,找不到值时出现) 2.null(代表空值) 3.false(布尔值的false,字符串"false ...

- MySQL的log_bin和sql_log_bin 的区别

利用二进制还原数据库的时候,突然有点纠结,log_bin和sql_log_bin有什么区别呢?行吧,搜搜,结合自己的经验,简单说一下.log_bin:二进制日志. 在 mysql 启动时,通过命令行或 ...

- 最小的N个和(堆)

描述: 有两个长度为N的序列 AB,从AB中各选一个数,可以得到N^2个和,求这N^2个和中最小的N个 输入 5 1 3 2 4 5 6 3 4 1 7 输出 2 3 4 4 5 分析: 首先限定输出 ...

- (第十三周)Final阶段成员贡献分

项目名:食物链教学工具 组名:奋斗吧兄弟 组长:黄兴 组员:李俞寰.杜桥.栾骄阳.王东涵 个人贡献分=基础分+表现分 基础分=5*5*0.5/5=2.5 成员得分如下: 成员 基础分 表现分 个人贡献 ...

- mysql常用命令行操作(一):登陆、退出、查看端口、修改密码、刷新

一.登陆和退出mysql mysql -u root -p # 登陆exit # 退出 二.查看当前mysql的端口号 show global variables like 'port'; 三.查看用 ...

- nodejs 中的一些方法

fs.unlink(path, [callback(err)]) //删除文件操作. //path 文件路径 //callback 回调,传递一个异常参数err. ndoe中解决跨域问题 expres ...

- Bridge (br0) Network on Linux

动手实践虚拟网络 - 每天5分钟玩转 OpenStack(10) - CloudMan - 博客园https://www.cnblogs.com/CloudMan6/p/5296573.html li ...