verilog流水线加法器

- 四位加法器

- 两级加法实现

verilog code

module pipeliningadder(

output reg [3:0] s,

output reg co,

input [3:0] a,

input [3:0] b,

input ci,

input clk,

input rstn

);

reg [3:0] a_tmp;

reg [3:0] b_tmp;

reg [1:0] a_tmp2;

reg [1:0] b_tmp2;

reg ci_tmp;

reg [1:0] s_tmp3;

reg co_low;

reg [1:0] s_low;

reg co_hign;

reg [1:0] s_hign;

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

a_tmp <= 4'b0;

b_tmp <= 4'b0;

ci_tmp <= 1'b0;

end

else

begin //将输入的数据缓存起来

a_tmp <= a;

b_tmp <= b;

ci_tmp <= ci;

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co_low <= 1'b0;

s_low <= 2'b0;

a_tmp2 <= 2'b0;

b_tmp2 <= 2'b0;

end

else

begin //低两位相加,缓存高两位

{co_low,s_low} <= a_tmp[1:0] + b_tmp[1:0] + ci_tmp;

a_tmp2 <= a_tmp[3:2];

b_tmp2 <= b_tmp[3:2];

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co_hign <= 2'b0;

s_hign <= 2'b0;

end

else

begin //高两位相加及与之间的低两位一并输出

{co_hign,s_hign} <= a_tmp2 + b_tmp2 + co_low;

s_tmp3 <= s_low; //寄存上一级的结果

end

end

always@(posedge clk,negedge rstn)

begin

if(!rstn)

begin

co <= 1'b0;

s <= 4'b0;

end

else

begin

{co,s} = {co_hign,s_hign,s_tmp3}; //合并上两级计算结果,输出结果

end

end

endmodule

testbench

module pipeliningadder_tb;

wire [3:0] s;

wire co;

reg [3:0] a;

reg [3:0] b;

reg ci;

reg clk;

reg rstn;

initial

begin

clk = 0;

rstn = 0;

@(posedge clk) rstn = 1;

a = 4'b0000; b = 4'b0000; ci = 0;

@(posedge clk) a = 4'b1111; b = 4'b1111; ci = 0;

@(posedge clk) a = 4'b1100; b = 4'b1001; ci = 0;

@(posedge clk) a = 4'b0111; b = 4'b0110; ci = 0;

@(posedge clk) a = 4'b0101; b = 4'b0101; ci = 1;

@(posedge clk) a = 4'b1110; b = 4'b1001; ci = 1;

@(posedge clk) a = 4'b0010; b = 4'b0110; ci = 1;

@(posedge clk) a = 4'b0110; b = 4'b1101; ci = 1;

@(posedge clk) a = 4'b1110; b = 4'b1110; ci = 1;

@(posedge clk) a = 4'b1100; b = 4'b0110; ci = 1;

@(posedge clk) a = 4'b1100; b = 4'b0101; ci = 1;

@(posedge clk) a = 4'b0011; b = 4'b1010; ci = 1;

@(posedge clk) $finish;

end

always #5 clk = ~clk;

initial begin

$fsdbDumpfile("test.fsdb");

$fsdbDumpvars();

end

pipeliningadder u_pipeliningadder(

.s(s),

.co(co),

.a(a),

.b(b),

.ci(ci),

.clk(clk),

.rstn(rstn)

);

endmodule

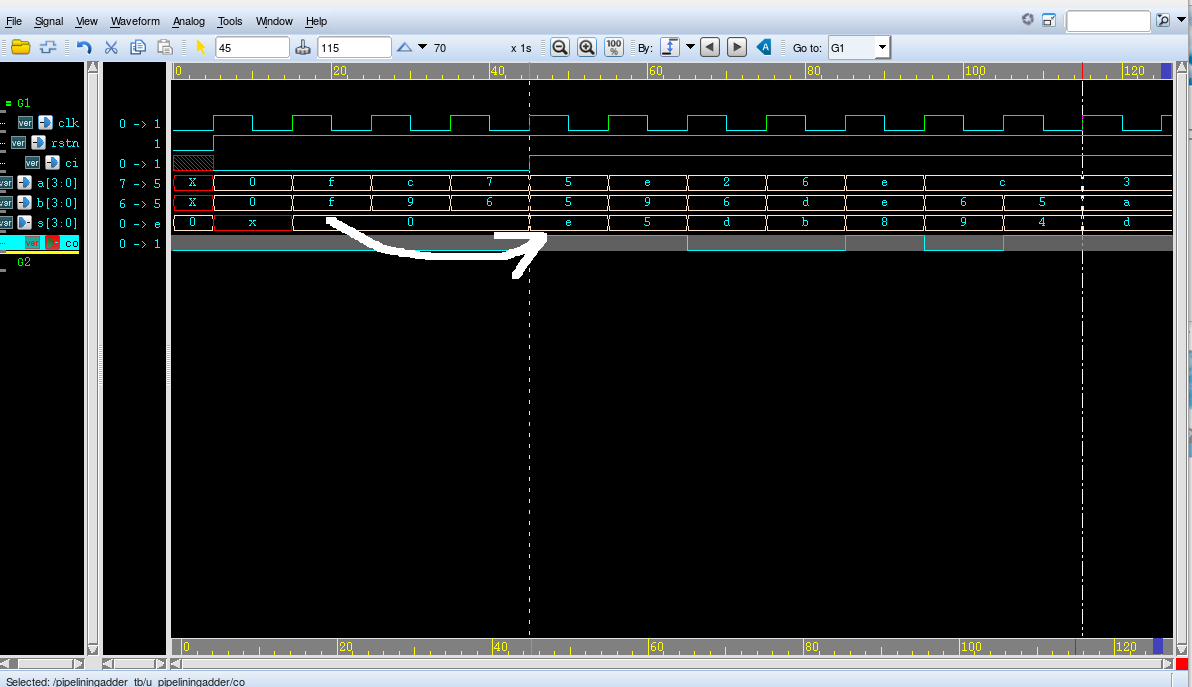

verdi波形查看

总结

使用流水线实现可以缩短关键路径,以提高运算频率,加快运算。

其他相关加法器实现方法:verilog 实现加法器

参考资料

[1]. 加法器的verilog实现

verilog流水线加法器的更多相关文章

- verilog 实现加法器

半加器 如果不考虑来自低位的进位将两个1二进制数相加,称为半加. 实现半加运算的逻辑电路称为半加器. 真值表 逻辑表达式和 \begin{align}\notag s = a{b}' + {a}'b ...

- 【FPGA学习】Verilog之加法器

在fpga工程应用设计中,随处可见加法器,乘法器等等.现在将一些常用模块和心得体会先记录下来,以便日后使用. 一位半加器: module halfadder(cout,sum,a,b); output ...

- verilog设计加法器

概述 本文利用了硬件行为描述.数据流描述.结构描述三种方法分别写了几个加法器 一位半加法器 即两个一位的二进制数相加,得到其正常相加的结果的最后一位. 仿真波形图 硬件行为描述 设计文件 123456 ...

- 流水线(pipe-line)简介

1.什么是流水线设计技术? 答:所谓流水线设计实际上是把规模较大.层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组并暂存数据. K级就是有K个寄存器组,从上到下没有反馈电路. 2.流水线设计的深 ...

- 剑指Offer - 九度1507 - 不用加减乘除做加法

剑指Offer - 九度1507 - 不用加减乘除做加法2013-11-29 20:00 题目描述: 写一个函数,求两个整数之和,要求在函数体内不得使用+.-.*./四则运算符号. 输入: 输入可能包 ...

- 流水线cpu —Verilog HDL

一.准备工作 先看看书(<计算机原理与设计 Verilog HDL版>),搞懂一点原理.然后照着书上的代码写一写(用8.4的就可以了,不用8.6的). 注意mux2x32,mux4,cla ...

- verilog实现16位五级流水线的CPU带Hazard冲突处理

verilog实现16位五级流水线的CPU带Hazard冲突处理 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4292869.html所增加的Hazard处 ...

- sobel流水线操作Verilog程序

sobel算子的verilog实现,采用了流水线操作 module sobel_computer ( clock , reset, OrigDataEn, //SobelAluEn, OrigData ...

- 四级流水线的8bit加法器

以流水线实现8bit 加法器. //date : 2013/8/23 //designer :pengxiaoen //function : module pipeline ( clock ,rese ...

随机推荐

- nat123 与微信公众号开发者测试账号配合调试

由于公司本身是做互联网 电商行业的,微信也是一个大块,近期开始花费时间在整合,总结自己的经验,看看之前的实现是否有明显的问题. 花了点钱(8块钱)充值了nat123,进行了内网穿透.之前也有使用花生壳 ...

- oracle单行函数之类型转换

oracle数据类型转换:显示转换盒隐式转换 oracle自动完成转换

- 26.单片机中利用定时器中断,在主流程while(1){}中设置每隔精确时间计量

{ CountMilliseconds++;//只负责自加,加到最大又重新从0开始 } u16 setDelay(u16 t) { ); } u8 checkDelay (u16 t)//返回非零表示 ...

- 多线程08-Callable和Future

1.简介 Callable是一个接口,与Runnable类似,包含一个必须实现的call方法,可以启动为让另一个线程来执行,执行Callable可以得到一个Future对象 该对象可以监听Callab ...

- eclipse sae上传代码

eclipse sae上传代码http://www.sinacloud.com/doc/sae/java/tools.html#eclipse 来自为知笔记(Wiz)

- Css溢出隐藏

display: -webkit-box;-webkit-line-clamp: 2; /*多少行数之后显示为省略...*/word-wrap: break-word;word-break: ...

- Python3 如何优雅地使用正则表达式(详解六)

修改字符串 我们已经介绍完如何对字符进行搜索,接下来我们讲讲正则表达式如何修改字符串. 正则表达式使用以下方法修改字符串: 方法 用途 split() 在正则表达式匹配的地方进行分割,并返回一个列表 ...

- EF学习

一.EF介绍 实体框架 Entity Framework 是ADO.NET 中的一组支持开发面向数据的软件应用程序的技术.在 EF 中的实体数据模型(EDM)由以下三种模型和具有相应文件扩展名的映射文 ...

- DOS头 IMAGE_DOS_HEADER

IMAGE_DOS_HEADER STRUCT { +0h WORD e_magic // Magic DOS signature MZ(4Dh 5Ah) DOS可执行文件标记 +2h WORD e_ ...

- 发布项目到 Linux 上运行 Core 项目

发布项目到 Linux 上运行 Core 项目 目录索引 [无私分享:ASP.NET CORE 项目实战]目录索引 简介 ASP.Net Core 给我们带来的最大的亮点就是跨平台,我在我电脑(win ...