HDLbits——Rotate100

verilog代码:

// Build a 100-bit left/right rotator, with synchronous load and left/right enable.

//A rotator shifts-in the shifted-out bit from the other end of the register,

// unlike a shifter that discards the shifted-out bit and shifts in a zero. If enabled,

// a rotator rotates the bits around and does not modify/discard them.

// 移出的一位不会丢弃而是补在空缺的位置,即就是题目中的a rotator要求

// load: Loads shift register with data[99:0] instead of rotating.

// ena[1:0]: Chooses whether and which direction to rotate.

// 2'b01 rotates right by one bit

// 2'b10 rotates left by one bit

// 2'b00 and 2'b11 do not rotate.

// q: The contents of the rotator.

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @(posedge clk)

begin

if(load)begin

q <= data;

end

else begin

case(ena)

2'b01: q <= {q[0],q[99:1]};//拼接运算符号{,} ,向右移动1bit

2'b10: q <= {q[98:0],q[99]};//向左边移动1bit

2'b00,2'b11:q <= q; // 保持

default:

q<= q; //所有情况考虑完整的情况下,此处可以省略

endcase

end

end

endmodule

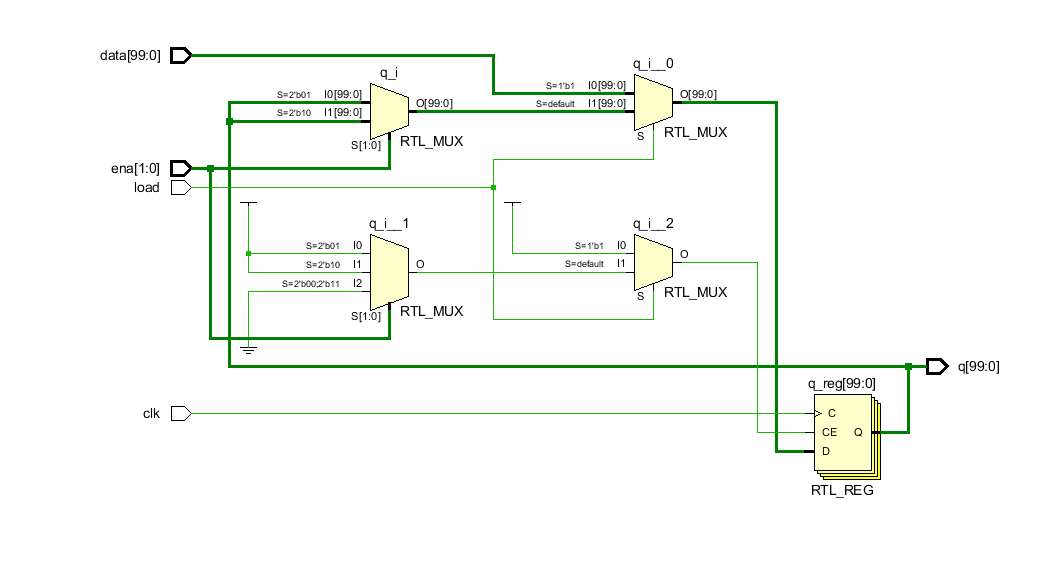

RTL原理图:

HDLbits——Rotate100的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- HDLBits答案——Circuits

1 Combinational Logic 1.1 Basic Gates 1.1.1 Exams/m2014 q4h module top_module ( input in, output out ...

- HDLBits答案——Verification: Writing Testbenches

1 clock module top_module ( ); reg clk; dut U1(.clk(clk)); initial begin clk = 0; end always begin # ...

- HDLBits答案——Verification: Reading Simulations

1 Finding bugs in code 1.1 Bugs mux2 module top_module ( input sel, input [7:0] a, input [7:0] b, ou ...

- HDLBits答案——Verilog Language

Verilog Language 1 Basics 1.1 Wire module top_module( input in, output out ); assign out = in; endmo ...

- HDLBits答案——Getting started

Getting started 1 Step one module top_module( output one ); // Insert your code here assign one = 1' ...

- verilog常见错误列表

Error/Warning 来源:https://hdlbits.01xz.net/wiki/ 题目: 1.Quartus Warning 10235: Warning (): Verilog HDL ...

- Verilog HDL

https://wenku.baidu.com/view/9943b7acf524ccbff1218463.html https://hdlbits.01xz.net/wiki/Main_Page h ...

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- 入行数字IC验证的一些建议

0x00 首先,推荐你看两本书,<"胡"说IC菜鸟工程师完美进阶>(pdf版本就行)本书介绍整个流程都有哪些岗位,充分了解IC行业的职业发展方向.<SoC设计方法 ...

随机推荐

- 第1关—print()函数与转换

Print()函数的用法有以下几种:单枪匹马--不带引号.搭配单引号.搭配双引号.搭配三引号,我们逐个见识下吧! 1.无引号 注意,这里的括号一定要用[英文括号],不然会报错 impor ...

- Mysql 索引心得

1. 频繁查询的字段,应该创建索引. 2.更新非常频繁的字段,不应该创建索引. 3.唯一性太差的字段,比如 gender字段,就不应该创建索引. 4.不会出现在where条件之后的字段,不应该创建索引 ...

- Metasploit渗透测试框架二

Metasploit基本使用方法 Metasploit基本命令 Metasploit程序需要使用Postgresql数据库. Postgresql是一种特性齐全的自由软件的对象-关系型数据库管理系统( ...

- windows 系统进行升级之后,如何删除 Windows.old 文件夹。

首先用鼠标右键点击 C 盘,在弹出的下拉列表里找到"属性"并点击它. 步骤阅读 2 在打开的 C 盘属性里的常规找到"磁盘清理",点击它打开. 步骤阅读 3 这 ...

- 实现接口开启线程(实现Runnable接口)

步骤 定义类实现Runnable接口 重写run()方法 在测试类创建子类对象 创建线程对象把子类对象作为参数传入构造方法 用线程对象调用start()方法开启线程 //1.类实现Runnable接口 ...

- MySQL下载,安装,配置环境变量【0基础小白用】

一,下载 选择社区版的,下载地址:https://dev.mysql.com/downloads/installer/ ,选择离线安装包 二,安装 1,双击安装包文件,这里选择服务模式,会安装在默认 ...

- css背景模糊化

处理背景模糊化 在css中,可以利用filter属性和blur()函数实现高斯模糊效果,filter属性用于设置图片元素的可视效果,配合blur()函数使用可给图片元素添加高斯模糊效果,语法为&quo ...

- SAP适合医疗器械行业的公司、工厂吗?

医疗器械行业在我国国民经济中发展情况良好,未来发展前景也很看好.但竞争力不强,在GMP要求下消耗大量的人力.物力是我国医疗器械企业需要面对的巨大压力,在这种情况下,企业如何充分利用网络经济和信息手段加 ...

- ptyhon基础课程_4

16 循环语句 1.while 语句的格式:"while 条件 :" while True : #循环输出"你好,世界" print ("你好,世界& ...

- GoLand 和 Pycharm的 快捷键设置与常用插件

GoLand 插件 Gopher 美化进度条,让等待更优雅. CodeGlance pro 旁边浏览框. 快捷键设置 删除行: ctrl + L 重新格式化代码 ctrl + K 开始新行 ctrl ...