SAR ADC简介

SAR型 (逐次逼近型)

摘要:逐次逼近寄存器型(SAR)模数转换器(ADC)占据着大部分的中等至高分辨率ADC市场。SAR ADC的采样速率最高可达5Msps,分辨率为8位至18位。SAR架构允许高性能、低功耗ADC采用小尺寸封装,适合对尺寸要求严格的系统。

本文说明了SAR ADC的工作原理,采用二进制搜索算法,对输入信号进行转换。本文还给出了SAR ADC的核心架构,即电容式DAC和高速比较器。最后,对SAR架构与流水线、闪速型以及Σ-Δ ADC进行了对比。

引言

逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。SAR ADC的分辨率一般为8位至16位,具有低功耗、小尺寸等特点。这些特点使该类型ADC具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。

顾名思义,SAR ADC实质上是实现一种二进制搜索算法。所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC采样速率仅是该数值的几分之一。

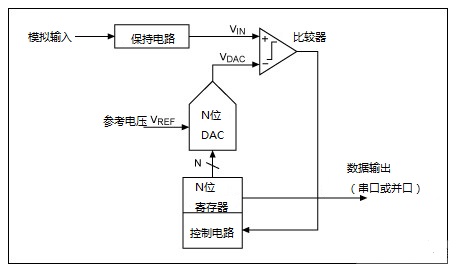

SAR ADC的架构

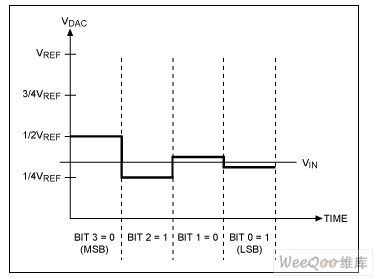

尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。模拟输入电压(VIN)由采样/保持电路保持。为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100... .00,MSB设置为1)。这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压。然后,比较判断VIN是小于还是大于VDAC。如果VIN大于VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。相反,如果VIN小于VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。这个过程一直持续到LSB。上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

SAR ADC的工作流程

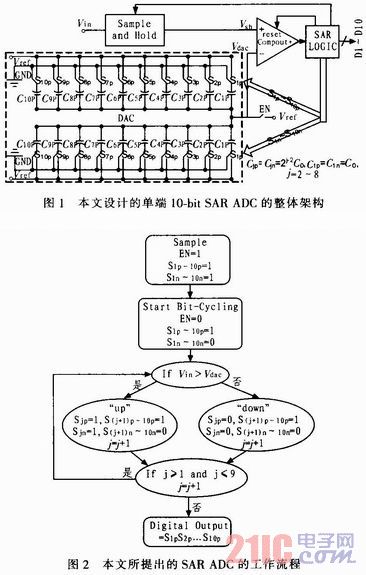

了解了SAR的架构后,我们以一个10位单端SAR ADC的整体为例,来说明SAR ADC的工作流程。该SAR ADC的架构如图1所示,主要包括以下4个部分:采样保持电路(Sample and Hold)、比较器(Comp)、10-bit逐次逼近寄存器及控制电路(SARLOGIC)、D/A转换电路(DAC)。 输入电压Vin通过采样保持电路得到采样电压Vsh,Vsh与DAC的输出Vdac通过比较器进行比较,比较结果传递给逐次逼近寄存器,逐次逼近寄存器一方面输出比较结果,另一方面控制DAC的转换开关,以便进行下一位的转换。

该SAR ADC的工作流程如图2所示,它主要可以分为采样、清零阶段和比较阶段。

第一步:采样、清零阶段。采样保持电路中的开关S,闭合,Vin=Vsh,属于跟随阶段;DAC中的电容C1p~C10p和C1n~C10n的下级板全部接GND,开关EN闭合,Vdac接GND,DAC处于清零阶段。

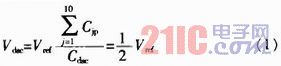

第二步:比较阶段。采样保持电路中的开关Sa断开,Vsh为采样得到的电压;DAC中的电容C1p~C10p的下级板接Vref,其余开关不动,而开关EN断开,此时DAC的输出结果:

Vsh与Vdac进行比较,如果Vsh大于Vdac,则比较器输出为1,即D1=1,而逐次逼近寄存器根据比较结果,将电容C10n(MSB电容)的下级板偏转到Vref;反之D1=0,C10p的下级板偏转到GND。其余电容保持不变。

第j步:根据上一步比较的结果,得到DAC的输出如下:

Vsh与Vdac进行比较,如果Vsh大于Vdac,则比较器输出为1,即Dj-1=1,而逐次逼近寄存器根据比较结果,将电容C(11-j)n的下级板偏转到Vref;反之Dj-1=0,C(11-j)p的下级板偏转到GND。其余电容保持不变。直至j=11,比较结束,进入下一个转换周期。

直到j>9时,结束转换,进行数字输出。

注意,对于4位ADC需要四个比较周期。通常,N位SAR ADC需要N个比较周期,在前一位转换完成之前不得进入下一次转换。由此可以看出,该类ADC能够有效降低功耗和空间,当然,也正是由于这个原因,分辨率在14位至16位,速率高于几Msps (每秒百万次采样)的逐次逼近ADC极其少见。

SAR ADC的另一个显着的特点是:功耗随采样速率而改变。这一点与闪速ADC或流水线ADC不同,后者在不同的采样速率下具有固定的功耗。这种可变功耗特性对于低功耗应用或者不需要连续采集数据的应用非常有利(例如,用于PDA 数字转换器)。

SAR的深入分析

SAR ADC的两个重要部件是比较器和DAC,稍后我们可以看到,图1中采样/保持电路可以嵌入到DAC内,不作为一个独立的电路。

SAR ADC的速度受限于:

·DAC的建立时间,在这段时间内必须稳定在整个转换器的分辨率以内(如:LSB)

·比较器,必须在规定的时间内能够分辨VIN与VDAC的微小差异

·逻辑开销

许多SAR ADC采用具有固有采样/保持功能的电容式DAC。电容式DAC根据电荷再分配的原理产生模拟输出电压,由于这种类型的DAC在SAR ADC中很常用,所以,我们最好讨论一下它们的工作原理。

电容式DAC包括一个由N个按照二进制加权排列的电容和一个“空LSB”电容组成的阵列。图3是一个16位电容式DAC与比较器相连接的范例。采样阶段,阵列的公共端(所有电容连接的公共点,见图3)接地,所有自由端连接到输入信号(模拟输入或VIN)。采样后,公共端与地断开,自由端与VIN断开,在电容阵列上有效地获得了与输入电压成比例的电荷量。然后,将所有电容的自由端接地,驱动公共端至一个负压-VIN。

作为二进制搜索算法的第一步,MSB电容的底端与地断开并连接到VREF,驱动公共端电压向正端移动½VREF。

因此,VCOMMON = -VIN + ½ × VREF

如果VCOMMON < 0 (即VIN > ½ × VREF),比较器输出为逻辑1。如果VIN < ½ × VREF,比较器输出为逻辑0。

如果比较器输出为逻辑1,MSB电容的底端保持连接至VREF。否则,MSB电容的底端连接至地。

接下来,下一个较小电容的底端连接至VREF,将新的VCOMMON电压与地电位进行比较。

继续上述过程,直至所有位的值均确定下来。

简言之,VCOMMON = -VIN + BN-1 × VREF/2 + BN-2 × VREF/4 + BN-1 × VREF/8 + ... + B0 × VREF/2N-1 (B_为比较器输出/ADC输出位)。

DAC校准:

对于一个理想的DAC来讲,每个与数据位相对应的电容应该精确到下一个较小电容的两倍。在高分辨率ADC (如16位)中,这会导致过宽的数值范围,以致无法用经济、可行的尺寸实现。16位的SAR ADC (如MAX195)实际由两列电容组成,利用电容耦合减小LSB阵列的等效容值。MSB阵列中的电容经过微调以降低误差。LSB电容的微小变化都将对16位转换结果产生明显的误差。不幸的是,仅仅依靠微调并不能达到16位的精度,或者补偿由于温度、电源电压或其它参数的变化所造成的性能指标的改变。考虑到上述原因,MAX195内部为每个MSB电容配置了一个校准DAC,这些DAC通过电容耦合到主DAC输出,根据它们的数字输入调节主DAC的输出。

校准时,首先要确定用于补偿每个MSB电容误差的修正代码,并存储该代码。此后,当主DAC对应的数据位为高电平时就把存储的代码提供给适当的校准DAC,补偿相关电容的误差。一般由用户发起校准过程,也可以在上电时进行自动校准。为降低噪声效应,每个校准过程都执行许多次(MAX195大约持续14,000个时钟周期),结果取平均值。当供电电压稳定后最好进行一次校准。高分辨率ADC应该在电源电压、温度、基准电压或时钟等任何一个参数发生显着变化后进行再校准,因为这些参数对直流偏移有影响。如果只考虑线性指标,可以容许这些参数有较大改变。因为校准数据是以数字方式存储的,无需频繁转换即可保持足够的精度。

比较器

比较器需要具有足够的速度和精度,尽管比较器的失调电压不影响整体的线性度,它将给系统传输特性曲线带来一个偏差,为减小比较器的失调电压引入了失调消除技术。然而,还必须考虑噪声,比较器的等效输入噪声通常要设计在1 LSB以内。比较器必须能够分辨出整个系统精度以内的电压,也就是说比较器需要保证与系统相当的精度。

SAR ADC与其它ADC结构的比较

与流水线ADC相比

流水线ADC采用一种并行结构,并行结构中的每一级同时进行一位或几位的逐次采样。这种固有的并行结构提高了数据的吞吐率,但要以功耗和延迟为代价。所谓延迟,在此情况下定义为ADC采样到模拟输入的时间与输出端得到量化数据的时间差。例如,一个5级流水线ADC至少存在5个时钟周期的延迟,而SAR只有1个时钟周期的延迟。需要注意的是,延迟的定义只是相对于ADC的吞吐率而言,并非指SAR的内部时钟,该时钟是吞吐率的许多倍。流水线ADC需要频繁地进行数字误差校准,以降低对流水线上每一级闪速ADC (即比较器)的精度要求。而SAR ADC的比较器精度只需与整体系统的精度相当即可。流水线ADC一般比同等级别的SAR需要更多的硅片面积。与SAR一样,精度高于12位的流水线ADC通常需要一些某种形式的微调或校准。

与闪速ADC相比

闪速ADC由大量的比较器构成,每个比较器包括一个宽带、低增益预放大器和锁存器。预放大器必须仅用于提供增益,不需要高线性度和高精度,这意味着只有比较器的门限值才需具有较高的精度。所以,闪速ADC是目前转换速率最快的一种架构。

通常需要折衷考虑闪速ADC的速度以及SAR DAC的低功耗和小尺寸特性。尽管极高速的8位闪速ADC (以及它们的折叠/内插变种)具有高达1.5Gsps的采样速率(例如MAX104、MAX106和MAX108),但很难找到10位的闪速ADC,而12位(及更高位)闪速ADC还没有商用化的产品。这是由于分辨率每提高1位,闪速ADC中比较器的个数将成倍增长,同时还要保证比较器的精度是系统精度的两倍。而在SAR ADC中,提高分辨率需要更精确的元件,但复杂度并非按指数率增长。当然,SAR ADC的速度是无法与闪速ADC相比较的。

与Σ-Δ转换器相比

传统的过采样/Σ-Δ转换器被普遍用于带宽限制在大约22kHz的数字音频应用。近来,一些宽带Σ-Δ转换器能够达到1MHz至2MHz的带宽,分辨率在12位至16位。这通常由高阶Σ-Δ调制器(例如,4阶或更高)配合一个多位ADC和多位反馈DAC构成。Σ-Δ转换器具有一个优于SAR ADC的先天优势:即不需要特别的微调或校准,即使分辨率达到16位至18位。由于该类型ADC的采样速率要比有效带宽高得多,因此也不需要在模拟输入端增加快速滚降的抗混叠滤波器。由后端数字滤波器进行处理。Σ-Δ转换器的过采样特性还可用来“平滑”模拟输入中的任何系统噪声。

Σ-Δ转换器要以速率换取分辨率。由于产生一个最终采样需要采样很多次(至少是16倍,一般会更多),这就要求Σ-Δ调制器的内部模拟电路的工作速率要比最终的数据速率快很多。数字抽取滤波器的设计也是一个挑战,并要消耗相当大的硅片面积。在不远的将来,速度最高的高分辨率Σ-Δ转换器的带宽将不大可能高出几兆赫兹很多。

总结

综上所述,SAR ADC的主要优点是低功耗、高分辨率、高精度、以及小尺寸。由于这些优势,SAR ADC常常与其它更大的功能集成在一起。SAR结构的主要局限是采样速率较低,并且其中的各个单元(如DAC和比较器),需要达到与整体系统相当的精度。

SAR ADC简介的更多相关文章

- 一种3位sar adc工作过程推导(二)

3位sar adc采用下图的电容阵列,需要23个电容,它的基本单元有二进制加权的电容阵列.1个与LSB电容等值的电容:它利用电容上的初始电荷再分配完成二进制搜索算法,因此功耗一般比较小,而且不需要额外 ...

- 一种3位sar adc仿真验证

3位sar adc采用下图的电容阵列,电路如下图:所有电容的正端(也称为上极板)与比较器的同相端连接,比较器反相端接gnd,其工作过程进行大致分析见之前的文章<一种3位sar adc工作过程推导 ...

- SAR ADC : 逐次逼近寄存器型(SAR)模数转换器(ADC)

1.为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100... .00,MSB设置为1).这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压.然后,比较判断VI ...

- ∑–△型模数转换器(ADC)简介

∑–△型模数转换器(ADC) 1.概述 近年来,随着超大规模集成电路制造水平的提高,Σ-Δ型模数转换器正以其分辨率高.线性度好.成本低等特点得到越来越广泛的应用.Σ-Δ型模数转换器方案早在20世纪60 ...

- STM32 逐次逼近寄存器型(SAR)模拟数字转换器(ADC)

是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构. SAR ADC的分辨率一般为8位至16位,具有低功耗.小尺寸等特点. 这些特点使该类型ADC具有很宽的应用范围,例如便携/ ...

- 探索ADC的原理(自制3位并行比较型ADC)

摘要 本文通过列举历史中出现的产品,梳理了模数转换器在20世纪30年代~~20世纪80年代末的发展历史.接下来,简要介绍模数转换器的原理.技术指标.分类和未来发展方向.最后,提供了一种自制3位FLAS ...

- 理解逐次逼近寄存器型ADC:与其它类型ADC的架构对比【转】

转自:http://bbs.dzsc.com/space/viewspacepost.aspx?postid=86760 摘要:逐次逼近寄存器型(SAR)模数转换器(ADC)占据着大部分的中等至高分辨 ...

- 基于STM8的ADC读取---STM8-第四章

1. 综诉 想学会如何在STM8上使用ADC这个功能,我们先得了解单片机中ADC究竟是什么. ADC是模拟信号转成数值信号,单片机只能识别TTL电平,其实就是 1 或者 0 ,但是如果我们给它一个3. ...

- linux下sar tool command note

linux下的sar工具简介 我习惯使用的命令是 : sar -r -f /var/log/sa/sa24 sar 既能报告当前数据,也能报告历史数据 不带选项执行会以10分钟为间隔报告自午夜 ...

随机推荐

- js 获取浏览器版本号

1.在web开发中,会常常让你推断当前使用的是那个浏览器及浏览器的那个版本号,依据浏览器版本号来调整CSS的样式, 使在web界面在各个浏览器展现达到最佳的效果,以下是获取当前浏览器的代码: getB ...

- string的操作

除了顺序容器共有的操作之外,string类型还提供了一些额外的操作.这些操作中的大部分要么是提供string类和C风格字符数组之间的相互转换,要么是增加了允许我们用下标代替迭代器的版本. 构造stri ...

- linux mysql 卸载后重装

$sudo apt-get remove mysql-common清理残留数据:$sudo dpkg -l |grep ^rc|awk '{print $2}' |sudo xargs dpkg -P ...

- Using Sessions and Session Persistence---reference

Using Sessions and Session Persistence The following sections describe how to set up and use session ...

- linux服务器上

命令行>mysql -uwin -pwin2009进入mysql command状态>use mindo时入mindo数据库>source 500sql.txt执行sql

- update 改写 merge into

update语句改写成merge into有时会提高运行速度 看两个案例 1.根据业务将两个嵌套子查询改写成max,速度有3min提升到3s UPDATE OPER_792.LL_SCB_YDKB_2 ...

- Adapter 适配器模式

将一个类的接口转换成客户希望的另外一个接口.Adapter模式使得原本由于接口不兼容而不能一起工作的那些类可以在一起工作. 目标接口(Target):客户所期待的接口.目标可以是具体的或抽象的类,也可 ...

- html代码实现自动滚动,鼠标滑过时停止滚动

<marquee style="width: 1200px;height:200px;margin:0px auto" onmouseout="this.start ...

- jQuery 定时局部刷新(setInterval)方法总结

来自:http://www.jbxue.com/article/8516.html 1.jQuery 定时局部刷新(setInterval),显示时间的代码. <head> <scr ...

- Bootstrap--组件之按钮组

什么是按钮组呢?简单解释:就是把一堆的按钮放在一行或者一列中.下面来看一个实例. 按钮组嘛,首先是按钮,所以会用到.btn这个类,还有就是bootstrap提供的按钮组.btn-group这个类,所以 ...