Verilog语言:还真的是人格分裂的语言

人气腹语术师天愿在现场披露了被人偶搭档夺取灵魂的腹语术师将妻子杀害的表演节目。天愿真的陷入了多重人格,命令自己杀害妻子和子的人偶的人格出现了。为了不(让自己)杀害和弟子登川有外遇的妻子,天愿提出委托想要监视,然而第二天早上,和子真的被杀害的事件发生了。天愿坦白很可能是在自己的意识失去的时候杀害的……”(----“真相只有一个”《名侦探柯南》一向是老衲喜欢的动画片)这个是第806回《腹语師的错觉》的介绍。

人有双重人格,或者叫人格分裂,那么语言呢?Verilog语言还真的是人格分裂的语言。前回书已经说到了,不能简单地把wire类型映射为组合逻辑,同时把reg类型映射为时序逻辑。事实上,这两个概念会交叉的。也就是说,wire类型极可能被综合为组合逻辑也可能综合为时序逻辑,reg类型也是这样。

“‘reg’是什么?”最微软的回答是:注册表文件。这个自然没错,但是违背了“到哪座山,唱哪里歌”的原则。一般的“标准”答案是:寄存器型变量。看看‘reg’,不就是‘register’(寄存器)的缩写吗?大多数中文教材中都是这样说的。

下面为了说明白这桩事情,请允许老僧引用IEEE有关Verilog语言里面的原文:

“Assignments to a reg are made by procedural assignments (see 6.2 and 9.2). Since the reg holds a value between assignments, it can be used to model hardware registers. Edge-sensitive (i.e., flip-flops) and level sensitive (i.e., RS and transparent latches) storage elements can be modeled. A reg need not represent a hardware storage element since it can also be used to represent combinatorial logic.”

为了强调,表1里面给出了wire、reg类型和组合逻辑、时序逻辑之间的映射关系。

表1 wire、reg类型和组合逻辑、时序逻辑之间的映射关系

|

wire |

reg |

|

|

组合逻辑 |

可 |

可 |

|

时序逻辑 |

可 |

可 |

可见reg是“双面间谍”的工作性质,为了能够“左右逢源”,自然用法要比wire来的复杂。类型wire被综合为时序逻辑一般还真是写错了,不必细表。

1. 电平触发,组合实现

和reg“孟不离焦,焦不离孟”的是关键词always,这个要记清楚。人家wire和assign是夫妻,reg和always是一对,千万不要搞混了,这不是能拉郎配的季节。

“always”的语法结构是:

always @(sensitive_tabel)

其中,sensitive_tabel称作敏感列表,其中包含always内部操作的一个或者多个触发条件。字符“@”发音是“艾特”(at),大伙儿发电子邮件(e-mail)的时候常用,不罗嗦。

正如上面提到的、标准立面的说法可以是边沿敏感和电平敏感两种。对于组合逻辑电路,这个敏感列表里面所有条件均为电平敏感。逻辑上,当敏感列表里面的条件符合的时候,always内部的操作可以进行。但是,很多逻辑上可行的代码,由于没有实际电路的支持,是无法实现的。

在Verilog语言95版本里面,电平触发的敏感列表的写法是

triger1 or triger2 or triger3……

其中,triger1等为触发信号。当触发信号电平变化时,说明敏感列表里面条件符合。如果触发信号是向量,则其中一个比特的信号变化,就认为信号电平有变化。到了Verilog 2001版本,这个写法被更加简化了:“,”和“or”都可以用来分割敏感事件;并且,可以用“*”代表所有输入信号,这可以防止遗漏。例1给出了一些符合语法的always的例子。

【例1】always与敏感列表

always @ (triger1 or triger2 or triger3) //Version 95 and Version 2001

always @ (triger1 , triger2 , triger3) //Version 2001

always @ (*) //Version 2001

具有完全电平敏感列表的always模块,总叫人觉得就是组合逻辑了。再次强调数字电路是并行工作的,注意不要用“执行”这个词,不准确。对应的所有assign以及always带领的快都是并行的,其在代码中前后顺序与输出结果无关。也就是说例2里面的两段代码是等效的。代码中,敏感列表sensitive_table1和sensitive_table2对应操作Operation_A和操作Operation_B。

【例2】always所带操作顺序与输出结果无关

|

always @(sensitive_table1) Operation_A always @( sensitive_table2) Operation_B |

always @( sensitive_table2) Operation_B always @(sensitive_table1) Operation_A |

理论上,assign后面只有一行,对于这个并行工作的理解不难,不会产生误解。到了always这里,一般其后的代码就有很多行了,一不注意就会出错。

2. 条件判断,分枝多多

“用C语言的标准评价Verilog,如同用水果的标准评价蜜饯。”,但是他们的确很多写法有类似,这是很容易误导学习者的地方。

前文书关于“? :”选择操作哪里介绍过,选择与分枝在一般系统中是不可少的。那里介绍的代码方法,显然会产生阅读困难----尤其是在条件比较多的时候。为了改善这一问题,也同时可以更加符合大家以前的习惯,这一讲书老朽给贵客介绍“if”和“case”这两位大家熟悉的陌生人。

先看眼里的代码,条件语句if的形式有如表2中的三种。其中,condition等表示选择的条件,operation等表示对应的操作。请注意,这里的表达式“选择”,目的是和电路对应,不是故意和别人不一样的哗众取宠。

表2条件语句if的格式

|

无分枝 |

单级分枝 |

多级分枝 |

|

|

形式 |

if (condition ) begin operations end |

if (condition ) begin operations_1 end else begin operations_2 end |

if (condition_1 ) begin operations_1 end else if (condition_2 ) begin operations_2 end else if…… …… begin operations_m end |

|

对应电路 |

时序电路 |

时序电路 组合电路 |

时序电路 组合电路 |

表.2中“对应电路”一行也请施主们注意,if语句中条件的所有路径覆盖不全面,可能会产生时序电路的。对于reg类型的变量,需要满足“条件不满足的时候,保持原值”;同时,组合电路不可“自赋值”(也就是类似“a <= a”的形式)。当需要“保持”的时候,纯组合电路是无法满足的。所以,综合器会引入“锁存器”。不是综合器自作主张,这是代码的要求。“天作孽犹可恕,自作孽不可活”,只能怪你自己了,哭吧!这个对应的器件是锁存器,不是这里的重点,会在以后介绍。这里要说的是:要产生组合逻辑,if的条件路径必须全覆盖。

if语句中条件的所有路径覆盖不全面,可能会产生时序电路的。这个对应的器件是锁存器,不是这里的重点,以后介绍。这里要说的是:要产生组合逻辑,if的条件路径必须全覆盖。

例3是一个单级条件语句if应用的例子,其功能是求有符号数绝对值。其中,输入为8比特有符号数,编码方式为补码;输出是输入数值的绝对值。具体算法是:

【例3】绝对值运算模块

module abs

(

input[7:0] signed_value,

output reg[6:0] result

);

//Definition for Variables in the module

//Load other module(s)

//Logical

always @(signed_value)

begin

if ( signed_value[7])

//Negative number input

begin

result <= (~signed_value[6:0]) + 7'h01;

end

else

//Positive number or zero input

begin

result <= signed_value[6:0];

end

end

endmodule

3. 多种情况,并列判决

在条件很多的时候,用if语句来写还是很麻烦的,搞不好就是是一个条件路径覆盖不完全。这个时候,可以选择case套餐。case语句是一种多分支选择语句, Verilog语言提供的case语句直接处理多分支选择。多分支的case有三种形式,如表3所示。

表3条件语句case的形式

|

case |

casex |

casez |

|

|

比较方式 |

敏感表达式与各项值之间的比较,是一种全等比较 |

如果分支表达式某些位的值为高阻z,那么对这些位的比较就会忽略,不予考虑,而只关注其他位的比较结果。 casez会把z/?匹配成任意,也会把任意匹配成z/? |

在casex语句中,则把这种处理方式进一步扩展到对x的处理,即如果比较双方有一方的某些位的值是z或x,那么这些位的比较就不予考虑。 casex会把z/?x匹配成任意,也会把任意匹配成z/?/x,即直接忽略z/?/x |

|

形式 |

case (variable) costant_1: begin operations_1 end costant_2: begin operations_2 end …… default: begin operations_m end endcase |

case (variable) costant_1: begin operations_1 end costant_2: begin operations_2 end …… default: begin operations_m end endcase |

case (variable) costant_1: begin operations_1 end costant_2: begin operations_2 end …… default: begin operations_m end endcase |

|

constant项 |

各个constant项为确定宽度的常数值,不包含x和z; 可以用“?”表示不关心该位数值 |

各个constant项为确定宽度的常数值,可包含x但不能包含z |

各个constant项为确定宽度的常数值,可包含z但不能包含z |

|

constant例子 |

3’b000:3比特宽度全0; 3’b0?0:3比特宽度第二比特不关心,其他比特为0 |

3’b000:3比特宽度全0; 3’b0?0:3比特宽度第二比特不关心,其他比特为0; 3’b00x:3比特宽度最低比特为x,其他比特为0 |

3’b000:3比特宽度全0; 3’b0?0:3比特宽度第二比特不关心,其他比特为0; 3’b00z:3比特宽度最低比特为不关心,其他比特为0 |

|

可综合性 |

可综合 |

依赖综合软件 |

依赖综合软件 |

case括弧内的变量称为控制表达式,case分支项中的常数称为分支表达式。控制表达式通常表示为控制信号的某些位,分支表达式则用这些控制信号的具体状态值来表示,因此分支表达式又可以称为常量表达式。当控制表达式的值与分支表达式的值相等时,就执行分支表达式后面的语句。如果所有的分支表达式的值都没有与控制表达式的值相匹配的,就执行default后面的语句。

default项可有可无,一个case语句里只能有一个default项。 当分支表达式可以覆盖控制表达式全部分枝路径时,default可以不写。但是,有时候这个全覆盖不是那么容易看出来的,所以建议最好写上default,哪怕有冗余这个default永远不可能被实现。也请大家放心,这种冗余综合软件会大伙儿去掉的,不必担心浪费电路资源。

每一个case分项的分支表达式的值必须互不相同,否则就会出现矛盾现象(对表达式的同一个值,有多种执行方案)。

执行完case分项后的语句,则跳出该case语句结构,终止case语句的执行。(精通C语言的大虾们请特别注意这点,这里case操作执行完之后不必写break了。)

在用case语句表达式进行比较的过程中,只有当信号的对应位的值能明确进行比较时,比较才能成功,因此要详细说明case分项的分支表达式的值。

case语句的所有表达式的值的位宽必须相等,只有这样控制表达式和分支表达式才能进行对应位的比较。一个经常犯的错误是用'bx、'bz 来替代n'bx、n'bz,这样写是不对的,因为信号x、z的缺省宽度是机器的字节宽度,通常是32位(此处 n 是case控制表达式的位宽)。

当分支表达式不完全覆盖控制表达式全部分枝路径时,您老有偷懒没有写default的情况下,可能产生时序逻辑的锁存器的,这点和条件if语句类似。例4是一个例子,说明了default的重要性。但是,图1中的“ld”是锁存器已经是时序电路的元件了,超越了本章的范围。

【例4】case语句条件覆盖不全产生会综合出锁存器

代码1:组合逻辑电路写法

module case_full

(

input[7:0] number,

input[1:0] select,

output reg[7:0] result

);

//Load other module(s)

//Definition for Variables in the module

//Logical

always @(*)

begin

case (select)

2'b00:

begin

result <= number + 8'b0000_0001;

end

2'b01:

begin

result <= number;

end

2'b10:

begin

result <= number - 8'b0000_0001;

end

default:

begin

result <= 8'b0000_0000;

end

endcase

end

endmodule

图1例4综合出的电路图(全部为组合逻辑)

4. 多路选择,一个例子

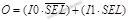

数据选择器(也称为:多路复用器,英文:multiplexer,简写:MUX),是一种从多路输入信号中选择一个信号作为输出的器件。电器符号如图2所示。

图2数据选择器的电气符号

数据选择器的的逻辑功能是:

注意,其中输入I0、I1和SEL以及输出O都是1比特位宽的信号。对应布尔逻辑表达式是

对应Verilog代码为:

1) 利用? :表达式

input SEL;

input I0;

input I1;

output O

assign O =(SEL) ? (I0) : (I1);

代码中关键的部分是? :表达式,其语法结构为 (逻辑表达式) ? (值0) : (值1);作用是

所以,以上代码满足了数字电路里面数据选择器的功能。

2) 利用if关键词

If (SEL == 1’b0)

begin

O = I0;

end

else

begin

O = I1;

end

3) 利用case关键词

case (SEL)

1’b0:

begin

O = I0;

end

1’b1:

begin

O = I1;

end

endcase

在很多情况下,需要选择的输入位宽大于1,这个时候只要两个待选择的输入与输出的位宽一致,照样可以实现功能(以下按照8比特输入为例)。此时Verilog代码除了模块的接口位宽,其他部分几乎没有变化:

input SEL;

input[7:0] I0;

input[7:0] I1;

output[7:0] O

assign O =(SEL) ? (I0) : (I1);

当然用if或者case语句也可以实现,相信读者举一反三的能力,就不罗列了。

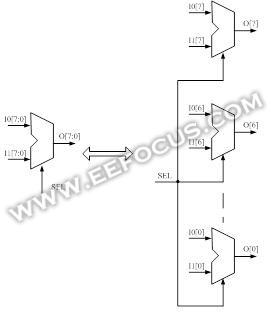

很多读者或许会感觉到笔者十分啰嗦,实则不然,图3是多位输入的数据选择器的电气原理图。

图3 多位数据选择器的电路原理图

上图看起来是顺理成章的。这里之所以笔者还不厌其烦的画出来,是为了叫读者看到多位与1比特实现上的区别。如果眼睛还没有贵恙的话,可以看出来多位数据选择器就是若干1比特数据选择器的并行排列。考虑到前面内容介绍的时延问题,需要提醒读者注意的是这个位数很高(当然不是例子里面的8比特)的时候,输入和输出信号的skew(线间时延)可能会给设计带来麻烦。

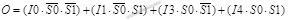

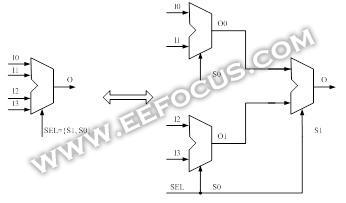

另一种常见的情况是输入不止有两个信号,或者说需要在不仅仅两个信号里面进行选择,这个叫做高阶数据选择器(一般吧SEL的比特数称为数据选择器的阶数)。通常输入个数是2的幂,此时选择信号SEL也就不仅是1比特信号了,这个很容易理解。在理论上,可以通过展开布尔逻辑表达式的方法,完成高速的高阶数据选择器。例如,2阶(也就是有4个输入信号,SEL为2比特变量)的随机选择的布尔逻辑表达式为:

其中,I0、I1、I2和I3为器件的输入,S0和S1为SEL信号的低比特和高比特。

这个式子已经不简单了,如果是10阶神马的数据选择器,那样的式子的长度不难想象。所以,在工程上,一般利用低阶数据选择器的串联来实现高阶数据选择器。图4是一个用3个1阶数据选择器实现2阶数据选择器的例子。

图4 利用低阶数据选择器实现高阶数据选择器

对于高阶数据选择器的Verilog代码,一般建议利用case的形式。例如图3里面的2阶数据选择器可以用以下代码实现:

case (SEL)

2’b00:

begin

O = I0;

end

2’b01:

begin

O = I1;

end

2’b01:

begin

O = I2;

end

2’b11:

begin

O = I3;

end

endcase

这正是:

“

组合逻辑大融合,关键语法有心得。不论理论数学河,电路优化靠综合。

鄙人说书自有乐,撬行老僧沙弥哥。报告整理嫉妒惹,大乘渡人笑呵呵。

”

与非网原创内容,谢绝转载!

系列汇总:

享受快时代的精品慢阅读

十年一觉,博士毕业后十多年从事无线通讯产品的研发工作。了解W-CDMA、TDS-CDMA和LTE的标准协议、接收机算法以及系统架构和开发。从事过关于W-CDMA的FPGA IP core设计工作,也完成过W-CDMA和TDS-CDMA的接收机理论研究和链路仿真工作。综合上面的工作,最终选择了无线通讯的系统设计和标准设计工作。目前拥有100多个已授权的发明专利,是某通讯行业标准文件的第一作者,亦有专利思想被写入3GPP协议。已出版著作《IP核芯志》。

转载自:http://www.eefocus.com/fpga/365722/r0

Verilog语言:还真的是人格分裂的语言的更多相关文章

- 「C语言」Windows+EclipseCDT下的C语言开发环境准备

之前写过一篇 「C语言」在Windows平台搭建C语言开发环境的多种方式 ,讨论了如何在Windows下用DEV C++.EclipseCDT.VisualStudio.Sublime Test.Cl ...

- c语言学习笔记(1)——c语言的特点

一.c语言概述 1.为什么学习c语言? (1)c的起源和发展 第一代语言:机器语言 1101 第二代语言:汇编语言 add ax,bx; 第三代语言:高级语言 a+b; 结构化:c fortra ...

- D、GO、Rust 谁会在未来取代 C?为什么?——Go语言的定位非常好,Rust语言非常优秀,D语言也不错

不要管我的地位和 D 语言创造者之一的身份.我会坦诚的回答这个问题.我熟悉 Go 和 Rust,并且知道 D 的缺点在哪里.我鼓励人们在 Rust 和 Go 社区相似身份的人,也可以提出他们诚恳的观点 ...

- C语言的本质(15)——C语言的函数接口入门

C语言的本质(15)--C语言的函数接口 函数的调用者和其实现者之间存在一个协议,在调用函数之前,调用者要为实现者提供某些条件,在函数返回时,实现者完成调用者需要的功能. 函数接口通过函数名,参数和返 ...

- C语言的本质(7)——C语言运算符大全

C语言的本质(7)--C语言运算符大全 C语言的结合方向 C语言中各运算符的结合性分为两种,即左结合性(自左至右)和右结合性(自右至左).例如算术运算符的结合性是自左至右,即先左后右.如有表达式 x- ...

- R语言︱H2o深度学习的一些R语言实践——H2o包

每每以为攀得众山小,可.每每又切实来到起点,大牛们,缓缓脚步来俺笔记葩分享一下吧,please~ --------------------------- R语言H2o包的几个应用案例 笔者寄语:受启发 ...

- GO语言的进阶之路-初探GO语言

GO语言的进阶之路-初探GO语言 作者:尹正杰 版权声明:原创作品,谢绝转载!否则将追究法律责任. 一.为什么我们需要一门新语言 Go语言官方自称,之所以开发Go 语言,是因为“近10年来开发程序之难 ...

- 【golang】 go语言之环境搭建+ 第一个go语言程序

1 下载:http://www.golangtc.com/download (以win为例) 2 安装步骤: 安装包: go1.8.windows-amd64.msi 双击进行安装 创建工作目录 :D ...

- GO语言学习(十六)Go 语言结构体

Go 语言结构体 Go 语言中数组可以存储同一类型的数据,但在结构体中我们可以为不同项定义不同的数据类型. 结构体是由一系列具有相同类型或不同类型的数据构成的数据集合. 结构体表示一项记录,比如保存图 ...

随机推荐

- Oracle Form删除list项

Oracle From中的list项点击后就会新增一个下拉列,此时可以使用 Ctrl+shift+< 进行删除

- windows 配置环境变量快捷方式

在 Windows 设置环境变量 在环境变量中添加软件A的目录: 在命令提示框中(cmd) : 输入 path %path%;C:\A, 按下"Enter". 注意: C:\A是软 ...

- ajax常用请求方式

1.JAVA @RequestMapping(value = "testAjax") @ResponseBody public Map<String, Object> ...

- 【好】strong-password-checker,我自己做出来的:)

我自己做出来的,分了几种情况来考虑.(再后面有加了注释的版本) https://leetcode.com/problems/strong-password-checker/ // 加油! public ...

- 二八定律全面分析SEO全过程

首先,大体的了解SEO的整个流程,SEO的整个流程无非是:关键词选定.标题标签描述的正确描写---内部优化----外链----内容---友情链接---更新. 在SEO界流行这样一句话:“内容为王,外链 ...

- KL变换和PCA的数学推导

一些推导的笔记 上面分解成无穷维,大多数时候都不是的吧... 这里的d有限维,应该是指相对小于上面的分解的维度的某个数 参考资料 参考资料,上面是从最小化损失的角度,利用拉格朗日对偶的优化方法求解 p ...

- AndroidStudio刚開始学习的人

看到谷歌宣布Android Studio将代替Eclipse. 自从7月25日開始我就開始学习使用AS,由于看到谷歌公司公布的说为了简化Android的开发力度,Google决定将重点建设Androi ...

- dubbo-monitor安装监控中心,管理控制台安装网页一直访问不到,解决bug的方式记录

问题再现 第一步,重启机器 第二步,按照dubbo-monitor需要开启的服务,顺序逐一进行启动,之前的推翻全部重新再走一遍就通了,千万不能死磕...很浪费时间.... 通过打印日志追踪问题的所在. ...

- iOS_Objective-C測试

1. iOS中程序正常载入UIViewControlle时,下面四个方法哪个最先运行? A.viewVillAppear B.viewDidLoad C.viewDidAppear D.viewWil ...

- GObject对象系统

http://www.ibm.com/developerworks/cn/linux/l-gobject/ 简单的说,GObject对象系统是一个建立在GLIB基础上的,用C语言完成的,具有跨平台特色 ...