对比 Verilog 和 SystemVerilog 中的基本数据类型

作为引子,首先来看一段描述,该段介绍了SystemVerilog对比Verilog在RTL设计和建模时的新特性之一(logic数据类型),然后下文我再展开对比介绍Verilog和SystemVerilog中的基本数据类型。(该段内容引用自 @Dr. Pong P. Chu 的书籍列表之《FPGA Prototyping by SystemVerilog Examples: Xilinx MicroBlaze MCS SoC》的书籍说明部分)

《SystemVerilog vs Verilog in RTL Design》By Pong P. Chu, Chapter 3.1 logic DATA TYPE

Verilog‐2001 divides the data types into a "net" group and a "variable" group. The former is used in the output of a continuous assignment and the

wiretype is the most commonly used type in the group. The latter is used in the output of a procedural assignment and theregtype is the most commonly used type in the group. Verilog‐2001 has a specific set of rules and restrictions regarding the assignment and connection of signals from the different groups.The names of the

wireandregtypes are misleading. A signal declared with thewiretype can be a connection wire or a component with memory (e.g., a latch). A variable declared with theregtype may or may not infer a register. It can be a connecting wire, a register, a latch, or a "C‐like software variable". Furthermore, the rules and restrictions imposed on assignment and connection of signals from different the groups are confusing and unnecessary.SystemVerilog introduces the

logicdata type. It can be used in the variable group or net group, which is inferred automatically from context. Thelogictype can replace thewireandregtypes in most codes. In addition, its name does not imply a specific hardware component and thus is more descriptive.

1. Verilog的数据类型

Verilog语言提供两组基本的数据类型:变量数据类型(variable)和线网数据类型(net),这两种类型都是四值逻辑。具体请参考《IEEE Standard for Verilog》Chapter 4 Data types。

- 对线网的声明进行简化,即:

net_type list_of_net_identifiers,其中net_type包含我们常用的如wire、tri、wand、wor等等(参考完整的线网声明:net_declaration); - 对变量的声明进行简化,即:

reg | integer | time | real | realtime+list_of_variable_identifiers(参考完整的变量声明:variable_declaration)。

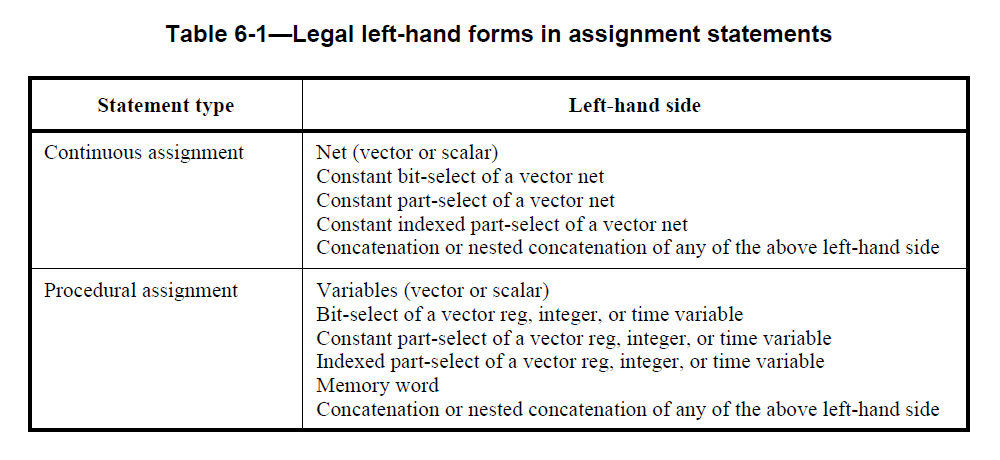

可以看到,在Verilog中,线网及变量的声明都很简单,都只有两部分:如net_type | reg | integer + 声明列表即可。另外,再来看Verilog中的赋值,Verilog中将连续赋值(Continuous assignment)及过程赋值(Procedural assignment)中的左值(LHS)分别限制为了线网(net)和变量(variable)类型,换言之,如我们常用的wire类型(net)只可以被连续赋值,以及我们常用的reg类型(variable)只可以被过程赋值:

在Verilog中,reg经常用来表示存储组合逻辑或时序逻辑的变量,不过很多初学者会混淆其综合后的硬件单元。实际上,reg变量并不一定会被综合为寄存器(register),之所以定义成reg类型,是表示从仿真的语义上来讲需要一个存储单元,而与综合后的硬件电路没有直接的关联,所以对初学者而言有时会具有误导性。而在SystemVerilog中,我们便引入了更具有描述性的logic数据类型,下面来介绍SystemVerilog中的数据类型。

2. SystemVerilog的数据类型

SystemVerilog添加了很多新的数据类型,但依然可以分为两组类型:变量类型(variable)和线网类型(net),来看他们的声明及定义如下,具体请参考《IEEE Standard for SystemVerilog》Chapter 6 Data types。

- 对线网类型的声明进行简化,即(参考完整的线网声明:net_declaration):

net_type data_type list_of_net_decl_assignments;

- 对变量类型的声明进行简化,即(参考完整的变量声明:variable_declaration):

[const][var] data_type list_of_variable_decl_assignments;

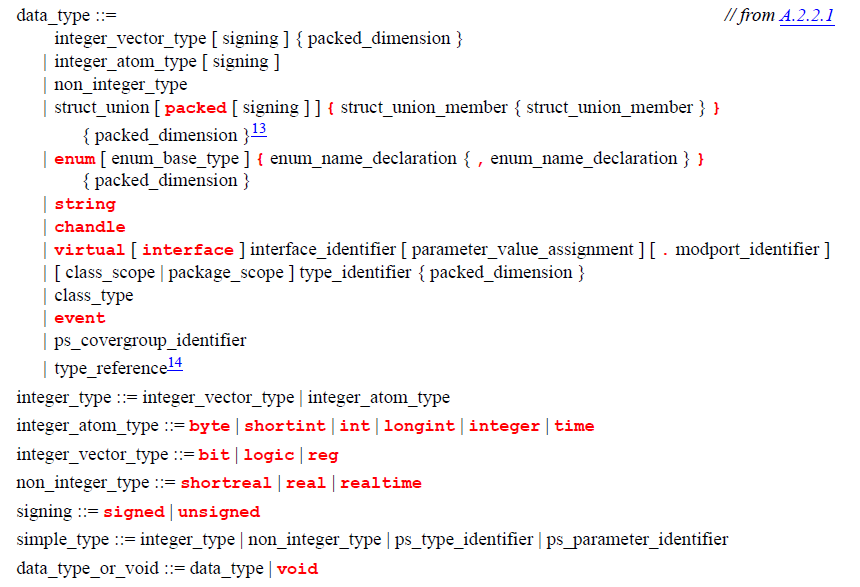

对比上述简化版之后,就可以发现:SystemVerilog区分为类型和数据类型,且两种类型(net和variable)的变量声明方式相同,都是:类型 + 数据类型 + 声明列表。其中线网类型(net_type)包含supply0 | supply1 | tri | triand | trior | trireg | tri0 | tri1 | uwire | wire | wand | wor,与Verilog相同;而变量类型(variable_type)只需要关键字var即可,并且var可以省略。而Verilog中的reg、integer、time、real、realtime在SystemVerilog中则都是指数据类型,并且SystemVerilog添加了很多新的数据类型:

其中又可以分为二值逻辑、四值逻辑;新增了枚举(enum)、结构体(struct)、字符串(string)、类(class)等一些新的数据类型,这里不展开介绍。只要明白,仅有数据类型时(如reg r;、byte b;、logic c;),其默认表示的是变量类型,因为关键字var可以省略。另外,数据类型也可以省略,仅有类型声明时(如wire w;、var v;),此时数据类型被隐式声明为logic:

- If a data type is not specified in the net declaration or if only a range and/or signing is specified, then the data type of the net is implicitly declared as

logic. - If a data type is not specified in the variable declaration or if only a range and/or signing is specified, then the data type of the variable is implicitly declared as

logic.

reg r ; // equivalent to "var reg r;"

logic [15:0] l ; // equivalent to "var logic [15:0] l;"

var byte my_byte; // equivalent to "byte my_byte;"

wire w ; // equivalent to "wire logic w;"

wire [15:0] ww ; // equivalent to "wire logic [15:0] ww;"

var v ; // equivalent to "var logic v;"

var [15:0] vw ; // equivalent to "var logic [15:0] vw;"

再来看到,像reg、bit、byte、int等,在SystemVerilog中,都属于数据类型(data_type),那么既然线网类型的声明也是net_type + data_type,则有如tri reg t;、inout wire reg p;、wire int i;等等,又是否合法呢?显然是不合法的。在《IEEE Standard for SystemVerilog》Chapter 6.7.1 Net declarations with built-in net types 中对线网类型(net_type)的数据类型(data_type)做了限制(Certain restrictions apply to the data type of a net):

- A valid data type for a net shall be one of the following:

- A 4-state integral type, including a packed array or packed structure.

- A fixed-size unpacked array or unpacked structure, where each element has a valid data type for a net.

- A lexical restriction applies to the use of the reg keyword in a net or port declaration. A net type keyword shall not be followed directly by the reg keyword. The reg keyword can be used in a net or port declaration if there are lexical elements between the net type keyword and the reg keyword.

这说明了线网类型(net_type)的数据类型(data_type)只能为四值数据类型(4-state data type),并且net_type reg list_of_net_decl;是非法的。以下都是合法的线网类型声明(net declarations):

wire logic w;

wire [15:0] ww;

trireg (large) logic #(0,0,0) cap1;

typedef logic [31:0] addressT;

wire addressT w1;

wire struct packed { logic ecc; logic [7:0] data; } memsig;

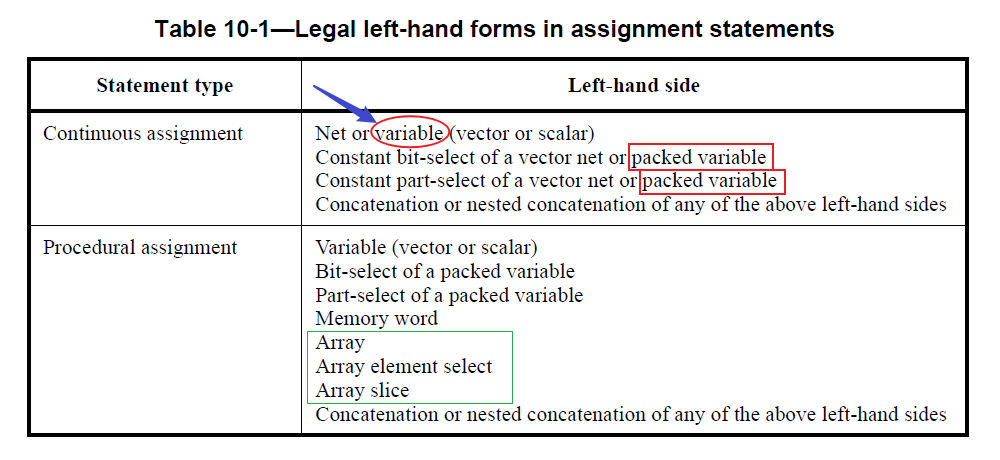

最后再来看赋值,主要注意其连续赋值(Continuous assignment)中的左值(LHS)与Verilog的区别:在SystemVerilog中,连续赋值的左值支持变量类型,而Verilog仅仅支持线网类型。

所以,如logic [15:0] data;,虽然默认表示的是变量类型(等价于var logic [15:0] data;),但是也支持连续赋值。由于其既支持连续赋值,又支持过程赋值,同时又是四值逻辑,所以logic数据类型可以代替Verilog设计代码中的大多数wire类型和reg类型,至于被综合成什么硬件,依然要由综合器根据上下文来进行推断。

对比 Verilog 和 SystemVerilog 中的基本数据类型的更多相关文章

- 第三章:systemverilog文本值和数据类型

1.增强的文本值 2.改进的`define文本替换 3.时间值 4.新的变量类型 5.有符号和无符号类型 6.静态和动态变量(***) 7.类型转换 8.常数 增强的文本值(文本赋值增强) 主要是:位 ...

- systemverilog中module与program的区别

我们知道,verilog语法标准中是没有program的,program是systemverilog语法标准新增的内容. 那么,为什么要新增一个program呢?主要考量是基于电路的竞争与冒险. 为避 ...

- Verilog与SystemVerilog编程陷阱:怎样避免101个常犯的编码错误

这篇是计算机类的优质预售推荐>>>><Verilog与SystemVerilog编程陷阱:怎样避免101个常犯的编码错误> 编辑推荐 纠错式学习,从"陷阱 ...

- SystemVerilog 中的相等运算符:== or === ?

1. 四值逻辑的逻辑运算 在对比SystemVerilog中的相等运算符之前,先来看一下三种最基本的逻辑运算符,下文中以·表示与运算,以+表示或运算,以'表示非运算.我们都知道在逻辑代数中,只有0和1 ...

- 【原创】SystemVerilog中的typedef前置声明方式

SystemVerilog中,为了是代码简洁.易记,允许用户根据个人需要使用typedef自定义数据类型名,常用的使用方法可参见"define和typedef区别".但是在Syst ...

- PowerShell中的基础数据类型

PowerShell是一个面向对象的语言,在申明变量的时候不强制要求申明数据类型,使用$开头来申明变量即可. 基本数据类型 PowerShell本身是基于.Net开发出来的,所以在.Net中的基本数据 ...

- MySql中的字符数据类型

MySql中的varchar类型 1.varchar类型的变化 MySQL数据库的varchar类型在4.1以下的版本中的最大长度限制为255,其数据范围可以是0~255或1~255根据不同版本数据库 ...

- [.net 面向对象编程基础] (3) 基础中的基础——数据类型

[.net 面向对象编程基础] (3) 基础中的基础——数据类型 关于数据类型,这是基础中的基础. 基础..基础..基础.基本功必须要扎实. 首先,从使用电脑开始,再到编程,电脑要存储数据,就要按类型 ...

- Mssql中一些常用数据类型的说明和区别

Mssql中一些常用数据类型的说明和区别 1.bigint 占用8个字节的存储空间,取值范围在-2^63 (-9,223,372,036,854,775,808) 到 2^63-1 (9,223,37 ...

随机推荐

- 用 set follow-fork-mode child即可。这是一个 gdb 命令,其目的是告诉 gdb 在目标应用调用fork之后接着调试子进程而不是父进程,因为在 Linux 中fork系统调用成功会返回两次,一次在父进程,一次在子进程

GDB的那些奇淫技巧 evilpan 收录于 Security 2020-09-13 约 5433 字 预计阅读 11 分钟 709 次阅读 gdb也用了好几年了,虽然称不上骨灰级玩家,但 ...

- linux patch中的p0和p1的区别

命令patch的主要作用是生成diff文件和应用diff文件.举个例子来讲,当发现某个程序出现bug需要打补丁时,patch便是一个好工具. diff文件头: [root@localhost kern ...

- linux服务之FTP服务篇

一.FTP协议 FTP服务器(File Transfer Protocol Server)是在互联网上提供文件存储和访问服务的计算机,它们依照FTP协议提供服务. FTP (File Transfer ...

- shell基础之多功能nginx(安装、重启、停止等)

1 #!/bin/bash 2 #要求:检查本机是否已编译安装nginx,检查本机是否存在nginx源码包,编译安装nginx,实现开启.停止.查看状态等功能 3 #检查是否已编译安装nginx 4 ...

- IDEA 配置 Tomcat(详细)(Day_12)

如果这世界上真有奇迹,那只是努力的另一个名字.生命中最难的阶段,不是没有人懂你,而是你不懂你自己. 运行环境 AND 版本 JDK8 + IntelliJ IDEA 2018.3 + Tomca ...

- mysql数据库-简介

目录 1 MySQL 的三大主要分支 1.1 官方文档 1.2 版本演变 1.3 MySQL 安装方式 1.3.1 RPM包安装Mysql 1.3.2 二进制安装MySQL 1.4 mysql组成 1 ...

- 『动善时』JMeter基础 — 30、JMeter中JSON断言详解

目录 1.JSON断言组件界面详解 2.JSON断言组件的使用 (1)测试计划内包含的元件 (2)登陆接口请求界面内容 (3)JSON断言界面内容 (4)查看运行结果 (5)断言结果组件说明 3.JS ...

- 微信小程序从开发到上线流程

一.微信小程序从开发到上线流程 注册小程序 1.登录微信公众平台 https://mp.weixin.qq.com 2.在微信公众平台>立即注册>小程序中注册微信小程序 3.在邮箱中激活并 ...

- 使用 Bridge to Kubernetes 简化云端开发

当我们面对一个大型应用程序,它有大量的微服务,并希望完成一些功能开发? 我们面临许多挑战,其中之一将是处理正确的环境,如何进行开发.我们知道,在团队中解决这个问题的最佳方法是将其容器化并在云上托管.这 ...

- GO语言异常处理02---返回错误

package main import ( "errors" "fmt" "math" ) /*计算圆面积,同时返回[结果-错误对]*/ f ...