【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验

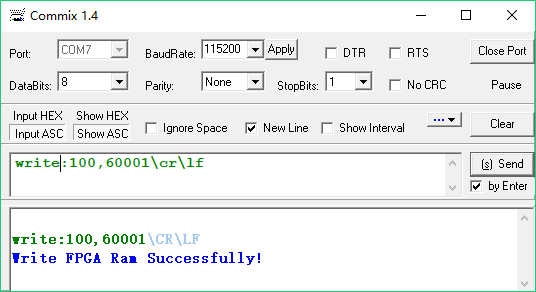

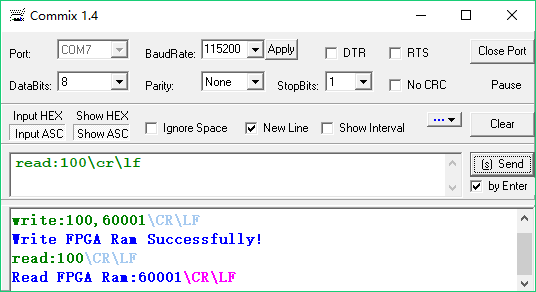

实验现象:

写RAM命令格式:write:地址(0-255),数据(0-65535)\cr\lf

读RAM命令格式:read:地址(0-255)\cr\lf

核心代码:

int main(void)

{ /* USER CODE BEGIN 1 */

int i;

int address,data;

char error_flag = ;

char receive_data[];

char buffer[];

char *p;

/* USER CODE END 1 */ /* MCU Configuration----------------------------------------------------------*/ /* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init(); /* USER CODE BEGIN Init */ /* USER CODE END Init */ /* Configure the system clock */

SystemClock_Config(); /* USER CODE BEGIN SysInit */ /* USER CODE END SysInit */ /* Initialize all configured peripherals */

MX_GPIO_Init();

MX_USART6_UART_Init();

MX_FMC_Init(); /* USER CODE BEGIN 2 */

usart6.initialize();

usart6.printf("Hello, I am iCore4!\r\n"); /* USER CODE END 2 */ /* Infinite loop */

/* USER CODE BEGIN WHILE */

while ()

{

/* USER CODE END WHILE */ /* USER CODE BEGIN 3 */

if(usart6.receive_ok_flag == ){

usart6.receive_ok_flag = ;

memset(receive_data,,sizeof(receive_data));

memset(buffer,,sizeof(buffer));

for(i = ;i < ;i ++){

receive_data[i] = usart6.receive_buffer[i];

}

p = receive_data;

i = ;

while(*p != ':'){ //»ñÈ¡²Ù×÷ÃüÁwrite or read£©

buffer[i++] = *p++;

if(i > sizeof(buffer))i = ;

}

for(i = ;i < sizeof(buffer);i++){//½«ÃüÁîת»¯ÎªÐ¡Ð´×Ö·û

buffer[i] = tolower(buffer[i]);

}

if(memcmp(buffer,"write",strlen("write")) == ){//Ö´ÐÐд²Ù×÷

error_flag = ;

p++;

address = atoi(p);

if(address > )error_flag = ;

p++;

p = strchr(p,',');

if(p == NULL)error_flag = ;

if(!error_flag){

p++;

data = atoi(p);

if(data > )error_flag = ; if(!error_flag){

fpga_write(address,data);

usart6.printf("Write FPGA Ram Successfully!");

}

}

}else{

if(memcmp(buffer,"read",strlen("read")) == ){//Ö´ÐжÁ²Ù×÷

error_flag = ;

p++;

address = atoi(p);

if(address > )error_flag = ;

p++;

if(strchr(p,','))error_flag = ;

if(!error_flag){

data = fpga_read(address);

usart6.printf("Read FPGA Ram:%d\r\n",data);

}

}else{

error_flag = ;

}

}

if(error_flag){

LED_RED_ON;

LED_GREEN_OFF;

usart6.printf("Bad Command!\r\n");

}else{

LED_RED_OFF;

LED_GREEN_ON;

}

}

}

/* USER CODE END 3 */ }

module ram_ctrl(

input clk_100m,

input rst_n,

input wr_n,

input rd_n,

input cs0,

input [:]ab,

inout [:]db,

output led_red,

output led_green,

output led_blue

);

//----------------------------clk------------------------------//

wire wr,rd;

wire [:]data_out; assign wr = wr_n | cs0;

assign rd = rd_n | cs0; reg wr_0,wr_1;

always@(posedge clk_100m or negedge rst_n)

if(!rst_n)

begin

wr_0 <= 'd1;

wr_1 <= 'd1;

end

else

{wr_1,wr_0} <= {wr_0,wr}; wire clk = !wr_1 | !rd;

assign db = !rd ? data_out:'hzzzz; //----------------------------ram------------------------------//

ram u1(

.clock(clk),

.wren(!wr),

.rden(!rd),

.address(ab),

.data(db),

.q(data_out)

); //----------------------------led_ctrl-------------------------//

reg led;

always@(posedge clk or negedge rst_n)

if(!rst_n)

led <= 'd1;

else

led <= ~led; assign {led_red,led_green,led_blue} = {'d1,led,1'd1}; endmodule

源代码下载链接:

链接:http://pan.baidu.com/s/1pKZTJAj 密码:pkf7

iCore4链接:

【iCore4 双核心板_FPGA】例程十五:基于单口RAM的ARM+FPGA数据存取实验的更多相关文章

- 【iCore1S 双核心板_FPGA】例程十二:基于单口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module single_port_ram( input CLK_12M, input WR, input RD, input CS0, inout [:]DB, input ...

- 【iCore3 双核心板_FPGA】实验十八:基于单口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1i58Ssvz iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- 【iCore4 双核心板_FPGA】例程十六:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: int main(void) { /* USER CODE BEGIN 1 */ int i; int address,data; ; ]; ]; char *p; /* US ...

- 【iCore3 双核心板_FPGA】实验十九:基于双口RAM的ARM+FPGA数据存取实验

实验指导书及代码包下载: http://pan.baidu.com/s/1pLReIc7 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore3 双核心板】例程十五:USB_CDC实验——高速数据传输

实验指导书及代码包下载: http://pan.baidu.com/s/1gemYjz9 iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 【iCore4 双核心板_FPGA】例程十:FSMC总线通信实验——复用地址模式

实验原理: STM32F767上自带FMC控制器,本实验将通过FMC总线的地址复用模式实现STM32与FPGA 之间通信,FPGA内部建立RAM块,FPGA桥接STM32和RAM块,本实验通过FSMC ...

- 【iCore4 双核心板_FPGA】例程十四:基于I2C的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,通过串口精灵给ARM发送数据从而给FPGA发送数据 ,会接收到字符GINGKO. 3.通过串口精灵发送命令可以控制ARM·L ...

- 【iCore4 双核心板_FPGA】例程十一:FSMC总线通信实验——独立地址模式

实验原理: STM32F767上自带FMC控制器,本实验将通过FMC总线的地址独立模式实现STM32与FPGA 之间通信,FPGA内部建立RAM块,FPGA桥接STM32和RAM块,本实验通过FSMC ...

随机推荐

- Angular 个人深究(三)【由Input&Output引起的】

Angular 个人深究(三)[由Input&Output引起的] 注:最近项目在做别的事情,angular学习停滞了 1.Angular 中 @Input与@Output的使用 //test ...

- C++雾中风景番外篇3:GDB与Valgrind ,调试代码内存的工具

写 C++的同学想必有太多和内存打交道的血泪经验了,常常被 C++的内存问题搅的焦头烂额.(写 core 的经验了)有很多同学一见到 core 就两眼一抹黑,不知所措了.笔者 入"坑&quo ...

- 使用tortoisegit简化命令

1. 如果希望git保存用户名和密码,后续操作都无需输入密码: git命令: git config --global credential.helper store 或者通过tortoisegit ...

- 50 tips of JavaScript,这些坑你都知道吗?

1.在局部作用域中,使用var操作符定义的变量将成为定义该变量的作用域中的局部变量,省略var的会创建全局变量:在全局作用域中,不管是否使用var操作符定义的变量都会创建一个全局变量.但是,在全局作用 ...

- 洛谷.2219.[HAOI2007]修筑绿化带(单调队列)

题目链接 洛谷 COGS.24 对于大的矩阵可以枚举:对于小的矩阵,需要在满足条件的区域求一个矩形和的最小值 预处理S2[i][j]表示以(i,j)为右下角的C\(*\)D的矩阵和, 然后对于求矩形区 ...

- python图片和分形树

链接: 这10个Python项目很有趣! Python 绘制分形图(曼德勃罗集.分形树叶.科赫曲线.分形龙.谢尔宾斯基三角等)附代码 使用Python生成树形图案 神奇的代码:用 Python 生成分 ...

- iOS离屏渲染之优化分析

在进行iOS的应用开发过程中,有时候会出现卡顿的问题,虽然iOS设备的性能越来越高,但是卡顿的问题还是有可能会出现,而离屏渲染是造成卡顿的原因之一.因此,本文主要分析一下离屏渲染产生的原因及避免的方法 ...

- Delphi 开发ActiveX控件(非ActiveForm)

Delphi 开发ActiveX控件(非ActiveForm) Q:为什么不采用ActiveForm工程?通过它可以快速开发带窗体控件,创建过程也非常简单(都不用考虑安全接口问题),很省事! A:如果 ...

- OpenCV支持向量机(SVM)介绍

支持向量机(SVM)介绍 目标 本文档尝试解答如下问题: 如何使用OpenCV函数 CvSVM::train 训练一个SVM分类器, 以及用 CvSVM::predict 测试训练结果. 什么是支持向 ...

- Linux网络编程:socket文件传输范例

基于TCP流协议的socket网络文件传输Demo: 实现:C语言功能:文件传输(可以传任何格式的文件) /********************************************** ...