Verilog中的UDP

概述

Verilog HDL语言提供了一种扩展基元的方法,允许用户自己定义元件(User Defined Primitives,UDP)。通过UDP,可以把一块组合逻辑电路或者时序逻辑电路封装在一个UDP内,并把这个UDP作为一个基本的元件来使用。需要注意的是,UDP不能综合,只能用于仿真。

UDP的定义与调用

UDP定义的语法和模块定义类似,但由于UDP和模块同属于同级设计,因此,UDP定义不能出现在模块之内。UDP定义使用由关键词primitive和endprimitive封装起来的一段代码,这段代码定义了该UDP的功能。这种功能的定义是通过表来实现的,即在这段代码中有一段处于 关键词table和endtable之间的表,用户可以通过设置该表来规定UDP的功能。

UDP的定义格式如下:

primitive<元件名称>(<输出端口名>,<输入端口名1>,输入端口名1>...输入端口名n>);

输出端口类型声明(output);

输入端口类型声明(input);

输出端口寄存器 变量说明(reg);

元件初始状态说明(initial);

table

<table 表项1>;

<table 表项2>;

......

<table 表项n>;

endtable

endprimitive

与Verilog HDL中的模块相比,UDP具有以下特点:

(1)UDP的输出端口只能有一个,且必须位于端口列表的第一项。只有输出端口能定义为REG类型。

(2)UDP的输入端口可有多个,一般时序电路UDP的输入端口最多9个,组合电路UDP的输入端口可多至10个。

(3)所有端口变量的位宽必须是1比特。

(4)在table表项中,只能出现0,1,x这三种状态,z将被认为是x状态。

根据UDP包含的基本逻辑功能,可以将UDP分为组合电路UDP、时序电路UDP及混合电路UDP,这几类UDP的差别主要体现在table表项的描述上。

UDP的调用和verilog HDL中模块的调用方法相似,通过位置映射。其语法格式如下:

UDP名 例化名(连接端口1信号名,连接端口2信号名,连接端口3信号名,...);

UDP定义的全加器

组合逻辑电路的功能列表类似真值表,规定了不同的输入值和对应的输出值,表中每一行的形式是"output ,input1,input2...",排列顺序与端口列表中的顺序相同。组合电路UDP的输入端口可多至10个。如果某个输入,输出组合没有定义输出,那么就把这种情况的输出置位x。

3选1多路选择器

?代表不必关心相应变量的具体值。

UDP原语中可以使用的值

UDP还可以描述具有电平触发和边沿触发特性的时序电路。时序电路拥有内部状态序列,其内部状态必须用寄存器变量进行建模,该寄存器的值就是时序电路的的当前状态,它的下一个状态是由放在基本功能列表中的状态转换表决定的,而且寄存器的下一个状态就是这个时序电路UDP的输出值。所以时序电路UDP由两部分组成——状态寄存器和状态列表,定义时序电路UDP的工作也分为两部分——初始化状态寄存器和描述状态列表。

在时序电路的UDP描述中,01、0x、x1代表着信号的上升沿。

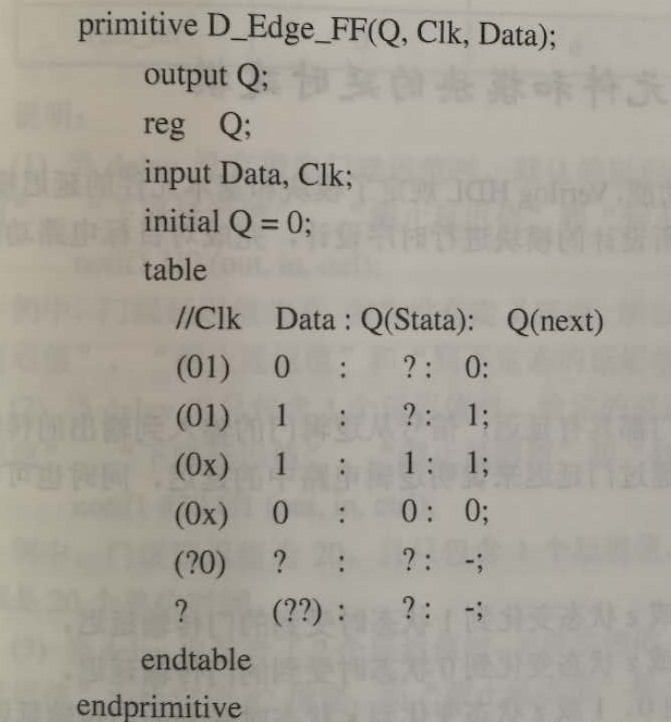

通过verilog hdl语言给出D触发器的UDP描述

表项(01)表示从0转换到1,表项(0x)表示从0转换到x,表项(?0)表示从任意值转换到0,表项(??)表示任意转换。对于未定义的转换,输出默认为x,假定D_Edge_FF为UDP定义,则它现在就能够像基本门一样在模块中使用。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

Verilog中的UDP的更多相关文章

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- LabVIEW中的UDP通信

UDP(user datagram protoco1)提供向接收端发送信息的最简便的协议,与TCP不同,UDP不是面向连接的可靠数据流传输协议,而是面向操作的不可靠数据流传输协议.UDP在数据传输之前 ...

- 关于verilog中if与case语句不完整产生锁存器的问题 分类: FPGA 2014-11-08 17:39 260人阅读 评论(0) 收藏

在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因. 一,什么是锁存器?锁存器与触发器 ...

- 关于Verilog 中的for语句的探讨

在C语言中,经常用到for循环语句,但在硬件描述语言中for语句的使用较C语言等软件描述语言有较大的区别. 在Verilog中除了在Testbench(仿真测试激励)中使用for循环语句外,在Test ...

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- verilog中always块延时总结

在上一篇博文中 verilog中连续性赋值中的延时中对assign的延时做了讨论,现在对always块中的延时做一个讨论. 观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 . @2时刻, ...

- verilog中读取文件中的字符串_modelsim高级仿真

今天给个程序大家玩玩.因为今天遇到一个问题,就是要向UART发送指令,指令非常多,都是字符串.一直copy 函数 UART ("COMM_1"); UART ("COM ...

随机推荐

- JNIjw04

1.VC6(CPP)的DLL代码: #include<stdio.h> #include "jniZ_JNIjw04.h" #include <string> ...

- DOM元素的位置、尺寸及更多的信息

一.基本概念 document.documentElement是整个DOM树的根节点,对应的元素就是html.下面将其称作根元素或根节点. document.body,对应的元素是body 二.浏览器 ...

- EditText实现输入限制和校验

EditText实现输入限制和校验 一.方法 1)输入限制 1.通过android:digits限制只能输入小写abc android:digits="abc" 2.通过andro ...

- spring3: AOP 之切面实例化模型 ——跟我学spring3

所谓切面实例化模型指何时实例化切面. Spring AOP支持AspectJ的singleton.perthis.pertarget实例化模型(目前不支持percflow.percflowbelow ...

- yii2:oracle date类型字段的写入或查询

insert: insert into tabname(datecol) value(sysdate) ; -- 用date值 insert into tabname(datecol) value(s ...

- LeetCode OJ :Remove Linked List Elements (移除链表元素)

Remove all elements from a linked list of integers that have value val. ExampleGiven: 1 --> 2 --& ...

- opencv 卡尔曼滤波器例子,自己修改过

一.卡尔曼滤波器的理论解释 http://blog.csdn.net/lindazhou2005/article/details/1534234(推荐) 二.代码中一些随机数设置函数,在opencv中 ...

- 在javascript中使用提示信息来熟悉当前的程序流程

最近,因为需要,开始了解javascript,这个对我来说是个新的东西,在分析现有程序的功能的时候,需要增加一些提示信息来帮助了解程序的处理流程.于是在网上了解了一下提示信息的使用和区别.在此整理一下 ...

- HihoCoder1325 : 平衡树·Treap(附STL版本)

平衡树·Treap 时间限制:10000ms 单点时限:1000ms 内存限制:256MB 描述 小Ho:小Hi,我发现我们以前讲过的两个数据结构特别相似. 小Hi:你说的是哪两个啊? 小Ho:就是二 ...

- AngularJS方法 —— angular.bootstrap

描述: 此方法用于手动加载angularjs模板 (官方翻译:注意基于端到端的测试不能使用此功能来引导手动加载,他们必须使用ngapp. angularjs会检测这个模板是否被浏览器加载或者加载多次并 ...