FPGA最小系统分析与电路设计

《FPGA最小系统分析与电路设计》

部分节选自《FPGA应用开发入门与典型.pdf 》

FPGA最小系统包括:FPGA芯片、下载电路、外部时钟、复位电路和电源。

如果使用NIOS II软嵌入式处理器还要包括SDRAM和Flash。

)配置管脚

MSEL[1..0]:用于选择配置模式,FPGA有多种配置模式,如主动、被动、

快速、正常、串行、并行等,以此管脚进行选择;

DATA0:FPGA串行数据输入,连接置配置芯片的串行数据输出管脚;

DCLK:FPGA串行时钟输出,为配置器件提供串行时钟;

nCSO(I/O):FPGA片选信号输出,连接至配置器件的nCS管脚;

ASDO(I/O):FPGA串行数据输出,连接至配置器件的ASDI管脚;

nCEO:下载链器件使能输出,在一条下载链种,当一个器件配置完成后,

此信号使能下一个器件开始进行配置。下载链的最后一个器件的nCEO应

悬空。

nCE:下载链器件使能输入,连接至上一个器件的nCEO,下载链的第一个

器件的nCE接地。

nCONFIG:用户配置模式起始信号;

nSTATUS:配置状态信号;

CONF_DONE:配置结束信号。

)电源引脚

VCCINT:内核电压,与工艺有关,例如130nm工艺为1.5V,90nm工艺为1.2V;

VCCIO:端口电压,一般为3.3V,也可以选择为5V、1.8V、1.5V;

VREF:参考电压;

GND:信号地。

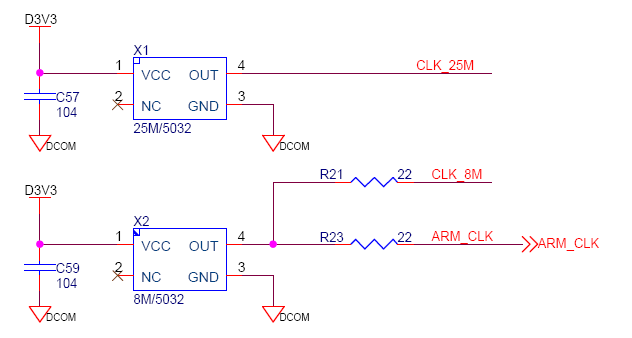

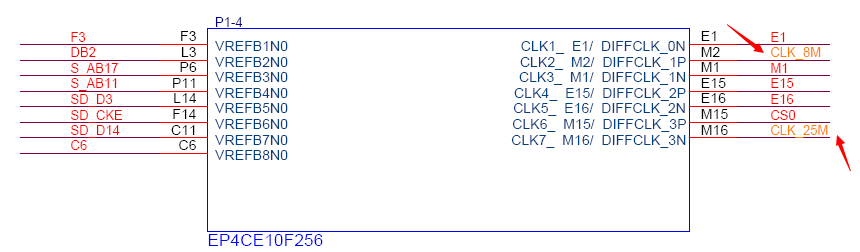

)时钟管脚

VCC_PLL:锁相环管脚电压,直接连VCCIO。

VCCA_PLL:锁相环模拟电压,一般通过滤波器连到VCCINT上。

GNDA_PLL:锁相环模拟地。

GNDD_PLL:锁相环数字地。

CLKnum(LVDSCLKnump):锁相环时钟输入,支持LVDS时钟输入,p接正端,num

表示PLL序号。

CLKnum(LVDSCLKnumn):锁相环时钟输入,支持LVDS时钟输入,n接负端,num

表示PLL序号。

PLLnum_OUTp(I/O):锁相环时钟输出,支持LVDS时钟输入,p接正端,num

表示PLL序号。

PLLnum_OUTn(I/O):锁相环时钟输出,支持LVDS时钟输入,n接正端,num

表示PLL序号。

)JTAG模式与AS模式

FPGA是SRAM型结构,本身不能固话程序。因此FPGA需要一片Flash结构的配置

芯片来存储逻辑配置信息,用于上电配置。

以Altera公司的FPGA为例,配置芯片分为串行(EPCSx系列)和并行(EPCx系列)

其中EPCx为老款配置芯片,体积大,价格高,现在常用EPCSx系列芯片。

JTAG模式是直接将程序下载到FPGA芯片上运行,可以无限擦写,AS模式是将程序

下载到编程配置芯片上,然后再配置FPGA。

)高速SDRAM

SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓

冲区。SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片

都是兼容的。

常用的有HY57V系列、三星K4S系列和美光MT48LC系列。

)电源设计:

AMS11117可以提供1A电流,线性电源(适用于144管脚以下、5万逻辑门以

下的FPGA)。

AS2830(或LT1085/6)可以提供3A电流,线性电源(适用于240管脚以下,

30万逻辑门以下的FPGA)。

TPS54350可以提供3A电流,开关电源(适用于大封装大规模的高端FPGA)。

)硬件调试方法

(1)先焊接电源部分,使用万用表测试,排除电源短路等情况后,上电测

试电压是否正确。

(2)然后焊接FPGA及其相关的下载电路,排除引脚粘连,再次测了电源地

之间是否有短路现象,上电测试电压是否正确,然后将手排除静电后触摸

FPGA有无发烫现象。如果出现FPGA发烫现象,一般是出现总线冲突的现象。

这种情况下需要检查外围总线是否出现竞争问题,通常是多片存储器片选

信号同时选通造成。

(3)以上步骤通过后,连接JTAG,上电运行,打开Quartus II,并打开

Programmer,点击Auto DEtect看能否检测到FPGA。

(4)焊接时钟电路、复位电路,并向FPGA下载一个程序,检查是否正常工作。

普及下 来自网友COM张 http://group.chinaaet.com/116/5263

刚学FPGA,谁能给俺解释一下SDRAM ,SRAM ,FLASH在FPGA中起的作用?最好能详细点~谢谢啦

在FPGA开发板上除了内部onchip memory,都有几种不同的存储器,比如SDRAM,SRAM,FLASH,EPCS。

1.EPCS

FPGA只是一个装载软核配置信息的一个工具,它是基于SRAM的查找表,上电的时候需要重新配置,因此一定需要一个配置芯片。一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS系列串行FLASH。一般使用AS模式下载EPCS系列器件。但有时候可能遇到AS模式不能成功下载的案例,原理图以及PCB板都是按照推荐电路设计,这时候我们可以通过Flash Loader检验EPCS器件是否良好。即通过JTAG方式下载EPCS系列器件。如果这种方式还是不能进行正确的AS模式的下载的话,可能EPCS器件本身已经不能正常工作了,此时可以建议更换配置芯片了。

在AS模式下,由目标FPGA来主动输出控制和同步信号(包括配置始终)给Altera专用的串行配置芯片EPCS*。

2.FLASH

属于EEPROM(电擦除可编程只读存储器),一种不挥发性(Non-Volatile )内存,在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。

在FPGA开发板中一般用来存储应用程序(C程序等)。用户可以将程序或用户数据烧写入Flash,可以通过NiosII IDE中提供的工具“Flash Programmer”来实现,非常方便,当然也可以自己写代码来将数据烧写入Flash。

3.SDRAM

SDRAM是多Bank结构,例如在一个具有两个Bank的SDRAM的模组中,其中一个Bank在进行预充电期间,另一个Bank却马上可以被读取,这样当进行一次读取后,又马上去读取已经预充电Bank的数据时,就无需等待而是可以直接读取了。这也就大大提高了存储器的访问速度。为了实现这个功能,SDRAM需要增加对多个Bank的管理,实现控制其中的Bank进行预充电。在一个具有两个以上Bank的SDRAM中,一般会多一根叫做BAn的引脚,用来实现在多个Bank之间的选择。在FPGA开发板中一般作为NIOS 处理器的RAM和程序运行空间。

4.SRAM

一个SRAM中的位单元通常由4~6只晶体管组成,利用双稳态触发器来保存信息,当这个位单元被赋予0或1的状态之后,它会保持这个状态直到下次被赋予新的状态,或者断电之后才会更改或消失。SRAM的速度相对比较快,而且比较省电,但是存储1位的信息需要4~6只晶体管,制造成本较高。

SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积。

FPGA最小系统分析与电路设计的更多相关文章

- FPGA最小系统设计

以EP4CE6E22I7为例,设计FPGA最小系统. 程序存储设计 一般使用EPCS4I8N: FPGA_DATA0:13 FPGA_DCLK :12 FPGA_nCS:8 ASDO:6 时钟 待续

- 系统分析与设计个人作业:WordCount

本次作业gitee地址:https://gitee.com/ackary/WordCount 一.项目简介 1.基础功能 基础功能部分主要实现的功能是统计一个程序设计语言源文件的字符数.单词数.行数, ...

- SATA主机协议的FPGA实现之物理层设计

SATA主机协议的FPGA实现之物理层设计 接上一篇文章,这里讲解SATA主机协议的物理层的实现过程. 下图是标准SATA协议文档中给出的物理层结构.可以看到它包含控制模块.时钟数据提取单元.同步 ...

- 文献综述十六:基于UML的中小型超市管理系统分析与设计

一.基本信息 标题:基于UML的中小型超市管理系统分析与设计 时间:2016 出版源:Journal of Xiangnan University 文件分类:uml技术系统的研究 二.研究背景 开发一 ...

- 基于FPGA的HDMI显示设计(三)

上一篇:基于FPGA的VGA显示设计(二) 10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”. 实习要求用 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- RQNOJ 622 最小重量机器设计问题:dp

题目链接:https://www.rqnoj.cn/problem/622 题意: 一个机器由n个部件组成,每一种部件都可以从m个不同的供应商处购得. w[i][j]是从供应商j处购得的部件i的重量, ...

- 干货分享,FPGA硬件系统的设计技巧

PGA的硬件设计不同于DSP和ARM系统,比较灵活和自由.只要设计好专用管脚的电路,通用I/O的连接可以自己定义.因此,FPGA的电路设计中会有一些特殊的技巧可以参考. 1. FPGA管脚兼容性设计 ...

- 系统分析与设计lesson6

| 分类 作业 | 1.用例建模 a. 阅读 Asg_RH 文档,绘制用例图. 按 Task1 要求,请使用工具 UMLet,截图格式务必是 png 并控制尺寸 b. 选择你熟悉的定旅馆在线服务系统 ...

随机推荐

- C# 取整

double a = 1.1478; Math.Celling(a): 向上取整,结果为2 Math.Float(a); 向下取整,结果为1 Math.Round(a,2); 保留两位小数的奇进偶舍 ...

- 如何使用数据库保存session的方法简介

使用数据库保存session的方法 php的session默认是以文件方式保存在服务器端,并且在客户端使用cookie保存变量,这就会出现一个问题,当一个用户由于某种安全原因关闭了浏览器的cookie ...

- HTML&CSS布局练习---360导航页面

一共分为7个部分:由HTML和CSS外部样式表做成 <!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" ...

- Office and Windows KMS使用帮助

Office KMS Key: http://technet.microsoft.com/zh-cn/library/dn385360.aspx htt ...

- 初学者对Spring MVC的认识

首先是要一定说明的是,这倒是说明是什么?对吧Spring MVC 是SpringFrameWork的后续产品,并且已经融入到Spring Web Flow中同时Spring MVC 分离了控制器,模型 ...

- C#中String.Empty,“”,NULL的区别

一.String.Empty String类的静态只读字段.定义如下: public static readonly string Empty; 二.“” 被赋值为“”的字符串变量,会在栈上保存一个地 ...

- UVALive 7297 bfs

题意 一个小偷偷到了项链 他想知道自己是否可以逃出去 地图中有一个小偷 一个警察 警察有一条狗 一开始 小偷和警察的移动速度都是1 当警察走到小偷经过过的地方时 警察会有一条狗嗅到小偷的气味并且以2的 ...

- Codeforces Round #360 (Div. 2) C D E

每次AB秒出 到了C难度陡然上升...翻译都弄不懂... C 给出一张图 找出两个点的覆盖集(覆盖集是指这图中每条边都有至少一个点在这个点集里面) 并且两个点集没有交集 英文很难看懂...就是二分图的 ...

- 使用java代码,动态给TextView设置drawable

Drawable country = context.getResources().getDrawable(drawableId); country.setBounds(0, 0, country.g ...

- Tiffany

--名称:Tiffany&Co(蒂芙尼) --总部:美国,纽约 --历史:1837年创立 --产品:珠宝.手表. 配饰.礼品 --特点:品牌,质量,奢饰品