SystemVerilog Tutorial

1.网站说明-tutorial

This SystemVerilog tutorial is written to help engineers with background in Verilog/VHDL to get jump start in SystemVerilog design and Verification. In case you find any mistake, please do let me know. I always love to hear about mistakes in my website.

As such this tutorial assumes that, you are already familiar with Verilog and bit of C/C++ language. If you are not well versed with verilog, you can refer to verilog section or go through the Verilog basics tutorial below.

Currently this website is getting more than 3 million hits every month.

总结就是网站帮助具有Verilog或VHDL背景的人员快速学习使用SystemVerilog来设计和验证.假想读者已经熟悉Verilog或者C/C++,否则可以先看看Verilog基础部分——verilog basic

2.SystemVerilog

Verilog 1995 version has been in market for a very long time. IEEE extended the features of Verilog 1995 and released it as Verilog 2001. But this was no good for verification engineers, so verifcation engineers had to use languages like "e", VERA, Testbuider. It was rather painfull to have two language, one for design and other for verification. SystemVerilog combines the Verification capabilties of HVL (Hardware Verification Language) with ease of Verilog to provide a single platform for both design and verification.

==Anyone with background of C++, or OO programming language will feel at home with SystemVerilog. But on other hand if you have been thinking C or C++ is not required, then you may be shocked to know that SystemVerilog is very much like C++. ==

*Now IEEE has accepted the SystemVerilog, and it is called 1800-2005 standard. *

Some of the new features in SystemVerilog are as listed below.

- C type data types like int, typedef, struct, union, enum.

- Dynamic data types : struct, classes, dynamic queues, dynamic arrays.

- New operators and built in methods.

- Enhanced flow control like, foreach, return, break, continue.

- Semaphores, mailboxes, event extensions.

- classes for object oriented programming.面向对象编程

- Assertions.断言

- Coverage.覆盖

- VPI extensions.

2.1Verilog Basic

- 主要回顾verilog最基础的部分,为SV入门必备

Verilog介绍

- Every new learner's dream is to understand Verilog in one day, at least enough to use it. The next few pages are my attempt to make this dream a reality. There will be some theory and examples followed by some exercises. This tutorial will not teach you how to program; it is designed for those with some programming experience. Even though Verilog executes different code blocks concurrently as opposed to the sequential execution of most programming languages, there are still many parallels. Some background in digital design is also helpful.不同于大多数编程语言,verilog语言中有许多并行执行的语句,有数字设计背景将有助于学习理解

- Life before Verilog was a life full of schematics. Every design, regardless of complexity, was designed through schematics. They were difficult to verify and error-prone, resulting in long, tedious development cycles of design, verification... design, verification... design, verification... Verilog语言出现之前,设计中多是原理图设计,对验证和错误检测带来了很大困难,从而导致开发周期很长

When Verilog arrived, we suddenly had a different way of thinking about logic circuits. The Verilog design cycle is more like a traditional programming one, and it is what this tutorial will walk you through. **Here's how it goes: **

- Specifications (specs) 协议

- High level design 高层次设计

- Low level (micro) design 低层次设计

- RTL coding RTL代码

- Verification 验证

- Synthesis. 综合

2.2Specifications

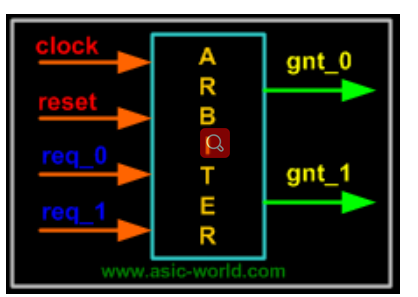

For this tutorial, we'll be building a two agent arbiter: a device that selects among two agents competing for mastership. Here are some specs we might write up.

- Two agent arbiter.

- Active high asynchronous reset. 高电平异步复位

- Fixed priority, with agent 0 having priority over agent 1 优先级

- Grant will be asserted as long as request is asserted. 发出请求时输出grant断言

Once we have the specs, we can draw the block diagram, which is basically an abstraction of the data flow through a system (what goes into or comes out of the black boxes?). Since the example that we have taken is a simple one, we can have a block diagram as shown below. We don't worry about what's inside the magical black boxes just yet.

2.3Block diagram of arbiter

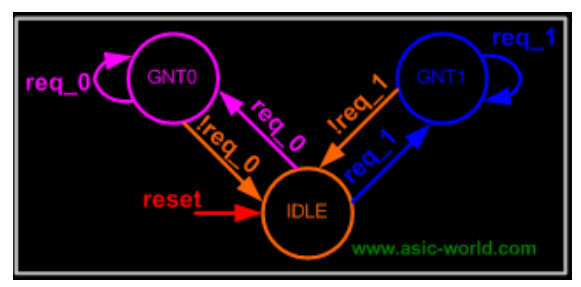

- Now, if we were designing this machine without Verilog, the standard procedure would dictate that we draw a state machine. From there, we'd make a truth table with state transitions for each flip-flop. And after that we'd draw Karnaugh maps, and from K-maps we could get the optimized circuit. This method works just fine for small designs, but with large designs this flow becomes complicated and error prone. This is where Verilog comes in and shows us another way.从顶层模块直接设计状态机容易出错,将顶层模块划分为若干子模块可以简化设计

2.4Low level design

Each of the circles represents a state that the machine can be in. Each state corresponds to an output. The arrows between the states are state transitions, labeled by the event that causes the transition. For instance, the leftmost orange arrow means that if the machine is in state GNT0 (outputting the signal that corresponds to GNT0) and receives an input of !req_0, the machine moves to state IDLE and outputs the signal that corresponds to that. This state machine describes all the logic of the system that you'll need. The next step is to put it all in Verilog.

Each of the circles represents a state that the machine can be in. Each state corresponds to an output. The arrows between the states are state transitions, labeled by the event that causes the transition. For instance, the leftmost orange arrow means that if the machine is in state GNT0 (outputting the signal that corresponds to GNT0) and receives an input of !req_0, the machine moves to state IDLE and outputs the signal that corresponds to that. This state machine describes all the logic of the system that you'll need.* The next step is to put it all in Verilog.*=详细的介绍看网站,=)

2.5两种设计方法

- 第一种设计方法是采用状态机设计

// 方法2 采用状态机实现

module arbiter_1 (

input clk,

input reset,//high activate asynchronous

input req_0,req_1,//agent 0 having priority over agent 1

output reg gnt_0,gnt_1

);

reg [2:0] state,next_state;

parameter IDLE = 3'b001,GNT0 = 3'b010,GNT1 = 3'b100;

always @(posedge clk or posedge reset) begin

if (reset) begin

state <= IDLE;

end

else begin

state <= next_state;

end

end

always @(*) begin

case (state)

IDLE: begin if(req_0==1'b1) next_state = GNT0;

else if(req_1==1'b1) next_state = GNT1;

else next_state = IDLE; end

GNT0:begin if(req_0==1'b1) next_state = GNT0;

// else if(req_1==1'b1) next_state = GNT1;

else next_state = IDLE;end

GNT1:begin if(req_1==1'b1) next_state = GNT1;

// else if(req_1==1'b1) next_state = GNT1;

else next_state = IDLE;end

default:begin next_state = IDLE; end

endcase

end

always @(*) begin

if(state == GNT0)begin

gnt_0 = 1'b1;

gnt_1 = 1'b0;

end

else if(state == GNT1)begin

gnt_1 = 1'b1;

gnt_0 = 1'b0;

end

else begin

gnt_0 = 1'b0;

gnt_1 = 1'b0;

end

end

endmodule

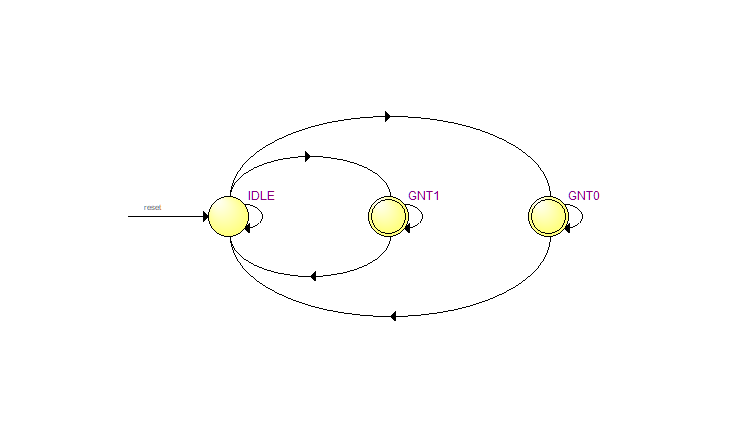

- 在quartus II里面生成的状态图

- 第二种采用普通写法

// 方法2

module arbiter (

input clk,

input reset,//high activate asynchronous

input req_0,req_1,//agent 0 having priority over agent 1

output reg gnt_0,gnt_1

);

always @(posedge clk or posedge reset) begin

if (reset==1'b1) begin

gnt_0 <= 1'b0;

gnt_1 <= 1'b0;

end

else if(req_0==1'b1)begin

gnt_0 = 1'b1;

gnt_1 = 1'b0;

end

else if(req_1 == 1'b1)begin

gnt_1= 1'b1;

gnt_0= 1'b0;

end

else begin

gnt_1= 1'b0;

gnt_0= 1'b0;

end

end

endmodule

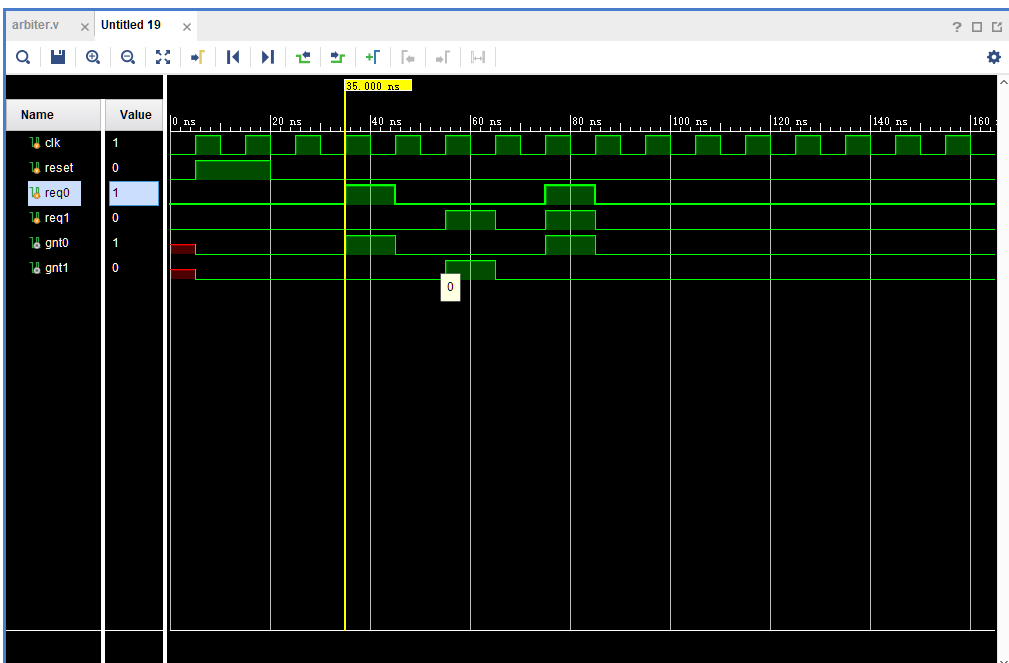

verification——TestBench

- 使用网站上写好的code去测试设计结果。测试就是对输入施加特定激励,看输出是满足期望

`timescale 1ns / 1ps

module arbiter_tb;

// 输入采用寄存器reg类型,输入采用线网类型wire

reg clock, reset, req0,req1;

wire gnt0,gnt1;

// 初始化输入

initial begin

$monitor ("req0=%b,req1=%b,gnt0=%b,gnt1=%b", req0,req1,gnt0,gnt1);//检测信号

clock = 0;

reset = 0;

req0 = 0;

req1 = 0;

#5 reset = 1;

#15 reset = 0;

#10 req0 = 1;

#10 req0 = 0;

#10 req1 = 1;

#10 req1 = 0;

#10 {req0,req1} = 2'b11;

#10 {req0,req1} = 2'b00;

#10 $finish;//执行到此处结束 运行90ns停止仿真

end

//周期为10ns的时钟

always begin

#5 clock = !clock;

end

//例化 将驱动添加到对应模块上的输入

arbiter U0 (

.clock (clock),

.reset (reset),

.req_0 (req0),

.req_1 (req1),

.gnt_0 (gnt0),

.gnt_1 (gnt1)

);

endmodule

- 仿真图:两种写法一致

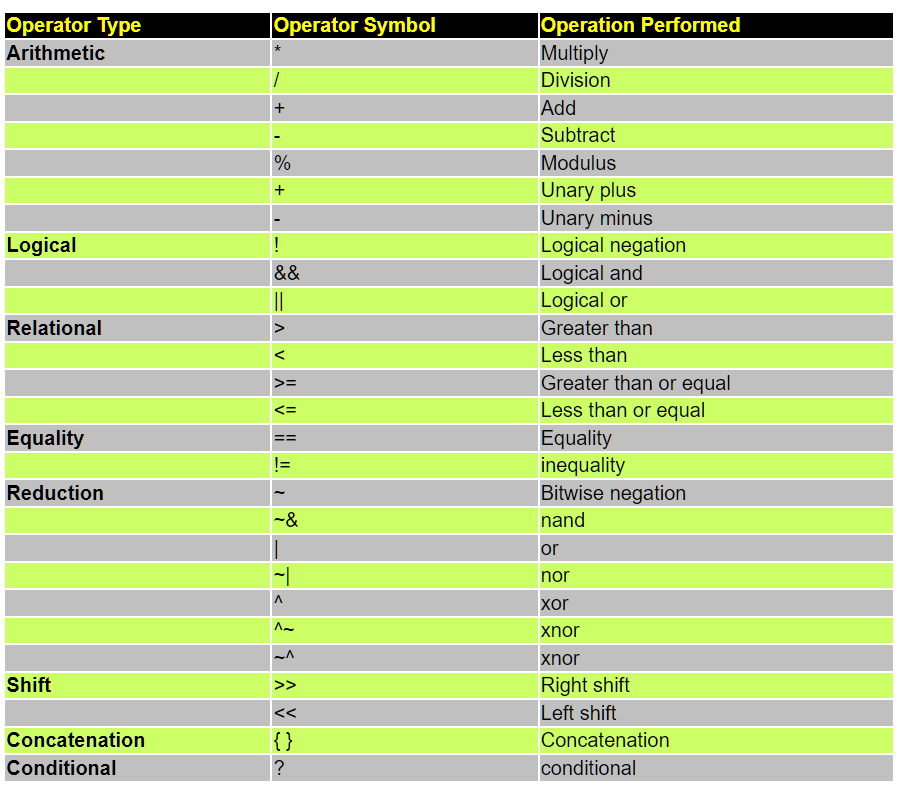

- 附录:Verilog里面的操作符号 Operator symbol,和C很相似!

SystemVerilog Tutorial的更多相关文章

- SystemVerilog搭建验证平台使用DPI时遇到的问题及解决方案

本文目的在于分享一下把DPI稿能用了的过程,主要说一下平台其他部分搭建好之后,在完成DPI相关工作阶段遇到的问题,以及解决的办法. 工作环境:win10 64bit, Questasim 10.1b ...

- SystemVerilog搭建APB_I2C IP 层次化验证平台

一.前言 近期疫情严重,身为社畜的我只能在家中继续钻研技术了.之前写过一篇关于搭建FIFO验证平台的博文,利用SV的OOP特性对FIFO进行初步验证,但有很多不足之处,比如结构不够规范.验证组件类不独 ...

- systemverilog 字符串类型

转载:https://blog.csdn.net/Holden_Liu/article/details/100727957 传统的Veriog仅仅支持文字表述上的字符串, 而SystemVerilog ...

- [翻译+山寨]Hangfire Highlighter Tutorial

前言 Hangfire是一个开源且商业免费使用的工具函数库.可以让你非常容易地在ASP.NET应用(也可以不在ASP.NET应用)中执行多种类型的后台任务,而无需自行定制开发和管理基于Windows ...

- Django 1.7 Tutorial 学习笔记

官方教程在这里 : Here 写在前面的废话:)) 以前学习新东西,第一想到的是找本入门教程,按照书上做一遍.现在看了各种网上的入门教程后,我觉得还是看官方Tutorial靠谱.书的弊端一说一大推 本 ...

- thrift 服务端linux C ++ 与客户端 windows python 环境配置(thrift 自带tutorial为例)

关于Thrift文档化的确是做的不好.摸索了很久才终于把跨linux与windows跨C++与python语言的配置成功完成.以下是步骤: 1) Linux下环境配置 ...

- Hive Tutorial(上)(Hive 入门指导)

用户指导 Hive 指导 Hive指导 概念 Hive是什么 Hive不是什么 获得和开始 数据单元 类型系统 内置操作符和方法 语言性能 用法和例子(在<下>里面) 概念 Hive是什么 ...

- Home / Python MySQL Tutorial / Calling MySQL Stored Procedures in Python Calling MySQL Stored Procedures in Python

f you are not familiar with MySQL stored procedures or want to review it as a refresher, you can fol ...

- Using FreeMarker templates (FTL)- Tutorial

Lars Vogel, (c) 2012, 2016 vogella GmbHVersion 1.4,06.10.2016 Table of Contents 1. Introduction to F ...

- Oracle Forms 10g Tutorial Ebook Download - Oracle Forms Blog

A step by step tutorial for Oracle Forms 10g development. This guide is helpful for freshers in Orac ...

随机推荐

- java逻辑运算中异或^

本文主要阐明逻辑运算符^(异或)的作用 a ^ b,相异为真,相同为假. 注意,异或运算,还能交换两个变量. int a = 1; int b = 2; System.out.println(&quo ...

- 二阶段目标检测网络-Cascade RCNN 详解

摘要 1,介绍 1.1,Faster RCNN 回顾 1.2,mismatch 问题 2,实验分析 2.1,改变IoU阈值对Detector性能的影响 2.2,提高IoU阈值的影响 2.3,和Iter ...

- java计算器༼༎ຶᴗ༎ຶ༽༼༎ຶᴗ༎ຶ༽༼༎ຶᴗ༎ຶ༽༼༎ຶᴗ༎ຶ༽,又是掉发的一天

题目: 给你一个字符串表达式 s ,请你实现一个基本计算器来计算并返回它的值. 注意:不允许使用任何将字符串作为数学表达式计算的内置函数,比如 eval() . 示例 1: 输入:s = " ...

- 中国蚁剑 - AntSword

中国蚁剑 - AntSword 中国蚁剑是一种跨平台操作工具,它主要提供给用户用于有效的网络渗透测试以及进行正常运行的网站. 否则任何人不得将网站用于其无效用途以及可能的等目的.自己承担并追究其相关责 ...

- [编程基础] C++多线程入门6-事件处理的需求

原始C++标准仅支持单线程编程.新的C++标准(称为C++11或C++0x)于2011年发布.在C++11中,引入了新的线程库.因此运行本文程序需要C++至少符合C++11标准. 文章目录 6 事件处 ...

- [数据结构]克鲁斯卡尔(Kruskal)算法

算法的概念 与Prim算法从顶点开始扩展最小生成树不同,Kruskal算法是一种按权值的递增次序选择合适的边来构造最小生成树的方法.假设N=(V,E)是连通网,对应的最小生成树T=(Vt,Et),Kr ...

- 消息队列(Message Query)的初学习

消息队列(Message Query)的初学习 摘要:本篇笔记主要记录了对于消息队列概念的初次学习.消息队列的基础知识. 目录 消息队列(Message Query)的初学习 1.何为消息? 2. ...

- 对 Pulsar 集群的压测与优化

前言 这段时间在做 MQ(Pulsar)相关的治理工作,其中一个部分内容关于消息队列的升级,比如: 一键创建一个测试集群. 运行一批测试用例,覆盖我们线上使用到的功能,并输出测试报告. 模拟压测,输出 ...

- 动力节点——day02

ipconfig ip地址的配置信息,ipconfig -all 更详细的配置信息 查看两台计算机是否可以正常通信 ping ip地址/域名(-t) 快捷键:ctrl+c复制 ctrl+v粘贴 c ...

- Linux环境下:程序的链接, 装载和库[静态链接]

看以下例子 main.c extern int x; int main() { int y = 100; swap(&x,&y); return 0; } int x = 1; voi ...