FPGA芯片内部硬件介绍

FPGA芯片内部硬件介绍

FPGA(Filed programmable gate device):现场可编程逻辑器件

FPGA基于查找表加触发器的结构,采用SRAM工艺,也有采用flash或者反熔丝工艺;主要应用高速、高密度大的数字电路设计。

FPGA由可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源(时钟/长线/短线)、底层嵌入功能单元、内嵌专用的硬核等组成;

目前市场上应用比较广泛的FPGA芯片主要来自Altera与Xilinx。另外还有其它厂家的一些低端芯片(Actel、Lattice)。

这里主要介绍AlteraCyclone II系列FPGA的内部硬件结构:

- FPGA器件结构

- 可编程输入/输出单元IOE

- 可编程逻辑单元LE

- 嵌入式块RAM

- 布线资源

- 底层嵌入功能单元

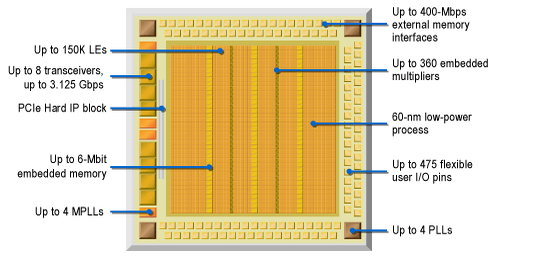

FPGA器件结构

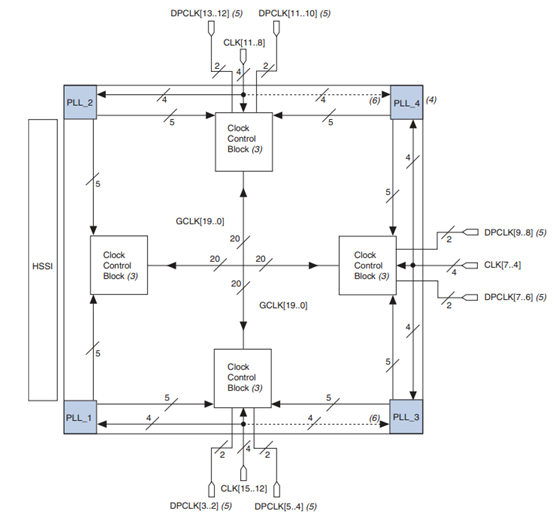

Altera cyclone IV器件结构

FPGA的内部结构包括:

- 可编程逻辑门阵列,由最小单元LE组成

- 可编程输入输出单元IOE

- 嵌入式RAM块,为M4K块,每个的存储量为4K,掉电丢失

- 布线网络

- PLL锁相环,EP4CE6E22C8N最大的倍频至250MHz,这也是该芯片的最大工作频率

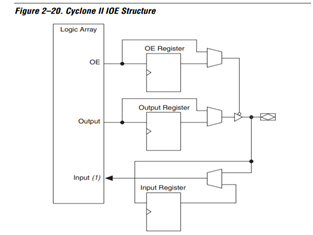

可编程输入/输出单元IOE

可编程I/O,可配置成OC门、三态门、双向IO、单端/差分等;支持各种不同的I/O标准:LVTTL、LVCOMS、SSTL、LVDS、HSTL、PCI等;

Altera 器件IOE结构

Altera器件的输入输出结构:可配置成三态、输入/输出、双向IO

Altera器件中cyclone系列中的IOE结构是基本的输入、输出、使能的触发器结构。

可编程逻辑单元LE

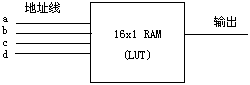

基本可编程逻辑单元LE由查找表(Look up table)触发器(FF)组成,而LE是组成LAB的最小单元;

LUT一般是4输入查找表,高端器件(xilinx v5)采用LUT-6结构;LUT可看成4位地址线的16x1的RAM 结构。

FF是可编程的触发器,可配置成同步/异步复位、同步/异步置位、使能、装载等功能触发器。

可编程逻辑块:

Altera:LAB

Xilinx:CLB

Xilinx CLB由四个SLICE构成;而Altera的LAB由16个/8个LE构成;

基本逻辑单元LE/SLICE:

Altera:LE

Xilinx:SLICE

xilinx 为SLICE:包括两个LUT-4/两个FF;

altera为LE:包括一个LUT-4/一个FF;

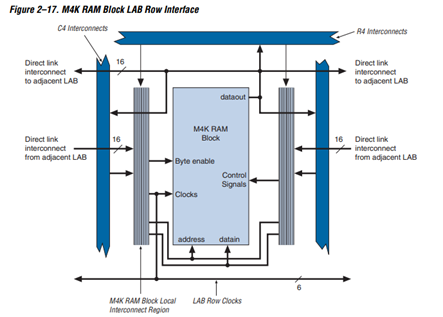

嵌入式块RAM

嵌入式块RAM可配置单/双端口RAM、伪双端口RAM、ROM、FIFO、SHIFT、CAM等;不同厂家的块RAM大小不一样:

Altera:M512、M4K M4K、M-RAM(512K);

Xilinx:18kbit;

Lattic:9kbit;

Altera:M4K:

布线资源

全局布线资源:用于全局时钟/全局复位/全局置位布线;

长线资源:用于BANK或者嵌入式功能单元的高速信号或者第二全局时钟的布线;

短线资源:用于其中逻辑单元间的逻辑互联与布线;

全局布线资源:

全局时钟树:

底层嵌入式功能块

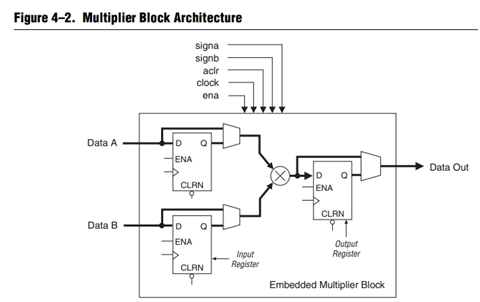

主要是指PLL/DPLL、DCM、DSP48、乘法器、嵌入式硬核/软核;

Xilinx:DCM、DSP48/48E、DPLL、Multiplier等

Altera:PLL/EPLL/FPLL、DSPcore等;

Multiplier结构

PLL/DCM:嵌入式锁相环

Altera:PLL

Xilinx:DCM

Altera的Cyclone II器件最多有四个PLL,分布在芯片四个角;需要主要的是Altera的PLL是模拟锁相环,在电源/地方面要做考虑。

Xilinx的spatan-3器件最多有四个DCM,也是分布在芯片四个角。

两者的区别:Altera的PLL可支持较低的输入频率,可Xilinx的DCM支持的最低锁相频率为24/32MHz;但Xilinx的高端器件Virtex-5的DPLL可达到很低的输入频率。

内嵌专用硬核

指高速串行收发器;GMAC、SERDES、PCIe等;

Xilinx:GMAC、SERDES、PCI、GTX、GRX

Atera:GMAC、SERDES、PCIe、SPI.4/SFI.5

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

FPGA芯片内部硬件介绍的更多相关文章

- FPGA内部硬件结构简介

我们知道FPGA内部有很多可供用户任意配置的资源,其中包括:可编程逻辑.可编程I/O.互连线.IP核等资源,很多学过数字电路的人都知道与或非门可以构成几乎所有的数字电路,但是FPGA内部最基本的主要单 ...

- 嵌入式开发之zynq——赛灵思的一款两a9加一fpga芯片的开发板

没办法,回家入职新公司,做通信的,用到这款zynq加ad9163射频架构的开发版,要我做驱动,这可是初次接触zynq,带fpga的集成芯片,心里还是有点惊喜和忧愁,忧愁怎么最快啃下这个硬骨头,好吧上网 ...

- ArduinoYun教程之ArduinoYun硬件介绍

ArduinoYun教程之ArduinoYun硬件介绍 ArduinoYun的电源插座 Arduino Yun有两排插座,这些插座可以按类型分为三类:电源.数字IO和模拟输入.电源部分主要集中在如图1 ...

- s3c2440裸机-UART编程(一、UART硬件介绍及传输原理)

1.uart硬件介绍 UART的全称是Universal Asynchronous Receiver and Transmitter(异步收发器). uart主要用于: 1.打印调试 2.数据传输 串 ...

- 用显微镜观察cpu芯片内部

1. 先找到一块Intel公司的奔三(Pentium III)Coppermine芯片,主频800MHZ,生产于2000年.(我查了一下,网上的报价现在是15~30元人民币/块.) 下面是这块CPU的 ...

- 《VR入门系列教程》之6---VR硬件介绍及DK1

第二章 VR硬件介绍 本章主要介绍当前比较流行的消费版VR设备,包括VR头显以及应用运行的PC和手机平台. 即使是在这工业高速发展的时代,一些大厂(比如Facebook的Oculus ...

- 操作系统(1)——X86-32硬件介绍、实验环境相关配置、uCore部分技巧介绍

实验环境 本文假设已经创建虚拟机并配置好Ubuntu 16.04(网上太多教程了,所以这里就不赘述了). X86-32硬件介绍 x86指的是80386这种机器(一种32位CPU,在早期得到了广泛的应用 ...

- 关于Quartus构建nios软核以及eclipse建立c语言工程以及成功下载到FPGA芯片过程遇到的各种问题以及解决方法详解

这不是一篇构建nios的教程,而是遇到的各种问题以及解决方法.至于构建教程,网上一大把,我推荐正点原子的FPGA教程,比较新,比较详细,通俗易懂!!! 这里以一个点亮LED灯的Nios软核为例,很明显 ...

- eclipse建立c语言工程以及成功下载到FPGA芯片过程遇到的各种问题以及解决方法详解

推荐大家预先建立好一个工程目录文件夹,确实挺好用,参考正点原子的pdf教程,如下图所示, 我们eclipse在software文件夹建立一个workspace即可 选择用helloworld模板建立工 ...

随机推荐

- [JS]笔记14之事件委托

-->什么是事件委托-->事件委托原理-->事件委托优点-->事件源 / 目标源 一.什么是事件委托 通俗的讲,onclick,onmouseover,onmouseout等这 ...

- js 获取鼠标选中值

if (window.getSelection) {//一般浏览器 userSelection = window.getSelection();} else if (document.selectio ...

- 使用jq插入节点

.append()和.appendTo()两种方法功能相同,主要的不同是语法——内容和目标的位置不同 append()前面是要选择的对象,后面是要在对象内插入的元素内容 appendTo()前面是要插 ...

- iOS 学习 - 19 结构体

//创建新类型typedef struct { int age; ];//最大字节为 20 }Student; Student value2 = {,*strcpy(value2.name, &quo ...

- (一)Maven初步了解与认识

Apache Maven是一个软件项目管理的综合工具.基于项目对象模型(POM)的概念,提供了帮助管理构建.文档.报告.依赖.发布等方法,Maven简化和标准化项目建设过程.处理编译,分配,文档,团队 ...

- TortoiseSVN提交提示423 Locked的解决办法

往svn上提交文件时,文件可能被另一个人占用,这时提交就会报423Locked错误. 此办法是阅读官方文档(TortoiseSVN-1.6.16-zh_CN.pdf) 4.21 锁部分提供的办法: 首 ...

- vimrc

我的vimrc https://github.com/juandx/vimrc 当然得装vundle git clone https://github.com/VundleVim/Vundle.vim ...

- [Erlang 0106] Erlang实现Apple Push Notifications消息推送

我们的IOS移动应用要实现消息推送,告诉用户有多少条消息未读,类似下图的效果(笑果),特把APNS和Erlang相关解决方案笔记于此备忘. 上面图片中是Apple Notif ...

- Ajax中Get请求与Post请求的区别

Get请求和Post请求的区别 1.使用Get请求时,参数在URL中显示,而使用Post方式,则不会显示出来 2.使用Get请求发送数据量小,Post请求发送数据量大 例子 页面的HTML代码: &l ...

- mysqldump: Got error: 1142: SELECT, LOCK TABLES command denied to user 'root'@'localhost' for table 'accounts' when using LOCK TABLES

AutoMySQLBackup备份时,出现mysqldump: Got error: 1142: SELECT, LOCK TABLES command denied to user 'root'@' ...