AXI-Lite总线及其自定义IP核使用分析总结

ZYNQ的优势在于通过高效的接口总线组成了ARM+FPGA的架构。我认为两者是互为底层的,当进行算法验证时,ARM端现有的硬件控制器和库函数可以很方便地连接外设,而不像FPGA设计那样完全写出接口时序和控制状态机。这样ARM会被PL端抽象成“接口资源”;当进行多任务处理时,各个PL端IP核又作为ARM的底层被调用,此时CPU仅作为“决策者”,为各个IP核分配任务;当实现复杂算法时,底层算法结构规整可并行,数据量大,实时性要求高,而上层算法则完全相反,并且控制流程复杂,灵活性高。因此PL实现底层算法后将运算结果交给PS端软件后续处理是非常高效的。

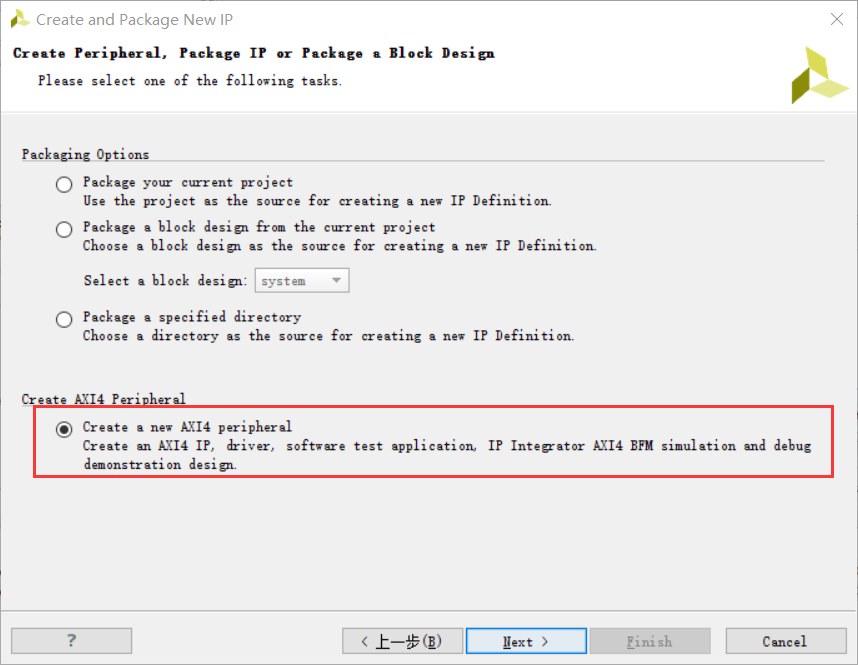

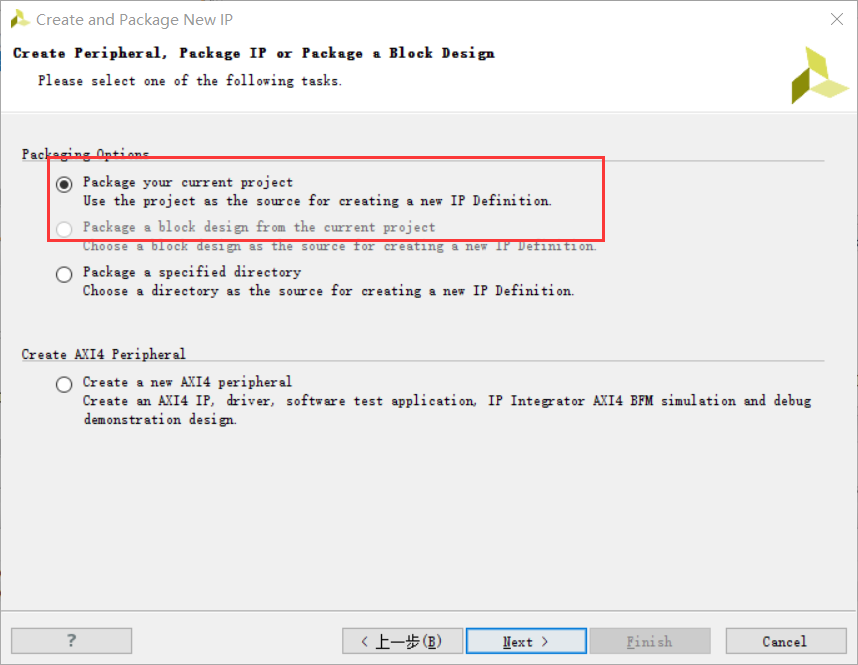

因此PS与PL端数据交互是至关重要的,在传输数据量小的控制 配置初始化等应用场合下无疑会选择简单的AXI-Lite总线,以下对总线接口 自定义IP操作及使用注意事项加以说明。打开Vivado新建工程,选择主菜单栏Tools选项下的Create and package new IP...

选择创建新的AXI4外设可以自动生成总线接口逻辑

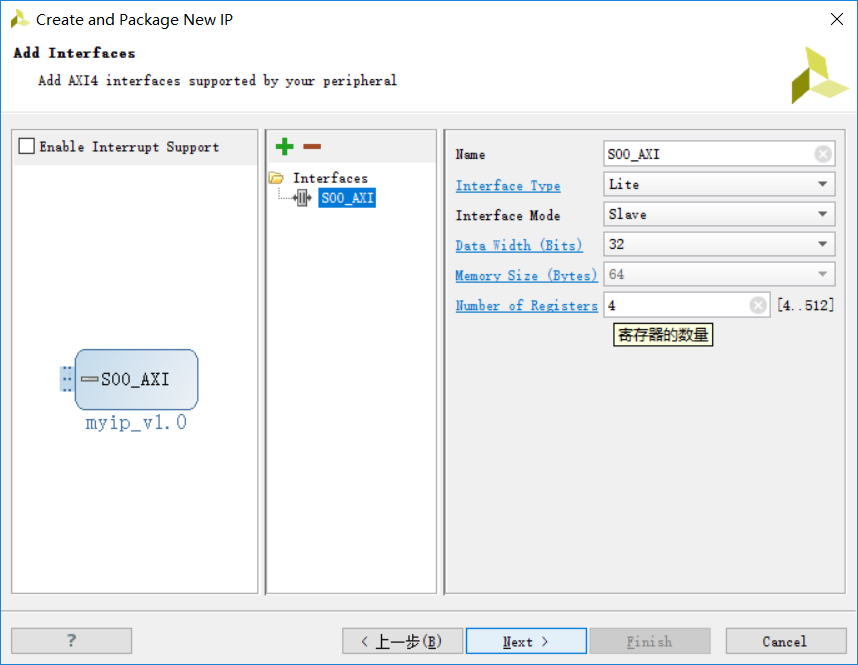

采用AXI-Lite总线的Slave模式,只有寄存器数量是可修改的。注意数据位宽固定32bit,计算机中数据以字节(8bit)为单位存储,因此各个寄存器地址的偏移量为4.这一点在写软件时会有所体现。

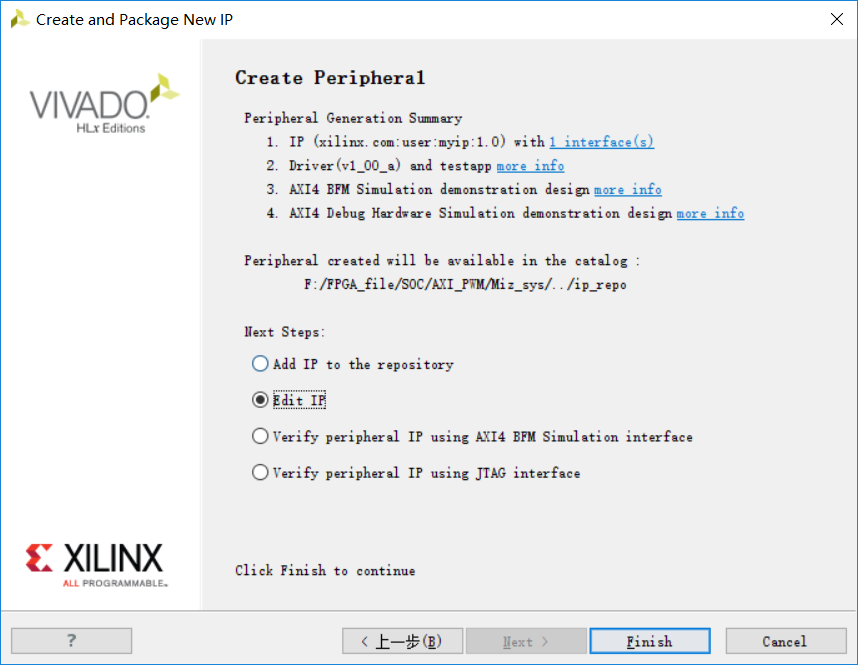

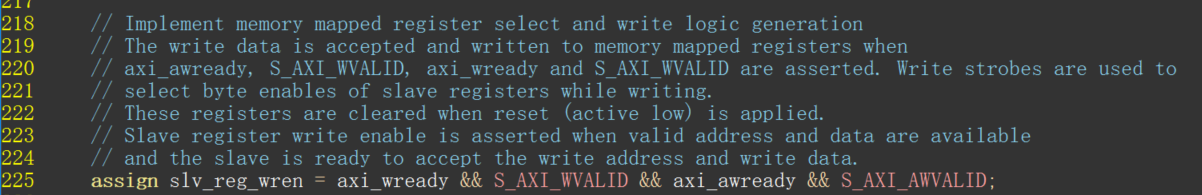

选择编辑IP,打开的工程由顶层Wrapper和AXI-Lite总线接口逻辑组成。关闭自动弹出的IP封装向导,当添加好用户自定义逻辑后再重新封装,否则封装的仅仅是软件生成的接口逻辑。接口比较多,分为写通道和通道,而每个通道基本逻辑又由地址通道和数据通道组成。除了以上四个通道外,写通道包含应答通道以返回CPU确认信息。每个接口以S_AXI_开头,之后AW代表地址写,W代表数据写,AR代表地址读,R代表数据读,B代表响应。关于AXI总线的基本特性在之前的博文中已有阐述,无非就是READY和VLD信号的“握手”。因此这五个核心信号包括VALID DATA和READY。

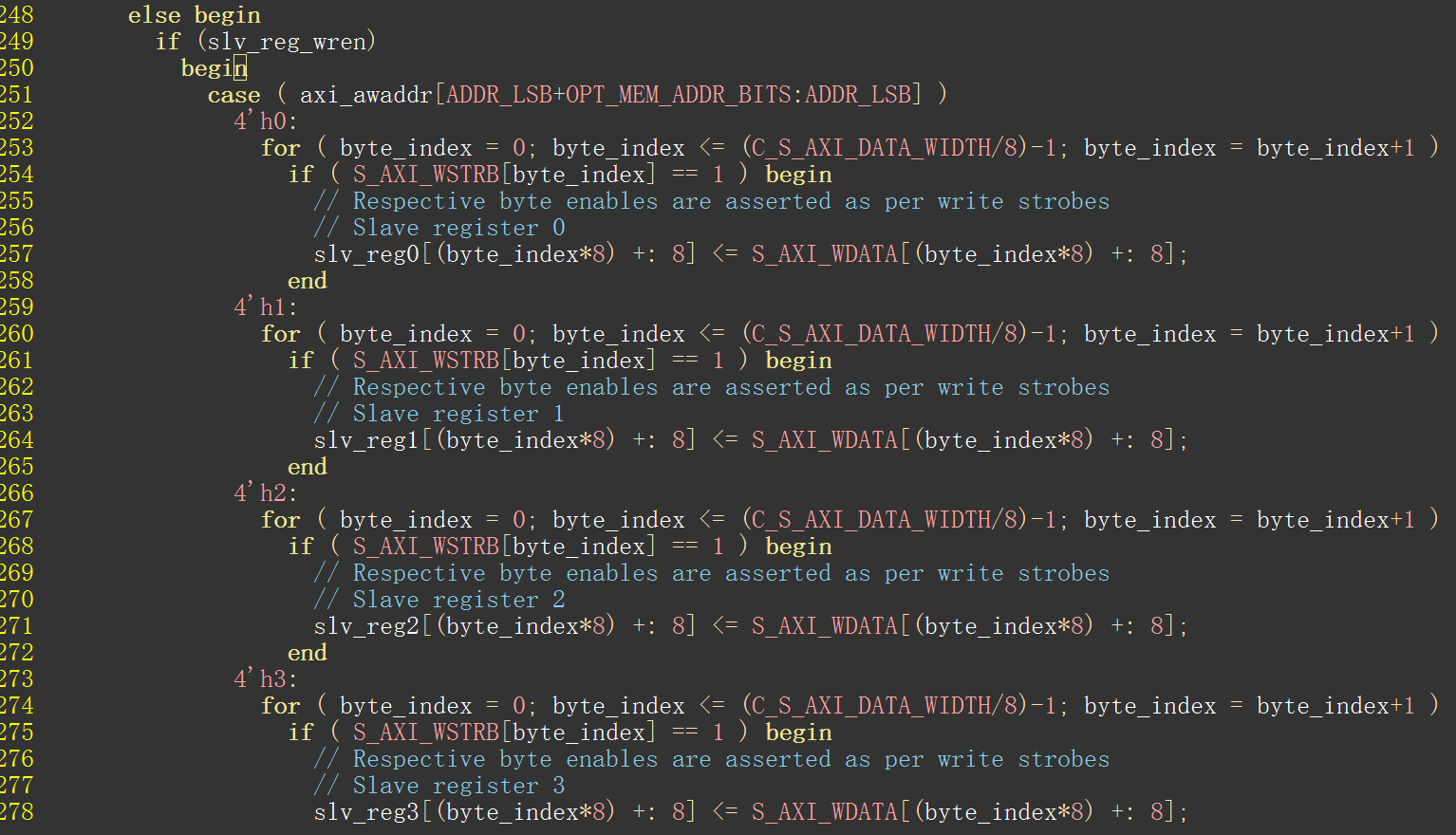

从上述代码可以看出,只有在写地址通道和写数据通道均握手成功时才能有效写入寄存器。

根据参数声明和寄存器选择与写操作逻辑可知,是根据地址[5:2]这四位来判断写入哪一个寄存器。如:

地址0,即6'b0000_00

地址4,即6'b0001_00

地址8,即6'b0010_00

地址12,即6'b0011_00

因此[5:2]部分依次是0 1 2 3,从而验证了之前地址偏移量是4的观点。这里的slv_regx信号就是我们需要送入自定义逻辑的控制信号了。

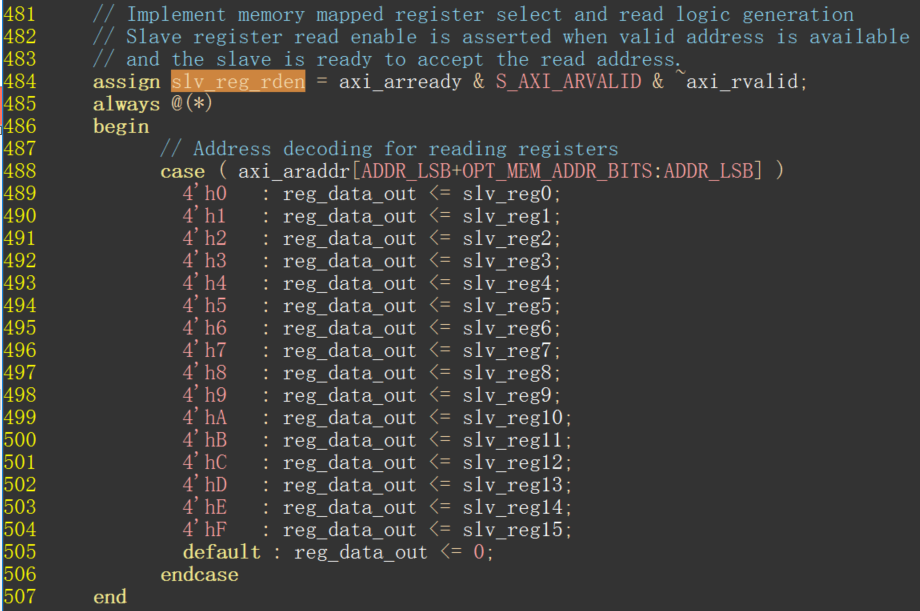

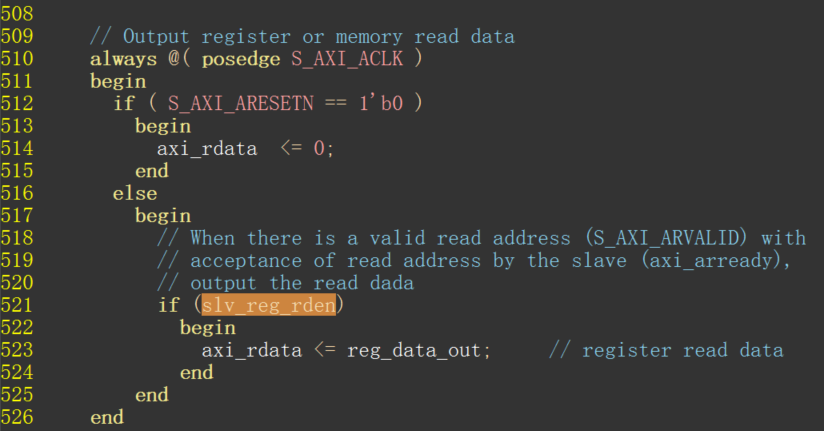

上面是读操作核心逻辑,当从机收到有效的读操作地址且准备好后,会将寄存器数据送回到主机。换句话说读操作读到的数据仅是单纯写入的控制数据,并不是自定义逻辑的处理结果。所以读操作要将489行开始的右侧数据源更换成自定义逻辑处理后有效数据。如:reg_data_out <= user_module_dout;

内部添加的自定义逻辑可以直接写在该模块内,也可以例化自定义模块或IP核。最后封装当前工程得到支持AXI-Lite总线的自定义IP核。

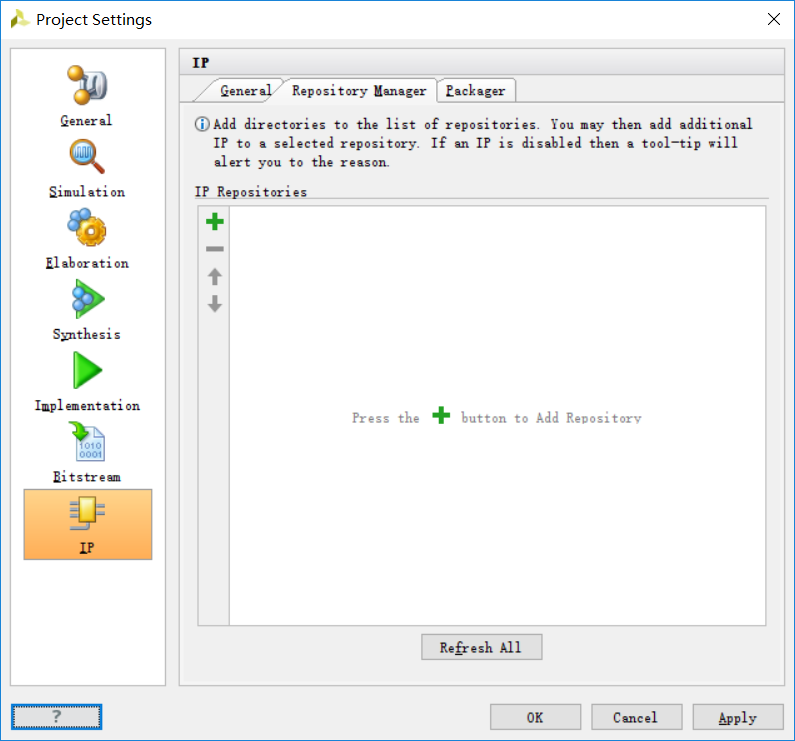

打开需要例化刚才产生IP核的工程,选择Project Setting -> IP -> Respository Manger添加IP核路径或,在block design或 IP Catalog中调用。

AXI-Lite总线及其自定义IP核使用分析总结的更多相关文章

- 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计

本帖最后由 xinxincaijq 于 2013-1-9 10:27 编辑 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计 转自博客:http:// ...

- Vivado 调用自定义IP核

关于Vivado如何创建自定义IP核有大量的参考文章,这里就不多加阐述了,本文目的主要是解决如何在新建工程中引用其它工程已经自定义封装好的IP核,从而实现自定义IP核的灵活复用. 举个例子,我们的目标 ...

- vivado设计四:自定义IP核测试

在vivado设计三中:http://blog.chinaaet.com/detail/37177已经建立了vivado工程和封装好了自定义IP核. 那么接下来,我们对这个自定义IP核进行测试了:我们 ...

- vivado设计三:一步一步生成自己的自定义IP核

开发环境:xp vivado2013.4 基于AXI-Lite的用户自定义IP核设计 这里以用户自定义led_ip为例: 1.建立工程 和设计一过程一样,见vivado设计一http://blog. ...

- NIOS II 自定义IP核的静态地址对齐和动态地址对齐

如果使用静态地址对齐(每个寄存器在Avalon总线上占4个字节的地址)设置IP使用静态地址对齐的方式为,在hw.tcl脚本里加上一局话:set_interface_property as addres ...

- NIOS II 自定义IP核编写基本框架

关于自定义IP .接口 a.全局信号 时钟(Clk),复位(reset_n) b.avalon mm slave 地址(as_address) 片选(as_chipselect /as_chipsel ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- 基于AXI4总线卷积FPGA加速IP核的尝试

本文先总结不同AXI IP核的实现的方法,性能的对比,性能差异的分析,可能改进的方面.使用的硬件平台是Zedboard. 不同的AXI总线卷积加速模块的概况 这次实现并逐渐优化了三个版本的卷积加速模块 ...

- 关于Xilinx AXI Lite 源代码分析---自建带AXI接口的IP

关于Xilinx AXI Lite 源代码分析---自建带AXI接口的IP 首先需要注意此处寄存器数量的配置,它决定了slv_reg的个数. 读写数据,即是对寄存器slv_reg进行操作: 关于AXI ...

随机推荐

- 必须知道的Java八大排序算法

冒泡排序.简单选择.直接插入.快速排序.堆排序.希尔排序.归并排序.基数排序. 将其按排序方式分类如下图所示: 1.冒泡排序: 基本思想——在要排序的一组数中,对当前还未排好序的范围内的全部数据,自上 ...

- BBS论坛(三十二)

32.帖子排序功能完成 (1)front_index.html <ul class="post-group-head"> {% if current_sort==1 % ...

- .NET Core实战项目之CMS 第八章 设计篇-内容管理极简设计全过程

写在前面 上一篇文章中我带着大家进行了权限部分的极简设计,也仅仅是一个基本的权限设计.不过你完全可以基于这套权限系统设计你的更复杂的权限系统,当然更复杂的权限系统要根据你的业务来进行,因为任何脱离实际 ...

- 【转】关于 python ImportError: No module named 的问题

今天在 centos 下安装 python setup.py install 时报错:ImportError: No module named sysconfig, 当时急着用,就顺手直接源码编译了一 ...

- 再见了Server对象,拥抱IHostingEnvironment服务对象(.net core)

一.绝对路径 1.获取应用程序运行当前目录Directory.GetCurrentDirectory(). System.IO命名空间中存在Directory类,提供了获取应用程序运行当前目录的静态方 ...

- 漫画:SOA中怎样确定服务的粒度?

一般系统的服务划分有以下两种维度: 按模块划分 这个比较适用于偏业务的场景:复杂的系统,最好先按业务领域横向拆分成可独立部署的子系统,每个子系统内部再按技术纵向拆分成不同的子模块. 按角色划分 这个比 ...

- [工具向]__关于androidstudio工具使用过程中学习到的一些知识点简记

前言 在我学习android开发课程的过程中,我们通常只会关注编程语言上面的一些知识点与问题,而忽略了开发工具的使用上的一些遇到的一些知识,其实每一款IDE工具都是集编程语言大成而开发出来的,其中有很 ...

- 贝叶斯个性化排序(BPR)算法小结

在矩阵分解在协同过滤推荐算法中的应用中,我们讨论过像funkSVD之类的矩阵分解方法如何用于推荐.今天我们讲另一种在实际产品中用的比较多的推荐算法:贝叶斯个性化排序(Bayesian Personal ...

- Docker系列10—容器编排工具Docker Compose详解

本文收录在容器技术学习系列文章总目录 1.Docker Compose 概述 Compose是一个用于定义和运行多容器Docker应用程序的工具.使用Compose,您可以使用Compose文件来配置 ...

- 痞子衡嵌入式:飞思卡尔i.MX RT系列MCU启动那些事(1)- Boot简介

大家好,我是痞子衡,是正经搞技术的痞子.今天痞子衡给大家介绍的是飞思卡尔i.MX RT系列MCU的BootROM功能简介. 截止目前为止i.MX RT系列已公布的芯片有三款i.MXRT105x, i. ...