Verilog 奇数分频

代码:

module odd_div( );

parameter DIV_PARA = ; //分频系数,3即3分频

parameter DIV_PARA_2 = DIV_PARA >> ;

reg clk, rstn, clk_div_pos, clk_div_neg;

wire clk_div_out;

reg [:] cnt; initial begin

clk <= ;

rstn <= ;

# rstn <= ;

end always begin

# clk <= ;

# clk <= ;

end // 计数循环

always@(posedge clk or negedge rstn) begin

if (!rstn) begin

cnt <= 'd0;

end

else

if (cnt < (DIV_PARA-))

cnt <= cnt + ;

else

cnt <= ;

end

// 上升沿触发

always@(posedge clk or negedge rstn) begin

if (!rstn) begin

clk_div_pos <= ;

end

else begin

if (cnt < DIV_PARA_2)

clk_div_pos <= ;

else

clk_div_pos <= ;

end

end

// 下降沿触发

always@(negedge clk or negedge rstn) begin

if (!rstn) begin

clk_div_neg <= ;

end

else begin

if (cnt < DIV_PARA_2)

clk_div_neg <= ;

else

clk_div_neg <= ;

end

end

// 生成分频信号

assign clk_div_out = clk_div_pos | clk_div_neg; endmodule

这个代码比较简单,而且为了仿真方便,将dut和bench写在一个模块了。。。。

代码设计思路来自这个帖子 https://blog.csdn.net/lt66ds/article/details/10035187

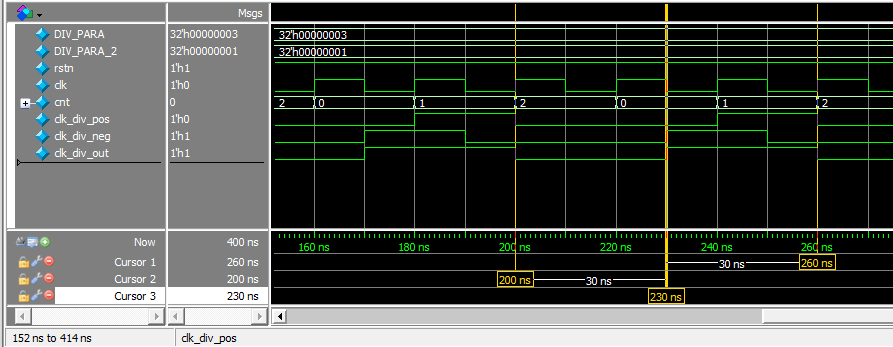

DIV_PARA参数设置分频系数,MoldelSIm仿真图如下

3分频:

DIV_PARA = 3

原时钟周期20ns,分频后的时钟周期为60ns,占空比为50%

5分频:

DIV_PARA = 5

原时钟周期20ns,分频后的时钟周期为100ns,占空比为50%

Verilog 奇数分频的更多相关文章

- verilog 奇数分频设计

module tw(clk,k_or,k1,k2); input clk; output k_or,k1,k2; reg [2:0] c1,c2; reg m1,m2; initial begin c ...

- FPGA三分频,五分频,奇数分频

我们在做FPGA设计时,有时会用到时钟频率奇数分频的频率,例如笔者FPGA的晶振为50M,当我们需要10M的时钟时,一种方式可以使用DCM或PLL获取,系统会内部分频到10M,但其实VERILOG内部 ...

- FPGA奇数分频

在FPGA设计中,分频是很常用的一个基本功能,一般来说,如果需要偶数分频即2次幂的整数倍,这个就很简单了,如2.4.8.16.32.64等这些以2的整数倍的. 这里说的是奇数倍分频,如时钟是100MH ...

- verilog实现奇数倍分频

在学习FPGA的过程中,最简单最基本的实验应该就是分频器了, 同时分频器也是FPGA设计中使用频率非常高的基本设计之一, 尽管在芯片厂家提供的IDE中集成了锁相环IP, 如altera 的PLL,Xi ...

- 【Verilog】verilog实现奇数次分频

实现占空比为50%的N倍奇数分频:首先进行上升沿触发进行模N计数,计数到某一个值时进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%的奇数n分频时钟.再者 同时进行下降沿触发的 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

- 基于verilog的分频器设计(奇偶分频原理及其电路实现:上)

在一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率太高)进行分频.分频器主要分为奇数分频,偶数分频,半整数分频和小数分频,在对时钟要求不是很严格的FPGA系统中 ...

- verilog分频模块设计

verilog设计: 分频器的设计: 分频器就是将一个时钟源的频率降低的过程(可以通过观察分频之后周期中包含几个原时钟周期来看是几分频),分频分为基数分频也分为偶数分频, 偶数分频的代码如下:(其中就 ...

- Verilog 任意(奇数/偶数)分频器

参加过一次笔试,让实现3分频,楼主当时是懵逼的,脑子里只知道同时利用上升沿和下降沿,本来写对了,慌张面试,脑子不管用了,(因为是手写,只能用脑子仿真)后来又给改错了,捂脸... 还是逻辑不清晰,现在自 ...

随机推荐

- Oracle EBS 应收发票取值

SELECT ct.trx_number ,ctl.description ,fnd_flex_ext.get_segs('SQLGL' ,'GL#' ,gcc.chart_of_accounts_i ...

- PLSQL中使用二维存储结构---二维数组

代码如下: --PLSQL中没有数组的概念 用TYPE 和Table of Record来代替多维数组--create by jenrry 20171028-- 1.0 建立存放列的测试表creat ...

- 《SQL Server 2008从入门到精通》--20180703

SELECT操作多表数据 关于连接的问题,在<SQL必知必会>学习笔记中已经讲到过,但是没有掌握完全,所以再学一下. JOIN连接 首先我们先来看一下最简单的连接.Products表和Ve ...

- C# 数据上传(自用笔记)

#region 数据上传 [HttpPost] public ActionResult UploadFile() { HttpFileCollectionBase files = Request.Fi ...

- 将Model对象转换成json文本或者json二进制文件

将Model对象转换成json文本或者json二进制文件 https://github.com/casatwy/AnyJson 注意:经过测试,不能够直接处理字典或者数组 主要源码的注释 AJTran ...

- Linux为grub菜单加密码

为grub菜单加密码 加入密码后,再次进入单用户或者给下次管理grub需要输入密码 加密操作 /sbin/grub-md5-crypt # 之后输入2次密码会生成加密后字符串 编辑grub加载文件 v ...

- matlab操作(整理)

http://blog.csdn.net/ysuncn/article/details/1741828 http://zhan.renren.com/h5/entry/3602888498000464 ...

- [2018HN省队集训D8T1] 杀毒软件

[2018HN省队集训D8T1] 杀毒软件 题意 给定一个 \(m\) 个01串的字典以及一个长度为 \(n\) 的 01? 序列. 对这个序列进行 \(q\) 次操作, 修改某个位置的字符情况以及查 ...

- 第一篇,编译生成libcef_dll_wrapper

因为工作原因需要在程序里面嵌入地图,在网上看了百度地图和高德地图都没有提供c++的接口,提供有web接口,那只好在程序里面嵌入web控件了,第一想到的是web browser控件,接着脑海里又想到IE ...

- XtraEditors三、LookUpEdit、GridLookUpEdit、SearchLookUpEdit

https://documentation.devexpress.com/WindowsForms/DevExpress.XtraEditors.LookUpEditBase.class 一.Look ...