7系列高速收发器总结 GTP IP核使用篇

上一篇7系列收发器博文讲解了GTP IP核的基本配置,本文继续分析如何将它使用起来。生成IP核后打开example design,先看看工程中包含的文件结构。

顶层文件下包含了gtp ip核系统顶层文件、frame_gen以及frame_check三类模块。frame_gen和frame_check用于测试过程中的数据包产生和接收检测(由于我在配置IP核时使能了两个通道,因此工程中有两组frame_gen和frame_check模块),gen模块读发送样式,check模块则将接收到数据与本地存储样式对比,从而判断数据传输是否正确。下面截取一段gen模块内代码:

发现gen模块是通过系统函数$readmem读取gt_rom_init_tx.dat文件来初始化rom,发送数据则直接从rom中读取。虽然$readmem和initial是不可综合语句,但其功能与.mif文件初始化ROM IP核是类似的。check模块与gen模块类似,但有一点比较值得借鉴。

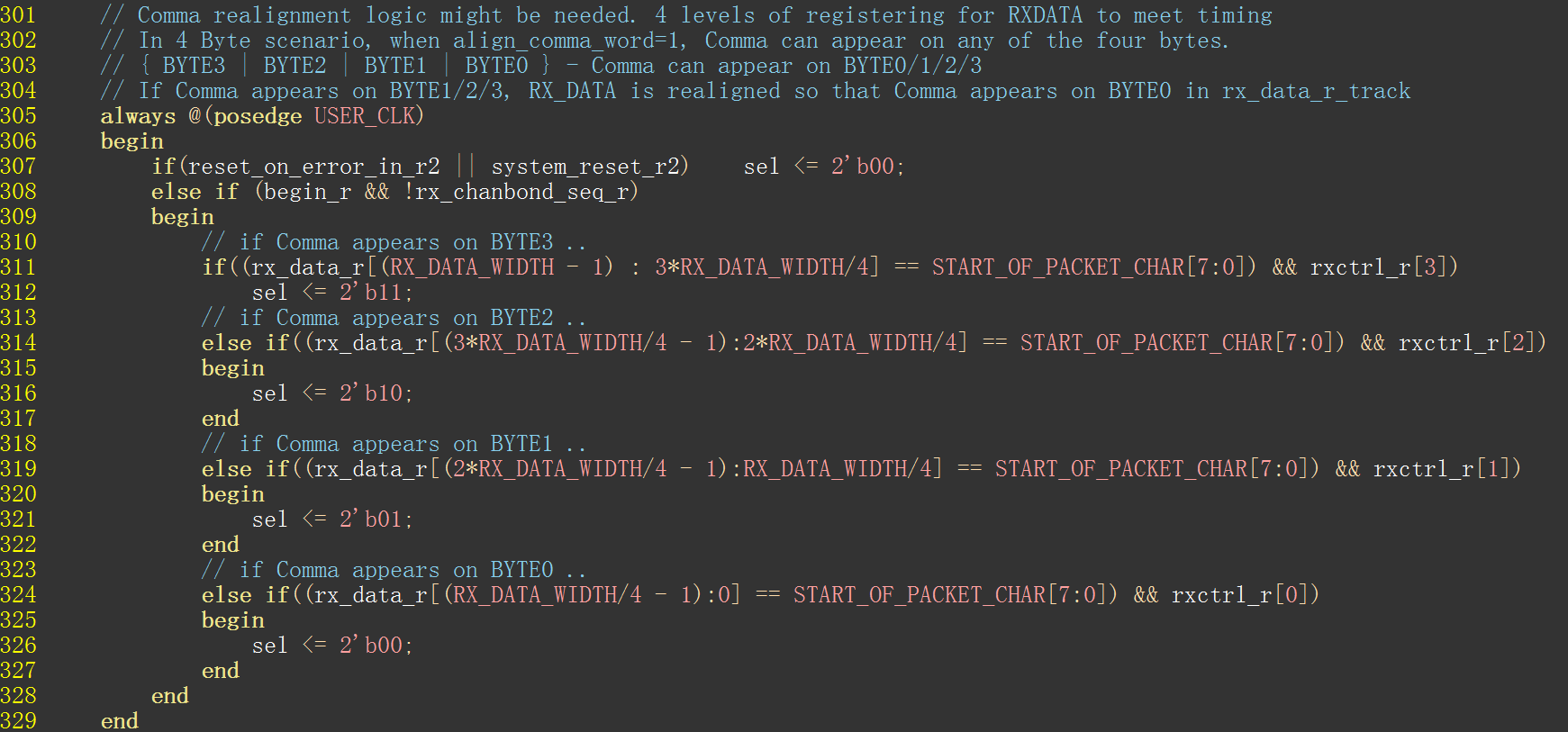

根据上边的注释可以看出,这个IP核在使用32bit用户数据位宽时,会发生错位现象。因此发送数据时所有comma码要放在32bit数据四个字节的同一字节中,最常见的是均放在最低字节,这样接收端可以根据控制字指示信号为1的位置找出错位情况,进而读数据进行重新对齐。比如当rxctrl == 4'b1000,则错误情况和重对齐方式如下:

d0'代表上一个数据的最低字节部分。其他错位情况的重对齐方式同理,现在看下check模块中根据sel信号对接收数据重对齐的逻辑。

可以看出重对齐方式与刚才讲的方法一致。因此当测试完毕后,去除frame_gen和frame_check模块并将gt数据端口开放到顶层后,接收端用户侧也要有类似的逻辑防止数据错位。

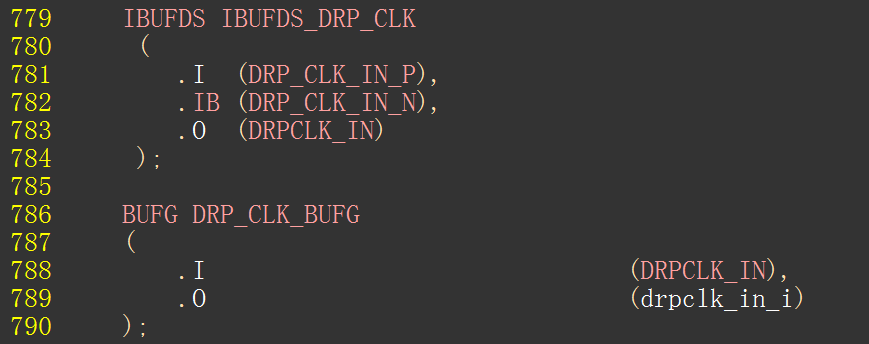

再来看下顶层文件中关于原语的使用:

IBUFDS是差分信号输入缓冲器,用来将差分信号变为单端信号。而BUFG是全局缓冲,其输出到达FPGA内部CLB IOB RAM的时钟延迟和抖动是最小的,从而使系统工作稳定。

最后,为保证最基本的通信功能,还需做三件事:

1. 去除gen和check逻辑块,并将用户数据端口开放到工程顶层;

2. 接收端用户侧例化数据重对齐模块保证接收正确;

3. 例化PLL产生100MHz时钟信号作为GTP子系统工作时钟;

7系列高速收发器总结 GTP IP核使用篇的更多相关文章

- 7 Series GTP IP核使用总结 IP核配置篇

FPGA内嵌收发器相当于以太网中的PHY芯片,但更灵活更高效,线速率也在随着FPGA芯片的发展升级.本文对7系列FPGA内部高速收发器GTP IP核的配置和使用做些简单的总结,以备后续回顾重用.本文是 ...

- xilinx IP核配置,一步一步验证Xilinx Serdes GTX最高8.0Gbps

版权声明:本文为博主原创文章,未经博主允许不得转载. https://blog.csdn.net/u010161493/article/details/77658599 目录(?)[+] 之前 ...

- Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟篇

xilinx的7系列FPGA根据不同的器件类型,集成了GTP.GTX.GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及最 ...

- 从Xilinx FFT IP核到OFDM

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109.关于 ...

- 【转载】xilinx 高速收发器Serdes深入研究

此篇文章深入浅出介绍了关于高速串行收发器的几个重要概念和注意事项,为方便知识点复习总结和后续查阅特此转载,原文标题及链接为:xilinx 高速收发器Serdes深入研究 - CSDN博客 http ...

- 如何将自己写的verilog模块封装成IP核

如何将自己写的verilog模块封装成IP核 (2014-11-21 14:53:29) 转载▼ 标签: 财经 分类: 我的东东 =======================第一篇========= ...

- Vivado使用技巧(二):封装自己设计的IP核

由 judyzhong 于 星期五, 09/08/2017 - 14:58 发表 概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原 ...

- Vivado使用技巧:封装自己设计的IP核

概述 Vivado在设计时可以感觉到一种趋势,它鼓励用IP核的方式进行设计.“IP Integrator”提供了原理图设计的方式,只需要在其中调用设计好的IP核连线.IP核一部分来自于Xilinx ...

- 基于Virtext6平台的GTX IP核基本设置说明

本工程基于以下条件使用: 板卡:DBF板v3.0 芯片型号:Virtex6 315T ISE版本:14.7 IP核版本: v6_gtxwizard : 1.12 一.IP核配置进行流程 第一页配置:线 ...

随机推荐

- Django学习日记04_模板_overview

通过Django中的模板,使得设计人员和网站管理有一个对接的接口,实现网页设计和逻辑的分离,因此,模板会处理大量的文本解析内容,django中内部使用了高效的引擎来完成模板解析. 模板设置 在使用模板 ...

- SQL SERVER 常用知识整理

以前写了一些关于sql的文章,包括一些转载的,这里做下整理,方便需要时候使用 一.基础运用 SQL 数据结构操作语句 SQL 时间处理 SQL 常见函数使用 CASE WHEN THEN 小结 二.优 ...

- Java 读取配置文件

1.读取XML文件使用dom4j-full.jar包的SAXReader解析: Document document=new SAXReader.reader("xml文路径/文件名xxx.x ...

- dubbo源码—service reference

service reference 在编写好服务之后,dubbo会将服务export出去,这个时候就可以编写consumer来调用这个服务了.dubbo作为一个rpc框架,使用者使用远程服务和使用本地 ...

- hadoop+hive+spark搭建(二)

上传hive软件包到任意节点 一.安装hive软件 解压缩hive软件包到/usr/local/hadoop/目录下 重命名hive文件夹 在/etc/profile文件中添加环境变量 export ...

- [Spark内核] 第35课:打通 Spark 系统运行内幕机制循环流程

本课主题 打通 Spark 系统运行内幕机制循环流程 引言 通过 DAGScheduelr 面向整个 Job,然后划分成不同的 Stage,Stage 是從后往前划分的,执行的时候是從前往后执行的,每 ...

- 强化学习之Sarsa (时间差分学习)

上篇文章讲到Q-learning, Sarsa与Q-learning的在决策上是完全相同的,不同之处在于学习的方式上 这次我们用openai gym的Taxi来做演示 Taxi是一个出租车的游戏,把顾 ...

- Updates were rejected because the remote contains work that you do(git报错解决方案)

Updates were rejected because the remote contains work that you do(git报错解决方案) 今天向GitHub远程仓库提交本地项目文件时 ...

- 利用TortoiseGit对Coding项目进行版本管理

Git配置: 1),首先去Git官网下载最新的Git,https://git-for-windows.github.io/ 2),下载对应的版本,然后一路next点击安装. Git与Coding联通 ...

- DAY3-“忙里偷闲”找你玩耍2018-1-11

接触Java第三天,嘿嘿,今天近代史期末考试,提前一小时交卷,回宿舍继续学习,中午去见女神姐姐了,每次见完女神姐姐都是满满地动力.这次女神姐姐告诉我们要好好规划自己的时间,早上花20分钟规划好一天的时 ...