FIFO IP核仿真

FIFO IP核仿真

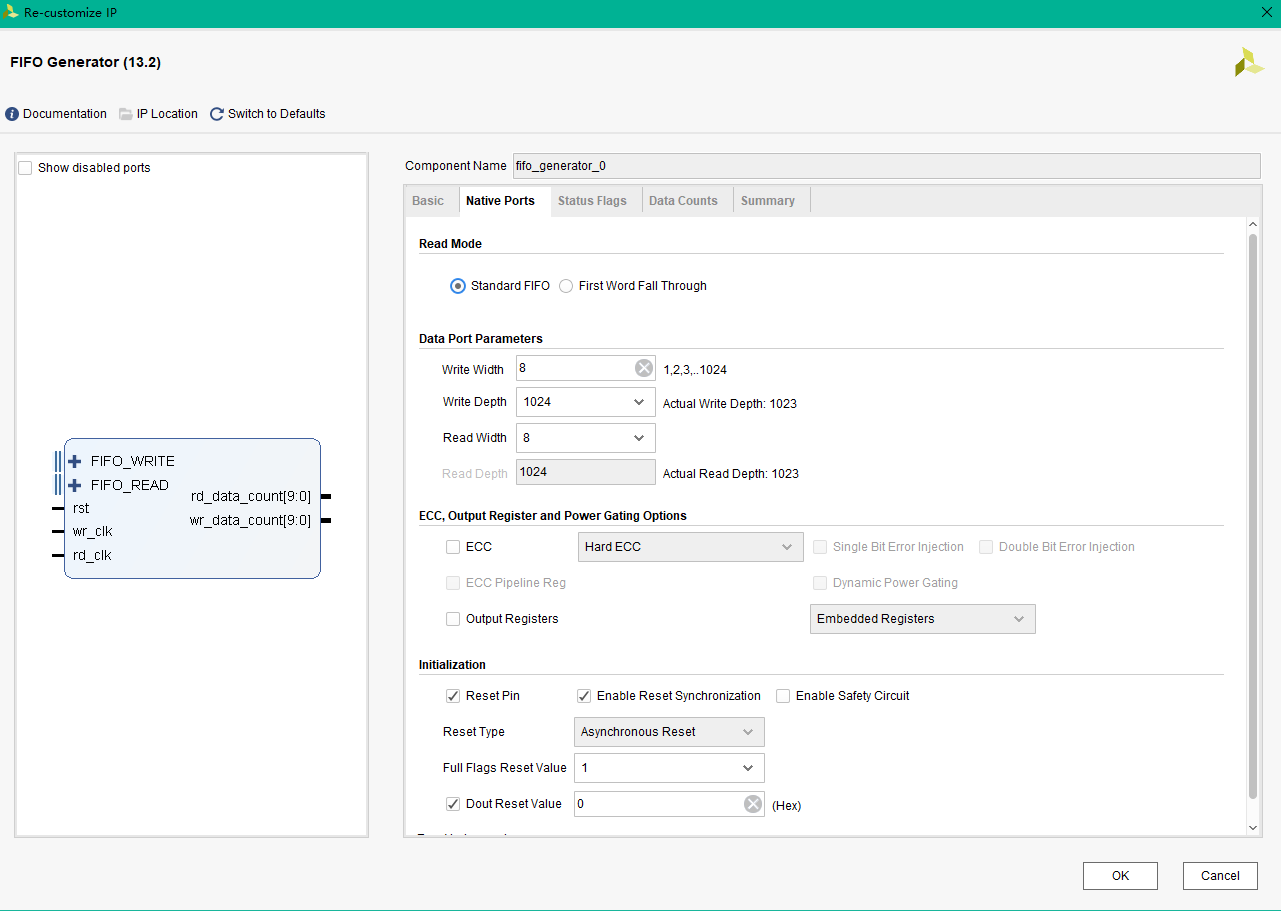

1.FIFO IP核配置

2.FIFO测试逻辑代码

首先往FIFO里面写入512个数据(FIFO深度的一半),然后再开始同时往FIFO里面写入,读出数据。FIFO读和写的时钟域不同,对于不同时钟域的信号应该进行区分,状态机也应该分开来写。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2017/10/23 16:11:32

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module top(

rst,

wr_clk,

rd_clk,

dout,

full,

empty,

rd_data_count,

wr_data_count

); //input

input rst;

input wr_clk;

input rd_clk; //output

output [:]dout;

output full;

output empty;

output [:]rd_data_count;

output [:]wr_data_count; //write state

reg [:]i;

reg read_start;

reg [:]din_r;

reg clear_fifo_full;

reg wr_en_r;

wire wr_en;

wire [:]din;

wire [:]wr_data_count;

wire full;

always@(posedge wr_clk)

begin

if(rst)

begin

wr_en_r <= 'b0;

i <= 'd0;

read_start <= 'b0;

clear_fifo_full <= 'b0;

din_r <= 'd0;

end

else

begin

case(i)

:

begin

if(!full) begin wr_en_r <= 'b1; i<=i+1'b1; end

else wr_en_r <= 'b0;

end

:

begin

if(wr_data_count =='d512) begin read_start <=1'b1; din_r <= din_r +'b1; i<=i+1'b1; end

else din_r <= din_r +'b1;

end

:

begin

if(full) begin clear_fifo_full <= 'b1; wr_en_r <= 1'b0; i<='d0; end

else din_r <= din_r +'b1;

end

endcase

end

end assign wr_en = wr_en_r;

assign din = din_r; //read state

reg rd_en_r;

reg [:]j;

reg clear_fifo_empty;

wire rd_en;

always@(posedge rd_clk)

begin

if(rst)

begin

rd_en_r <= 'b0;

j <= 'd0;

clear_fifo_empty <= 'b0;

end

else

begin

case(j)

:

begin

if(read_start & !empty) begin rd_en_r <= 'b1; j<=j+1'b1; end

else rd_en_r <= 'b0;

end

:

begin

if(empty) begin clear_fifo_empty <= 'b1; rd_en_r <= 1'b0; j<='d0; end

else rd_en_r <= 'b1;

end

endcase

end

end assign rd_en = rd_en_r; fifo_generator_0 U1 (

.rst(rst), // input wire rst

.wr_clk(wr_clk), // input wire wr_clk

.rd_clk(rd_clk), // input wire rd_clk

.din(din), // input wire [7 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [7 : 0] dout

.full(full), // output wire full

.empty(empty), // output wire empty

.rd_data_count(rd_data_count), // output wire [9 : 0] rd_data_count

.wr_data_count(wr_data_count) // output wire [9 : 0] wr_data_count

); endmodule

3.测试脚本

add_force {/top/rst} -radix hex { 0ns} { 150000ps}

add_force {/top/wr_clk} -radix hex { 0ns} { 50000ps} -repeat_every 100000ps

add_force {/top/rd_clk} -radix hex { 0ns} { 49500ps} -repeat_every 99000ps

4.仿真波形分析

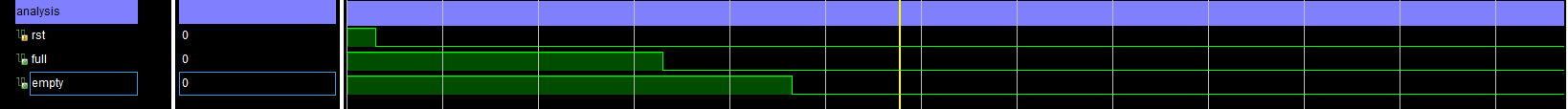

仿真波形图

对FIFO进行复位操作,开始full,empty都会拉高一段时间,然后才会恢复正常。

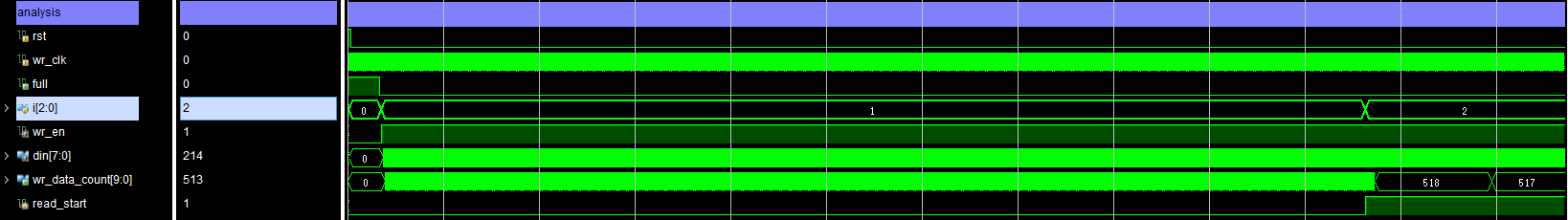

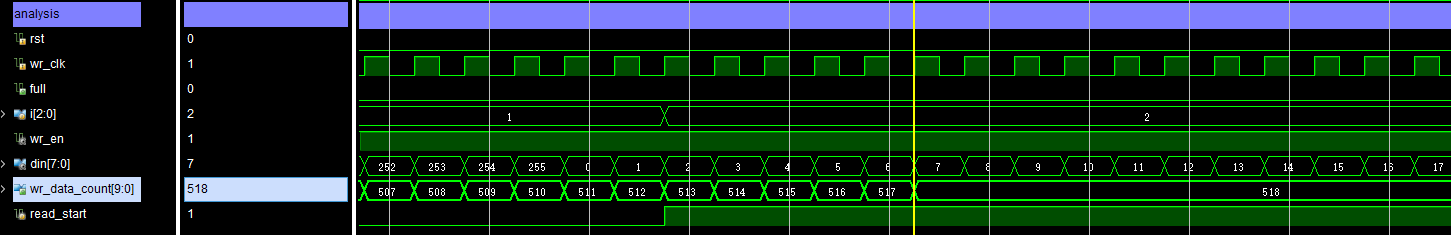

与写状态有关的信号分析

当full恢复正常后,写使能,同时状态机跳转。

当写入512个数据后(wr_data_count == 512),read_start信号开始拉高,FIFO开始读出数据,同时状态机也在此刻跳转,下一个状态再写数据的同时,也在监测FIFO是否已经被写满。

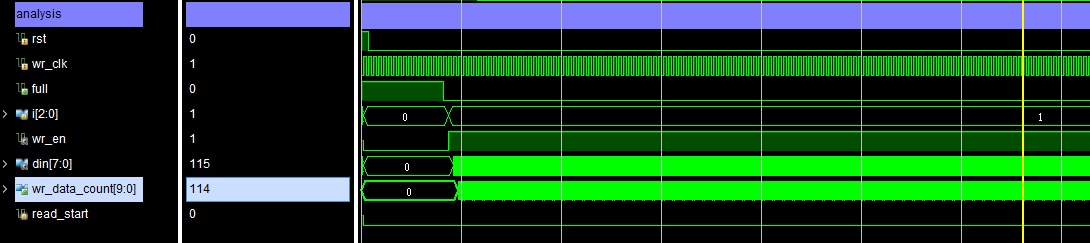

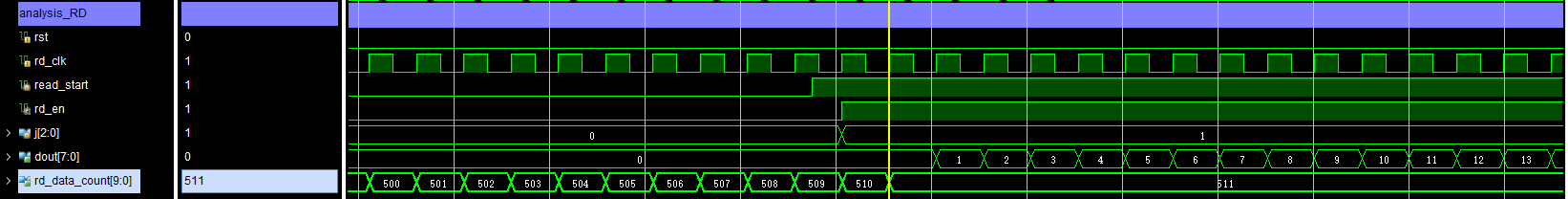

下面来看FIFO读数据端的仿真波形

当read_start信号拉高时,re_en信号开始拉高,FIFO才开始从dout端口读出数据,可以看到,刚开读出的数据为FIFO din端口最先写入的数据。从rd_data_count端口可以看到,此时FIFO里面已经有500多个数据可以读。

结论:仿真结果与预期相符。

FIFO IP核仿真的更多相关文章

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- Altera FIFO IP核时序说明

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- modelsim-altera IP核仿真

modelsim 仿真fifo时出现 Instantiation of 'scfifo' failed. The design unit was not found. 2012-07-21 13:27 ...

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- Altera三速以太网IP核快速仿真与使用(上篇)

对于比较高级的ip核,altera一般都会提供仿真案例,网上有关于这个IP核的各种仿真方法,但都比较繁琐,前几日,朋友跟我分享了一个比较快速高效的仿真方法,这个方法也是他摸索折腾了一段时间才总结出来的 ...

- 用Modelsim SE 直接仿真 Altera(Intel PSG) IP核 需要注意的问题

如果我们直接用Modelsim SE仿真 Altera IP核,首先会进入Quartus II目录下找到IP核对应的仿真库源文件,然后在Modelsim SE中进行编译,添加到Modelsim SE的 ...

- IP核——FIFO

一.Quartus 1.打开Quartus ii,点击Tools---MegaWizard Plug-In Manager 2.弹出创建页面,选择Creat a new custom megafunc ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

随机推荐

- 部署php的正确姿势

1. 更新源 apt-get update 2.安装apache apt-get install apache2 ubuntu下apache2虚拟主机配置 cd /etc/apache2/sites- ...

- 解决 canvas 将图片转为base64报错

var canvas=document.getElementById("canvas"),//获取canvas ctx = canvas.getContext("2d&q ...

- STP实验(指定特定交换机为根桥)

实验要求:将三层交换机设置为根桥交换机,并查看 拓扑如下: 涉及内容有: 1.根桥交换机的选举方式 2.生成树修改优先级成为根桥交换机 3.生成树直接指定根桥交换机 根桥交换机是根据优先级和MAC地址 ...

- 基于CART的回归和分类任务

CART 是 classification and regression tree 的缩写,即分类与回归树. 博主之前学习的时候有用过决策树来做预测的小例子:机器学习之决策树预测--泰坦尼克号乘客数据 ...

- 如何更改Apache的根目录指向

更改Apache的默认网站根目录地址方法如下: 0,先找到主目录下的apache文件,然后进行下面操作 1.找到 DocumentRoot “X:/Apache/htdocs” 将“X:/Apache ...

- 当爬虫遇到js加密

当爬虫遇到js加密 我们在做python爬虫的时候经常会遇到许多的反爬措施,js加密就是其中一种. 破解js加密的方法也有很多种: 1.直接驱动浏览器抓取数据,无视js加密. 2.找到本地加密的js代 ...

- hdu4847 Wow! Such Doge! KMP

Chen, Adrian (November 7, 2013). “Doge Is An Ac- tually Good Internet Meme. Wow.”. Gawker. Retrieved ...

- linux----磁盘介绍

1.磁盘简图: 2.常见分区 mbr:主引导区,共512byte 扩展分区 逻辑分区

- JAVA 实用插件

一.alibaba开发规约插件 https://p3c.alibaba.com/plugin/eclipse/update 下载地址 alibaba是个优秀的公司,这个插件能很好的规范代码,推荐给大家 ...

- hotel管理

PS:这个界面