data hazard in CPU pipeline

1, background info

5 stages in CPU pipeline: IF, ID, EX, MM, WB

IF – Instruction Fetch

ID – Instruction Decode

EX – Execute

MM – Memory

WB – Write Back

2, what is data hazard and how does it happen

Data hazards occur when instructions that exhibit data dependency modify data in different stages of a pipeline.

For example, we write a register and then read it. The write and read operations are dependent; they are related by the same register.

In a pipeline, if read happens before the write can finish, it’s very likely that it would not read back a correct value.

In this case, data hazard happens.

It’s not difficult to imagine that any 2 operations involving write may cause data hazard.

We can categorize data hazard into 3 kinds:

(1) read after write (RAW);

(2) write after write (WAW);

(3) write after read (WAR);

3, how to prevent data hazard

(1) pipeline bubbling

That is, stall the pipeline until hazard is resolved.

add r1, r2, r3

add r4, r1, r5 Cycles----->

________________________ Instructions

|_IF_|_ID_|_EX_|_MM_|_WB_|______________ add r1, r2, r3

|_IF_|_x_x_x_x_|_ID_|_EX_|_MM_|_WB_| add r4, r1, r5

stall cycles

Usually, NOP operationg is inserted during stall time.

As instructions are fetched, control logic determines whether a hazard could/will occur. If this is true, then the control logic insert NOPs into the pipeline.

If the number of NOPs equals the number of stages in the pipeline, the processor has been cleared of all instructions and can proceed free from hazards.

(2) out-of-order execution

This would be introduced heavily later.

(3) operand forwarding/bypass

See below examle.

Instruction 0: Register 1 = 6Instruction 1: Register 1 = 3Instruction 2: Register 2 = Register 1 + 7 = 10

Instruction 2 would need to use Register 1. If Instruction 2 is executed before Instruction 1 is finished, it may get a wrong result.

However, we can see that:

a) the output of Instruction 1 (which is 3) can be used by subsequent instructions before the value 3 is committed to/stored in Register 1.

b) there is no wait to commit/store the output of Instruction 1 in Register 1 (in this example, the output is 3) before making that output available to the subsequent instruction (in this case, Instruction 2).

So it can be done that:

Instruction 2 uses the correct (the more recent) value of Register 1: the commit/store was made immediately and not pipelined.

This is forwarding/bypass.

4, how does forwarding/bypss work

With forwarding enabled, the Instruction Decode/Execution (ID/EX) stage of the pipeline now has two inputs: the value read from the register specified (in this example, the value 6 from Register 1), and the new value of Register 1 (in this example, this value is 3) which is sent from the next stage Instruction Execute/Memory Access(EX/MM). Added control logic is used to determine which input to use.

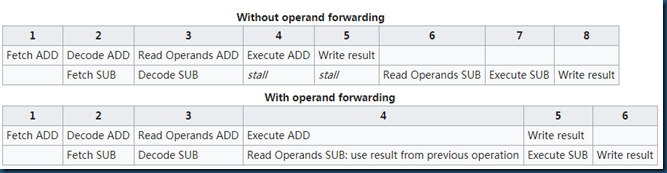

A forwarding vs. no forwarding example as followed:

ADD A B C #A=B+C

SUB D C A #D=C-A

data hazard in CPU pipeline的更多相关文章

- [Machine Learning with Python] Data Preparation through Transformation Pipeline

In the former article "Data Preparation by Pandas and Scikit-Learn", we discussed about a ...

- antidependence and data hazard

See below example. ADDD F6, F0, F8 SUBD F8, F10, F14 Some article would say that “ There’s an ant ...

- SSIS Data Flow 的 Execution Tree 和 Data Pipeline

一,Execution Tree 执行树是数据流组件(转换和适配器)基于同步关系所建立的逻辑分组,每一个分组都是一个执行树的开始和结束,也可以将执行树理解为一个缓冲区的开始和结束,即缓冲区的整个生命周 ...

- verilog实现16位五级流水线的CPU带Hazard冲突处理

verilog实现16位五级流水线的CPU带Hazard冲突处理 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4292869.html所增加的Hazard处 ...

- [DE] Pipeline for Data Engineering

How to build an ML pipeline for Data Science 垃圾信息分类 Ref:Develop a NLP Model in Python & Deploy I ...

- 以Excel 作为Data Source,将data导入db

将Excel作为数据源,将数据导入db,是SSIS的一个简单的应用,下图是示例Excel,数据列是code和name 第一部分,Excel中的数据类型是数值类型 1,使用SSDT创建一个package ...

- One EEG preprocessing pipeline - EEG-fMRI paradigm

The preprocessing pipeline of EEG data from EEG-fMRI paradigm differs from that of regular EEG data, ...

- Java底层实现 - CPU术语

1.内存屏障(memory barriers)是一组处理器指令,用于实现对内存操作的顺序限制 2.缓冲行(cache line)CPU高速缓存中可以分配的最小存储单位.处理器填写缓存行时 会加载整个缓 ...

- CPU和GPU性能对比

计算20000次10000点的fft,分别使用CPU和GPU,得 the running time of cpu is : 2.3696s the running time of gpu is : 0 ...

随机推荐

- class13and14and15_登录窗口

最终的运行效果图(程序见序号6.2): #!/usr/bin/env python# -*- coding:utf-8 -*-# ----------------------------------- ...

- PAT_A1043#Is It a Binary Search Tree

Source: PAT A1043 Is It a Binary Search Tree (25 分) Description: A Binary Search Tree (BST) is recur ...

- shell 一些命令(转)

shell 一些命令(转) https://www.cnblogs.com/amei0/p/8041989.html 参考文档 http://man.linuxde.net/ 一.awk 求和 awk ...

- jmeter 实战

JMeter 接口测试 什么是接口测试 概念 内部接口 方法与方法之间的交互 模块与模块之间的交互 一种调用对外包装的接口 Web接口分类 web接口分类:https.http.webService ...

- EXE 和 SYS 信息交互

操了,分发函数少发一个,让我白调了两个多小时.

- netty UnpooledHeapByteBuf 源码分析

UnpooledHeapByteBuf 是基于堆内存进行内存分配的字节缓冲区,没有基于对象池技术实现,这意味着每次I/O的读写都会创建一个新的UnpooledHeapByteBuf,频繁进行大块内存的 ...

- 2019-8-31-dotnet-非泛型-类型-System.Collections.IEnumerable-不能与类型实参一起使用

title author date CreateTime categories dotnet 非泛型 类型 System.Collections.IEnumerable 不能与类型实参一起使用 lin ...

- 和Excel函数date同样功能的VBA函数DateSerial用法

Sub 日期别()On Error Resume Nextlastrow = Sheets("运营日报").Range("a1048576").End(xlUp ...

- Android studio 添加引用Module项目 与 设置Module项目的Libs的Jar在主项目里使用

前言 添加引用Module项目 设置Module项目的Libs的Jar在主项目里使用 1.在项目里添加libs包,并且加入jar 2.设置这个module项目的build.gradle depende ...

- [笔记]Laravel TDD 胡乱记录

TDD: 测试驱动开发(Test-Driven Development),TDD的原理是在开发功能代码之前,先编写单元测试用例代码,测试代码确定需要编写什么产品代码. -- 载自TDD百度百科 参考 ...