PCB板信号完整性分析的操作步骤及设置方法

- 电路中被测试的网络,必须包含IC的一个信号输出脚,这个输出信号作为激励这个网络的信号源。如果一个网络只有R、L、C等无源器件,没有晶体管、IC等有源器件,那么这个无源网络,就不能进行信号完整性分析。也就是说:必须设定被测试网络的激励源。

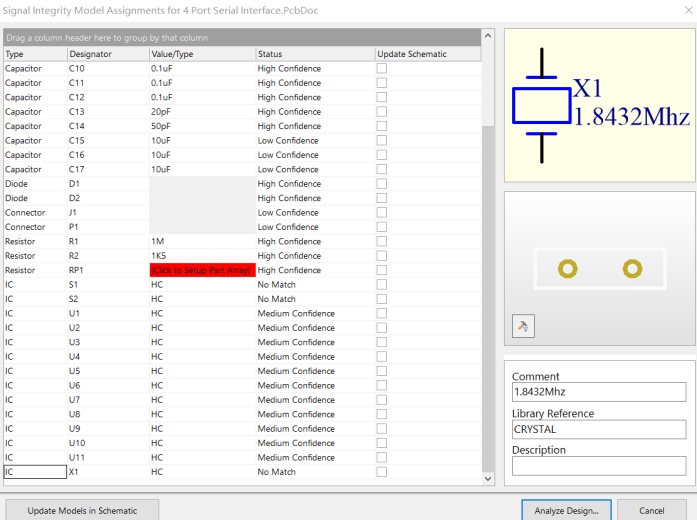

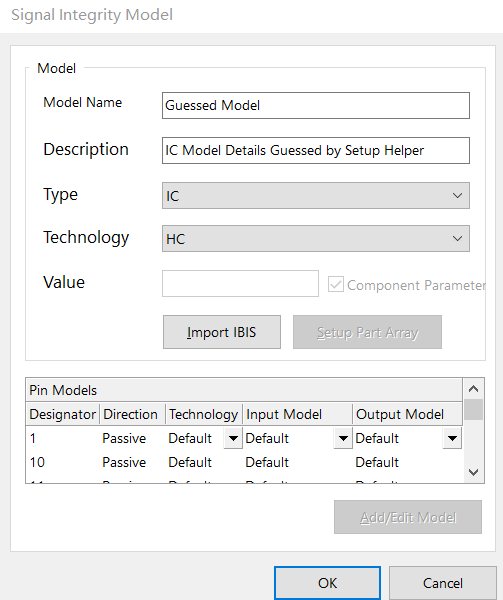

- 在绘制电路原理图、PCB板图时,绘图使用的零件库应当使用集成零件库,集成零件库里面的零件包含了电路原理图符号、封装符号、仿真模型、信号完整性模型。如果零件库里的零件不包含完整性模型,就必须登录零件生产商的官网,下载信号完整性模型,或从其他文件找到模型。然后再加载到工程文件里面来。也可以在原理图中调整模型。

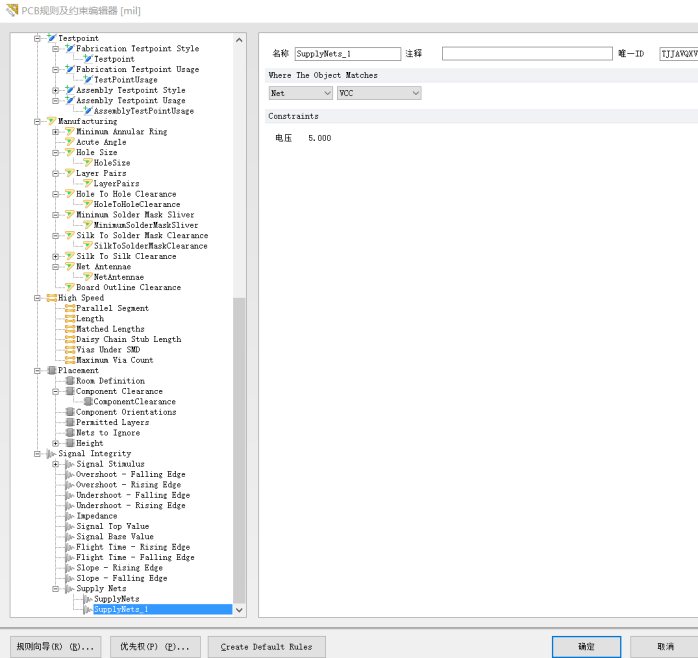

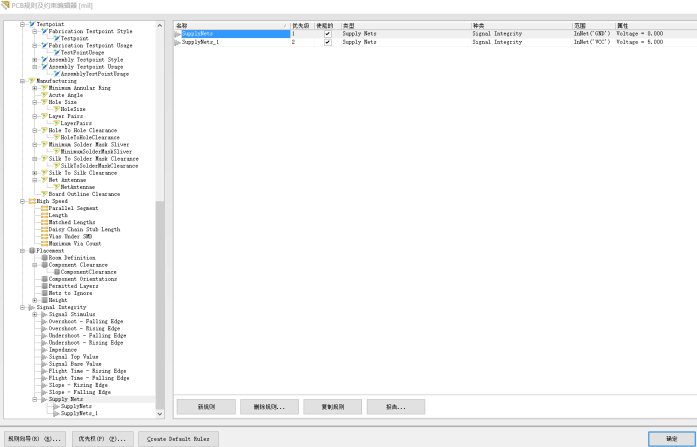

- 设定电路原理图中的电源网络电压值(如3.3V\5V\12V等等)、把电路图中电源的地网络,设定为0V。

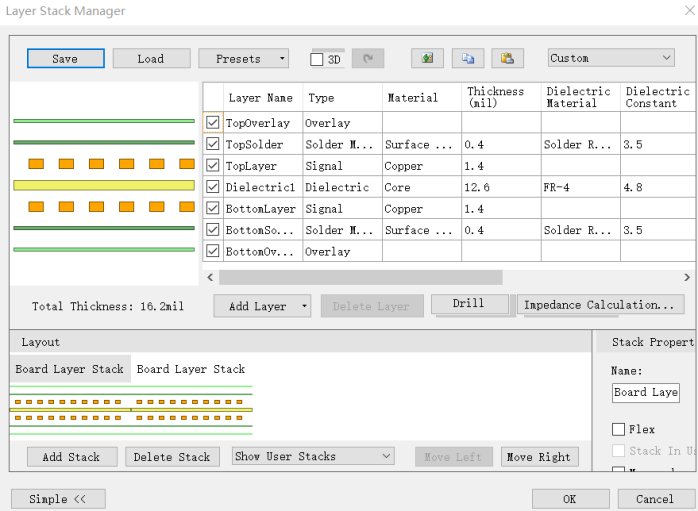

- 设定PCB板的PCB板层堆叠:单击design-------layer stack manager。一般采用系统默认值即可。

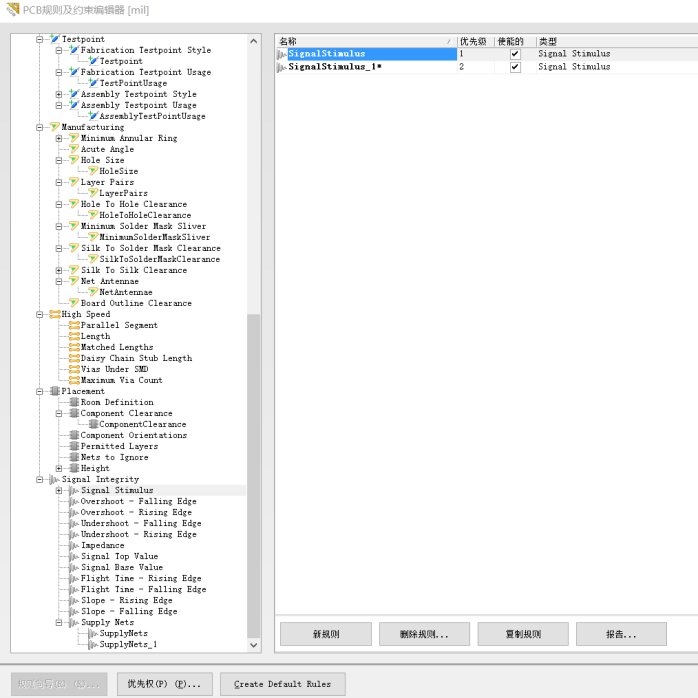

- 设置电压和地网络:在下图的左下角,单击:supply net,选择new rule.

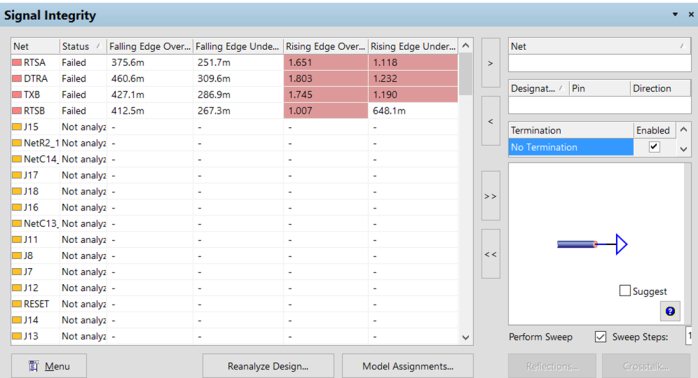

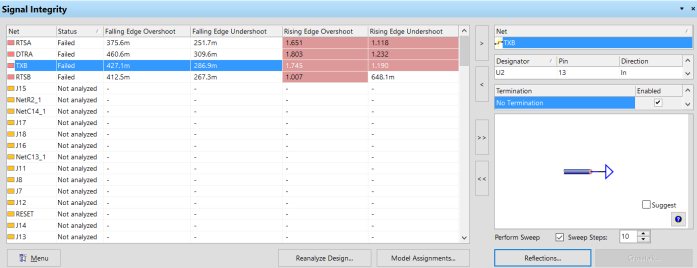

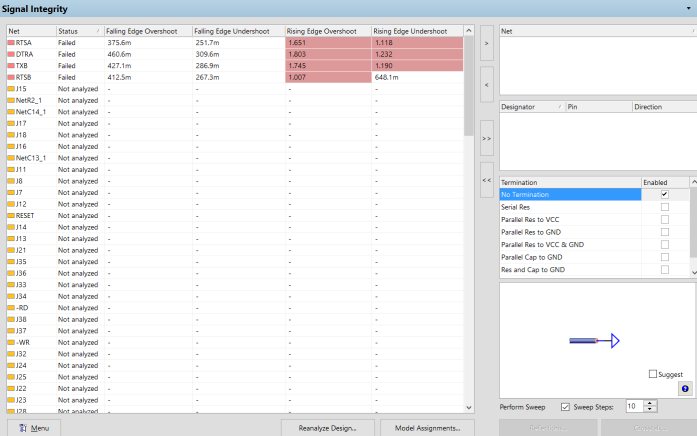

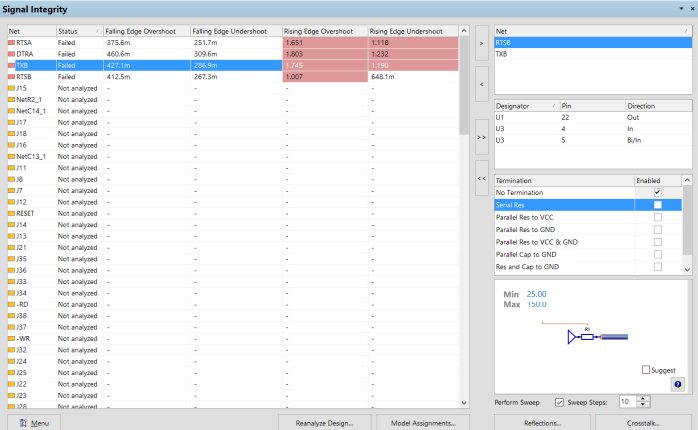

- 选择tools-----signal integrity------弹出一下对话框:

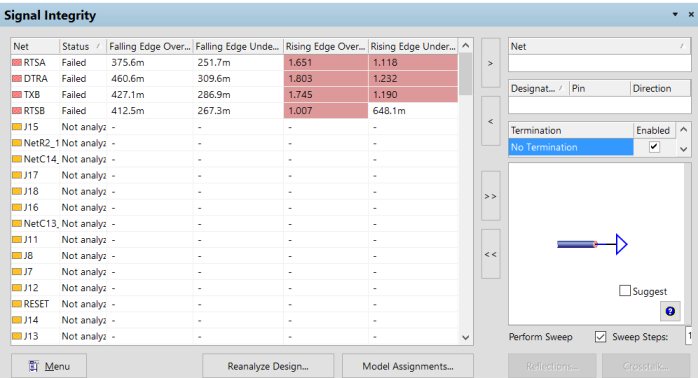

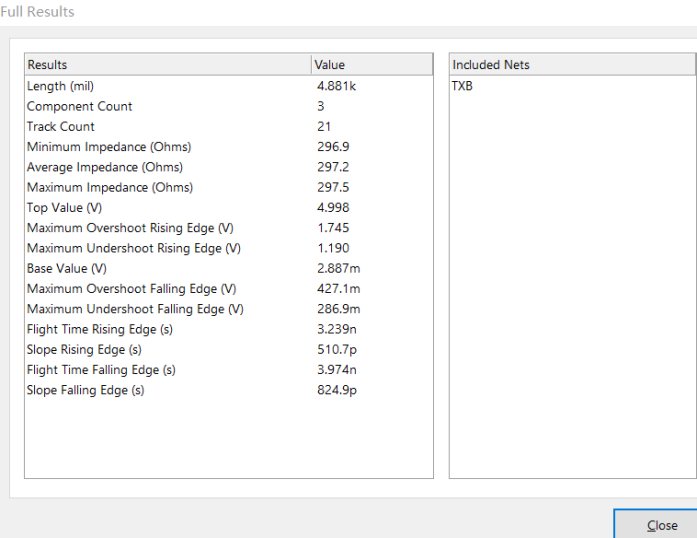

- 怎样查看上面网络表中某一个网络的完整性分析结果:右键单击上表中第三个网络:TXB-------在下拉菜单中选择details细节--------弹出下图:full result(该网络分析的详细结果)。

- 查看网络输出端的反射波形:

PCB板信号完整性分析的操作步骤及设置方法的更多相关文章

- PCB设计与信号完整性

之前在设计板卡时,只是听过相关的概念,但是未真正去研究关于SI相关的知识.将之前看过的一些资料整理如下: (1)信号完整性分析 与SI有关的因素:反射,串扰,辐射.反射是由于传输路径上的阻抗不匹配导致 ...

- Altium Designer PCB双面板制作打印操作步骤

Altium Designer PCB双面板制作打印操作步骤百度知道:http://jingyan.baidu.com/article/335530da83441c19cb41c3db.html?st ...

- 基于Python项目的Redis缓存消耗内存数据简单分析(附详细操作步骤)

目录 1 准备工作 2 具体实施 1 准备工作 什么是Redis? Redis:一个高性能的key-value数据库.支持数据的持久化,可以将内存中的数据保存在磁盘中,重启的时候可以再次加载进行使 ...

- PCB MS SERVER 数据导出与导入操作步骤----使用第3方工具

工作每天都与数据库打交道,经常会遇到一些需要将数据库中的数据导出来或将数据导入到数据库 而用微软数据库客户端自带的功能操作步骤好麻烦的,用过的大家都会有相同的感受吧. 微软客户端不好之处整理:这里吐槽 ...

- RK3399/NanoPC-T4开发板使用/sys/class/gpio操作外接GPIO设备-【申嵌视频-RK3399篇】

实验2:RK3399/NanoPC-T4开发板使用/sys/class/gpio操作外接GPIO设备,比如外接一个LED模块,通过GPIO1_A0管脚 1 介绍 LED模块 Matrix-LE ...

- PCB板可靠性测试方法择要

在电子设备中PCB板是所有电子设备的核心,其的可靠性程度会直接影响了产品的耐用性和寿命.因此在我们实验室(上海摩尔实验室)的实际工作中遇到了越来越多的针对PCB板的可靠性的测试要求,现根据一些企业的内 ...

- CH7511|LT7211|PS8625替代方案 CS5211 设计EDP转LVDS优势方案原理图+PCB板设计

CH7511|LT7211|PS8625这三款都是专门用于设计EDP转LVDS转接板或者屏转换方案板,CH7511.LT7211.PS8625目前这几款都是出于缺货状态,台湾瑞奇达Capstone 新 ...

- EMC信号完整性落地实测1---走出玄学

EMC信号完整性落地实测1---走出玄学 无论我们从51单片机,STM32电路,运放,传感器,ADC采集还是可控硅晶闸管等等电源电路跨入到电子工程师的行业,我们通常会长时间处于低频的电子电路设计调试阶 ...

- ArcGIS生成根据点图层生成等值面并减小栅格锯齿的操作步骤

一.打开ArcMAP并加载上相应的点图层和边界面图层 二.ArcToolbox--Spatial Analyst工具--差值分析--克里金法(根据不同的情况选择不同的算法,这次的处理实际上使用的是样条 ...

随机推荐

- linux 下core文件生成、路径、格式设置及调试

core文件生成及调试1 代码 #include<stdio.h> int main() { int *p = NULL; *p = 0; return 0; } 2 在当前shell执行 ...

- mvn-dependencies-vs-dependencyManagement

dependencyManagement里只是声明依赖,并不实现引入,因此子项目需要显式的声明需要用的依赖. dependencies 相对于dependencyManagement,所有声明在dep ...

- STL源码之traits编程技法

摘要 主要讨论如何获取迭代器相应型别.使用迭代器时,很可能用到其型别,若需要声明某个迭代器所指对象的型别的变量,该如何解决.方法如下: function template的参数推导机制 例如: tem ...

- Spring security oauth2 password flow

Spring security oauth2 包含以下两个endpoint来实现Authorization Server: AuthorizationEndpoint: 授权请求访问端点, 默认url ...

- Java学习之旅(二):生病的狗2(java例化)

废话不多说,直接上肝货,可运行. 代码简陋,逻辑关系可能还不是很严谨,欢迎交流. public class Owner { //属性部分 //狗主人肯定有一条狗,这条狗可以被别的主人检查,所以设置为p ...

- 全能中间件v19.5.7 正式版发布

v19.5.7 更新=========================1.新增 支持更多微信公众号API.2.优化 AccessToken 刷新机制.3.修复 微信公众号“消息加解密方式”为“安全模式 ...

- Vue框架(二)——Vue指令(v-once指令、v-cloak指令、条件指令、v-pre指令、循环指令)、todolist案例、Vue实例(计算、监听)、组件、组件数据交互

Vue指令 1.v-once指令 单独使用,限制的标签内容一旦赋值,便不可被动更改(如果是输入框,可以主动修改) <!DOCTYPE html> <html lang=" ...

- Function Evaluation

Author: Leisureeen Time Limit: 100ms Memory Limit: 65535KB Code Size Limit: 16 KB 64-bit integer IO ...

- golang 之文件操作

文件操作要理解一切皆文件. Go 在 os 中提供了文件的基本操作,包括通常意义的打开.创建.读写等操作,除此以外为了追求便捷以及性能上,Go 还在 io/ioutil 以及 bufio 提供一些其他 ...

- chrome Network 过滤和高级过滤

转自:https://blog.csdn.net/tengdazhang770960436/article/details/90644523