对FPGA的时钟资源理解(更新中)

7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟、内部时钟进行处理,生成需要的低抖动时钟。PLL是MMCM的功能子集,也是基于MMCM的。其中MMCM包含的额外特性有:

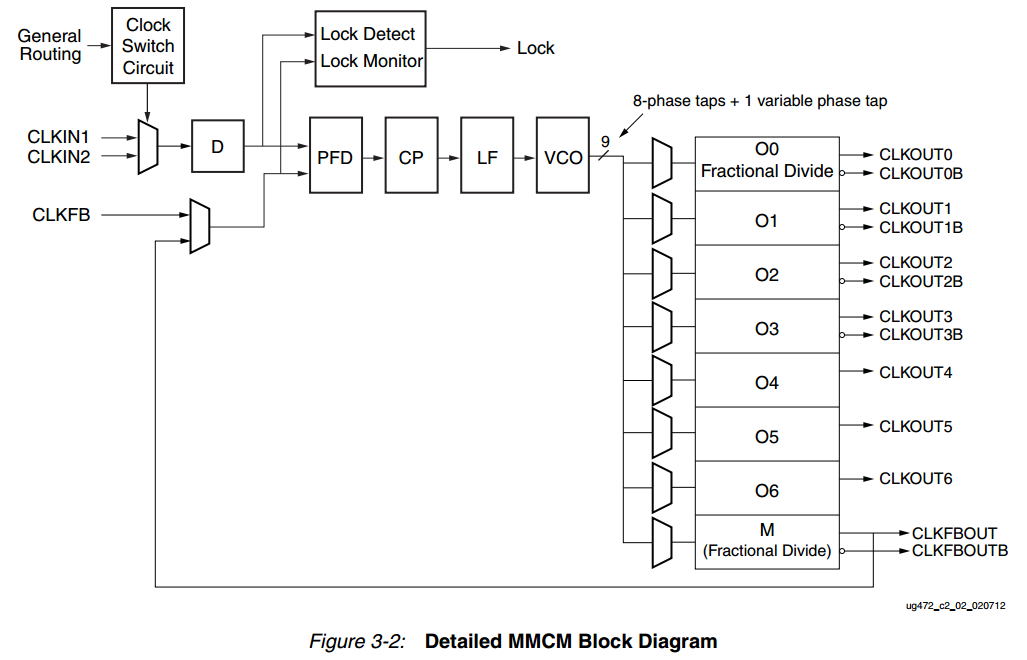

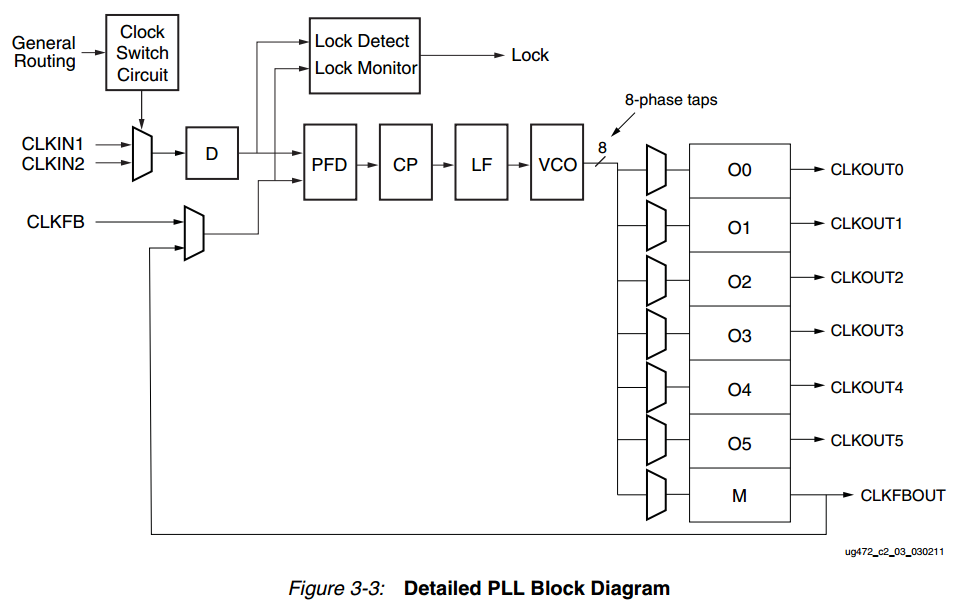

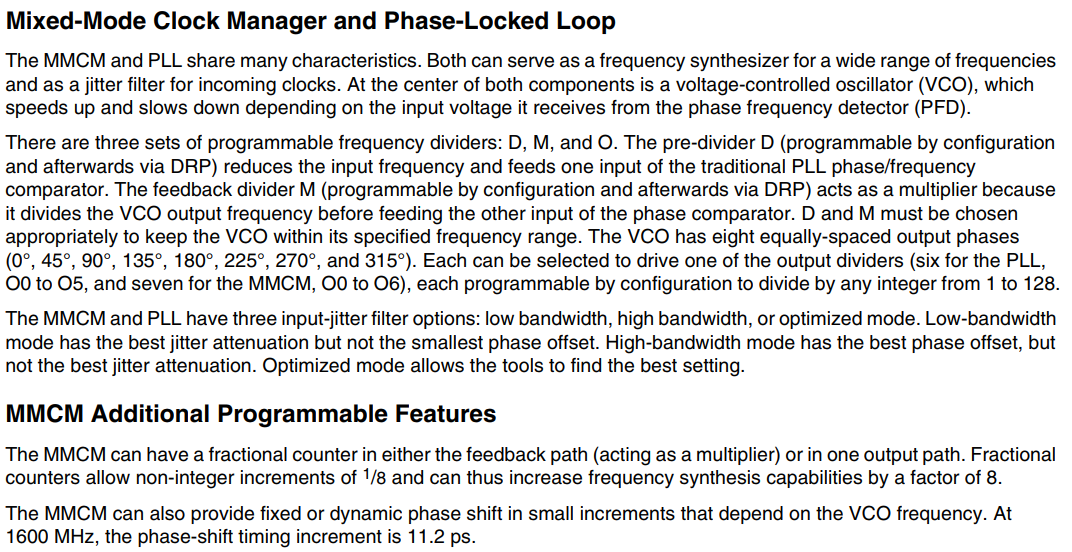

输入多路复用器从IBUFG,BUFG,BUFR,BUFH,GTs(CLKIN only)或互连(不推荐)中选择其一 作为参考和反馈时钟,每个时钟输入都经过一个可编程的计数器(D)。相位频率检测器(PFD)比较输入(参考)时钟和反馈时钟的上升边缘的相位和频率。如果最小的高/低脉冲是可保持的,则任务周期是辅助的。PFD用于生成与两个时钟之间的相位和频率成比例的信号。这个信号用于驱动增压泵(CP)和循环过滤器(LF)来为VCO生成一个参考电压。PFD会产生一个向上或向下的信号给充电泵和环形滤波器,以确定VCO是否应该以更高或更低的频率运行。当VCO以过高的频率运行时,PFD会激活一个向下的信号,导致控制电压降低,降低VCO的工作频率。当VCO以极低的频率运行时,向上的信号会增加电压。VCO生产八个输出阶段和一个可变阶段,用于精细阶段的转换。每个输出阶段都可以被选择作为输出计数器的参考时钟(图3-2和图3-3)。每个计数器可以独立地为给定的客户设计进行编程。还提供了一个特殊的计数器M。这个计数器控制MMCM和PLL的反馈时钟,允许合成宽范围的频率。除了整数除法输出计数器之外,MMCMs还为CLKOUT0和CLKBOUT0添加了一个分数计数器。

source: 可以选择单端输入、差分输入、全局buffer、no buffer四种;

Clock Management

Some of the key highlights of the clock management architecture include:

• High-speed buffers and routing for low-skew clock distribution

• Frequency synthesis and phase shifting

• Low-jitter clock generation and jitter filtering

Each 7 series FPGA has up to 24 clock management tiles (CMTs), each consisting of one mixed-mode clock manager (MMCM) and one phase-locked loop (PLL).

参考:

UG472-7 Series FPGAs Clocking Resources.pdf

DS180-7 Series FPGAs Data Sheet: Overview.pdf

对FPGA的时钟资源理解(更新中)的更多相关文章

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- C#图书资源【更新中...】喜欢的就转存吧

百度分享暂时取消了,需要的朋友可以直接关注我,我发给你. 重点篇 1.C#与.NET3.5高级程序设计 2.C#与.NET3.5高级程序设计.rar 3.Effective_C#_中文版_改善C#程序 ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- Spartan6系列之Spartan6系列之芯片时钟资源深入详解

1. 时钟资源概述 时钟设施提供了一系列的低电容.低抖动的互联线,这些互联线非常适合于传输高频信号.最大量减小时钟抖动.这些连线资源可以和DCM.PLL等实现连接. 每一种Spartan-6芯片提 ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

随机推荐

- 机器学习基石(台湾大学 林轩田),Lecture 2: Learning to Answer Yes/No

上一节我们跟大家介绍了一个具体的机器学习的问题,以及它的内容的设定,我们今天要继续下去做什么呢?我们今天要教大家说到底我们怎么样可以有一个机器学习的演算法来解决我们上一次提到的,判断银行要不要给顾客信 ...

- 使用AutoCloseable 实现自动关闭资源

一.认识AutoCloseable AutoCloseable接口位于java.lang包下,从JDK1.7开始引入. 1.在1.7之前,我们通过try{} finally{} 在finally中释放 ...

- Django 的 orm 查询

一.模型关系表 1. 一对一 Author-AuthorDetail 关联字段可以在任意表下,但必须唯一约束.(unique约束) ad_id(unique约束) ad = models.oneToO ...

- 2.4 UML类图

类图定义 类class的定义 具有相同属性.操作.方法.关系或者行为的一组对象的描述符 类是真实世界事物的抽象 问题领域的类:在对系统建模时,将会涉及到如何识别业务系统中的事物,这些事物构 成了整个业 ...

- python基础之正则表达式 re模块

内容梗概: 1. 正则表达式 2. re模块的使⽤ 3. 一堆练习正则表达式是对字符串串操作的一种逻辑公式. 我们一般使用正则表达式对字符串进行匹配和过滤.使用正则的优缺点: 优点: 灵活,功能性强, ...

- LCS(最长公共子序列)问题

例题见挑战程序设计竞赛P56 解释:子序列是从原序列中按顺序(可以跳着)抽取出来的,序列是不连续的,这是其和子串最大的区别: 我们可以定义dp数组为dp[i][j],表示的是s1-si和t1-ti对应 ...

- Python mongoDB读取

class db_class(): def __init__(self): mongo_DB='test1' self.mongo_TABEL='test' client=pymongo.MongoC ...

- bat语法需要注意的地方

if else 格式 if exist C:\Python27 ::空格 ( ::(与if在同一行 ...

- DOM与document的区别

DOM: DOM 全称是 Document Object Model,也就是文档对象模型. DOM 就是针对 HTML 和 XML 提供的一个API.什么意思?就是说为了能以编程的方法操作这个 HTM ...

- js操作字符串的常用方法

使用 substring()或者slice() 函数:split() 功能:使用一个指定的分隔符把一个字符串分割存储到数组 例子: str=”jpg|bmp|gif|ico|png”; arr=the ...