FPGA芯片结构介绍及工作原理解析

FPGA工作原理与简介

如前所述,FPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA采用Flash或者熔丝与反熔丝工艺的查找表结构。通过烧写文件改变查找表内容的方法来实现对FPGA的重复配置。

根据数字电路的基本知识可以知道,对于一个n输入的逻辑运算,不管是与或非运算还是异或运算等等,多只可能存在2n种结果。所以如果事先将相应的结果存放于一个存贮单元,就相当于实现了与非门电路的功能。FPGA的原理也是如此,它通过烧写文件去配置查找表的内容,从而在相同的电路情况下实现了不同的逻辑功能。

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的 的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

下面给出一个4与门电路的例子来说明LUT实现逻辑功能的原理。

例1-1:给出一个使用LUT实现4输入与门电路的真值表。

表1-1 4输入与门的真值表

从中可以看到,LUT具有和逻辑电路相同的功能。实际上,LUT具有更快的执行速度和更大的规模。

由于基于LUT的FPGA具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,所以适用于高速、高密度的高端数字逻辑电路设计领域。其组成部分主要有可编程输入/输出单元、基本可编程逻辑单元、内嵌SRAM、丰富的布线资源、底层嵌入功能单元、内嵌专用单元等,主要设计和生产厂家有Xilinx、Altera、LatTIce、Actel、Atmel和QuickLogic等公司,其中的是Xilinx、Altera、LatTIce三家。

如前所述,FPGA是由存放在片内的RAM来设置其工作状态的,因此工作时需要对片内RAM进行编程。用户可根据不同的配置模式,采用不同的编程方式。FPGA有如下几种配置模式:

并行模式:并行PROM、Flash配置FPGA;

主从模式:一片PROM配置多片FPGA;

串行模式:串行PROM配置FPGA;

外设模式:将FPGA作为微处理器的外设,由微处理器对其编程。

目前,FPGA市场占有率的两大公司Xilinx和Altera生产的FPGA都是基于SRAM工艺的,需要在使用时外接一个片外存储器以保存程序。上电时,FPGA将外部存储器中的数据读入片内RAM,完成配置后,进入工作状态;掉电后FPGA恢复为白片,内部逻辑消失。这样FPGA不仅能反复使用,还无需专门的FPGA编程器,只需通用的EPROM、PROM编程器即可。Actel、QuickLogic等公司还提供反熔丝技术的FPGA,只能,具有抗辐射、耐高低温、低功耗和速度快等优点,在军品和航空航天领域中应用较多,但这种FPGA不能重复擦写,开发初期比较麻烦,费用也比较昂贵。LatTIce是ISP技术的发明者,在小规模PLD应用上有一定的特色。早期的Xilinx产品一般不涉及军品和宇航级市场,但目前已经有Q Pro-R等多款产品进入该类领域。

1.2.2 FPGA芯片结构

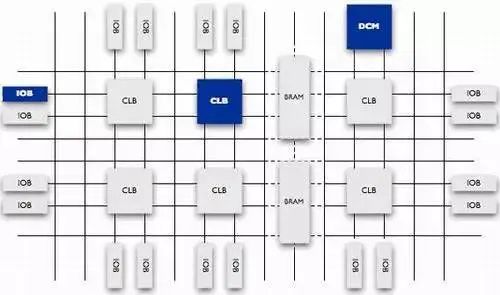

目前主流的FPGA仍是基于查找表技术的,已经远远超出了先前版本的基本性能,并且整合了常用功能(如RAM、时钟管理和DSP)的硬核(ASIC型)模块。如图1-1所示(注:图1-1只是一个示意图,实际上每一个系列的FPGA都有其相应的内部结构),FPGA芯片主要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

图1-1 FPGA芯片的内部结构

每个模块的功能如下:

1. 可编程输入输出单元(IOB)

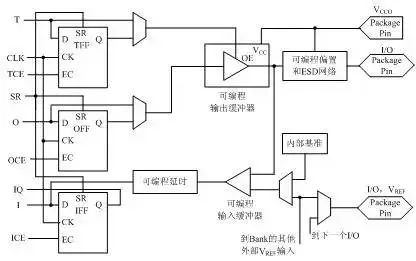

可编程输入/输出单元简称I/O单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求,其示意结构如图1-2所示。FPGA内的I/O按组分类,每组都能够独立地支持不同的I/O标准。通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。目前,I/O口的频率也越来越高,一些高端的FPGA通过DDR寄存器技术可以支持高达2Gbps的数据速率。

图1-2 典型的IOB内部结构示意图

外部输入信号可以通过IOB模块的存储单元输入到FPGA的内部,也可以直接输入FPGA 内部。当外部输入信号经过IOB模块的存储单元输入到FPGA内部时,其保持时间(Hold TIme)的要求可以降低,通常默认为0。

为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。只有相同电气标准的端口才能连接在一起,VCCO电压相同是接口标准的基本条件。

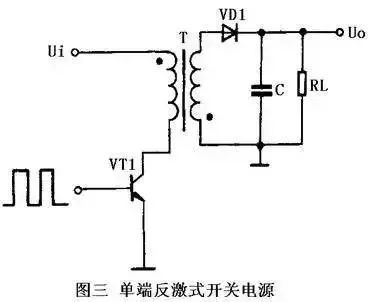

2. 可配置逻辑块(CLB)

CLB是FPGA内的基本逻辑单元。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都包含一个可配置开关矩阵,此矩阵由4或6个输入、一些选型电路(多路复用器等)和触发器组成。开关矩阵是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多个(一般为4个或2个)相同的Slice和附加逻辑构成,如图1-3所示。每个CLB模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式RAM和分布式ROM。

图1-3 典型的CLB结构示意图

Slice是Xilinx公司定义的基本逻辑单位,其内部结构如图1-4所示,一个Slice由两个4输入的函数、进位逻辑、算术逻辑、存储逻辑和函数复用器组成。算术逻辑包括一个异或门(XORG)和一个专用与门(MULTAND),一个异或门可以使一个Slice实现2bit全加操作,专用与门用于提高乘法器的效率;进位逻辑由专用进位信号和函数复用器(MUXC)组成,用于实现快速的算术加减法操作;4输入函数发生器用于实现4输入LUT、分布式RAM或16比特移位寄存器(Virtex-5系列芯片的Slice中的两个输入函数为6输入,可以实现6输入LUT或64比特移位寄存器);进位逻辑包括两条快速进位链,用于提高CLB模块的处理速度。

图1-4 典型的4输入Slice结构示意图

3. 数字时钟管理模块(DCM)

业内大多数FPGA均提供数字时钟管理(Xilinx的全部FPGA均具有这种特性)。Xilinx推出的FPGA提供数字时钟管理和相位环路锁定。相位环路锁定能够提供的时钟综合,且能够降低抖动,并实现过滤功能。

4. 嵌入式块RAM(BRAM)

大多数FPGA都具有内嵌的块RAM,这大大拓展了FPGA的应用范围和灵活性。块RAM可被配置为单端口RAM、双端口RAM、内容地址存储器(CAM)以及FIFO等常用存储结构。RAM、FIFO是比较普及的概念,在此就不冗述。CAM存储器在其内部的每个存储单元中都有一个比较逻辑,写入CAM中的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址,因而在路由的地址交换器中有广泛的应用。除了块RAM,还可以将FPGA中的LUT灵活地配置成RAM、ROM和FIFO等结构。在实际应用中,芯片内部块RAM的数量也是选择芯片的一个重要因素。

单片块RAM的容量为18k比特,即位宽为18比特、深度为1024,可以根据需要改变其位宽和深度,但要满足两个原则:首先,修改后的容量(位宽深度)不能大于18k比特;其次,位宽不能超过36比特。当然,可以将多片块RAM级联起来形成更大的RAM,此时只受限于芯片内块RAM的数量,而不再受上面两条原则约束。

5. 丰富的布线资源

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用以完成芯片Bank间的高速信号和第二全局时钟信号的布线;第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的结果有密切、直接的关系。

6. 底层内嵌功能单元

内嵌功能模块主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等软处理核(Soft Core)。现在越来越丰富的内嵌功能单元,使得单片FPGA成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向SOC平台过渡。

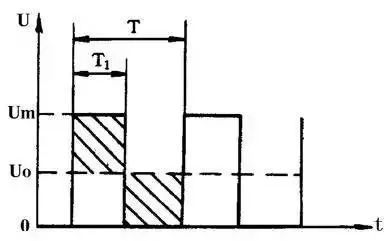

DLL和PLL具有类似的功能,可以完成时钟高精度、低抖动的倍频和分频,以及占空比调整和移相等功能。Xilinx公司生产的芯片上集成了DLL,Altera公司的芯片集成了PLL,Lattice公司的新型芯片上同时集成了PLL和DLL。PLL 和DLL可以通过IP核生成的工具方便地进行管理和配置。DLL的结构如图1-5所示。

图1-5 典型的DLL模块示意图

7. 内嵌专用硬核

内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA处理能力强大的硬核(Hard Core),等效于ASIC电路。为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用的硬核。例如:为了提高FPGA的乘法速度,主流的FPGA中都集成了专用乘法器;为了适用通信总线与接口标准,很多高端的FPGA内部都集成了串并收发器(SERDES),可以达到数十Gbps的收发速度。

Xilinx公司的高端产品不仅集成了Power PC系列CPU,还内嵌了DSP Core模块,其相应的系统级设计工具是EDK和Platform Studio,并依此提出了片上系统(System on Chip)的概念。通过PowerPC、Miroblaze、Picoblaze等平台,能够开发标准的DSP处理器及其相关应用,达到SOC的开发目的。

1.2.3 软核、硬核以及固核的概念

IP(Intelligent Property)核是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。到了SOC阶段,IP核设计已成为ASIC电路设计公司和FPGA提供商的重要任务,也是其实力体现。对于FPGA开发软件,其提供的IP核越丰富,用户的设计就越方便,其市场占用率就越高。目前,IP核已经变成系统设计的基本单元,并作为独立设计成果被交换、转让和销售。

从IP核的提供方式上,通常将其分为软核、硬核和固核这3类。从完成IP核所花费的成本来讲,硬核代价;从使用灵活性来讲,软核的可复用使用性。

1. 软核

软核在EDA设计领域指的是综合之前的寄存器传输级(RTL)模型;具体在FPGA设计中指的是对电路的硬件语言描述,包括逻辑描述、网表和帮助文档等。软核只经过功能仿真,需要经过综合以及布局布线才能使用。其优点是灵活性高、可移植性强,允许用户自配置;缺点是对模块的预测性较低,在后续设计中存在发生错误的可能性,有一定的设计风险。软核是IP核应用广泛的形式。

2. 固核

固核在EDA设计领域指的是带有平面规划信息的网表;具体在FPGA设计中可以看做带有布局规划的软核,通常以RTL代码和对应具体工艺网表的混合形式提供。将RTL描述结合具体标准单元库进行综合优化设计,形成门级网表,再通过布局布线工具即可使用。和软核相比,固核的设计灵活性稍差,但在可靠性上有较大提高。目前,固核也是IP核的主流形式之一。

3. 硬核

硬核在EDA设计领域指经过验证的设计版图;具体在FPGA设计中指布局和工艺固定、经过前端和后端验证的设计,设计人员不能对其修改。不能修改的原因有两个:首先是系统设计对各个模块的时序要求很严格,不允许打乱已有的物理版图;其次是保护知识产权的要求,不允许设计人员对其有任何改动。IP硬核的不许修改特点使其复用有一定的困难,因此只能用于某些特定应用,使用范围较窄。

FPGA芯片结构介绍及工作原理解析的更多相关文章

- SharePoint Client Object Model API 介绍以及工作原理解析

CSOM和ServerAPI 的对比 SharePoint从2010开始引入了Client Object Model的API(后文中用CSOM来代替),从名字来看,我们可以简单的看出,该API是面向客 ...

- jdk调度任务线程池ScheduledThreadPoolExecutor工作原理解析

jdk调度任务线程池ScheduledThreadPoolExecutor工作原理解析 在日常开发中存在着调度延时任务.定时任务的需求,而jdk中提供了两种基于内存的任务调度工具,即相对早期的java ...

- jdk线程池ThreadPoolExecutor工作原理解析(自己动手实现线程池)(一)

jdk线程池ThreadPoolExecutor工作原理解析(自己动手实现线程池)(一) 线程池介绍 在日常开发中经常会遇到需要使用其它线程将大量任务异步处理的场景(异步化以及提升系统的吞吐量),而在 ...

- 时间轮TimeWheel工作原理解析

时间轮工作原理解析 一.时间轮介绍 1.时间轮的简单介绍 时间轮(TimeWheel)作为一种高效率的计时器实现方案,在1987年发表的论文Hashed and Hierarchical Timing ...

- Docker Macvlan 介绍 or 工作原理

Docker Macvlan Network Macvlan Network:属于Docker的网络驱动. Macvlan Network:Docker主机网卡接口逻辑上分为多个子接口,每个子接口标识 ...

- Nginx02 Nginx的的目录结构、基本工作原理、基本配置文件介绍

1 Nginx目录结构 1.1 简要介绍 [root@localhost ~]# tree /usr/local/nginx /usr/local/nginx ├── client_body_temp ...

- FPGA第一篇:SRAM工作原理

一.SRAM概述 SRAM主要用于二级快速缓存(Level2 C ache). 它利用晶体管来存储数据.与DRAM相比,SRAM的速度快,但在同样面积中SRAM的容量要比其它类型的内存小. 大部分FP ...

- Servlet 工作原理解析

转自:http://www.ibm.com/developerworks/cn/java/j-lo-servlet/ Web 技术成为当今主流的互联网 Web 应用技术之一,而 Servlet 是 J ...

- [转]Servlet 工作原理解析

Web 技术成为当今主流的互联网 Web 应用技术之一,而 Servlet 是 Java Web 技术的核心基础.因而掌握 Servlet 的工作原理是成为一名合格的 Java Web 技术开发人员的 ...

- Servlet 工作原理解析--转载

原文:http://www.ibm.com/developerworks/cn/java/j-lo-servlet/index.html?ca=drs- Web 技术成为当今主流的互联网 Web 应用 ...

随机推荐

- crc16校验C语言源码实例解析

一 概念: 循环冗余码校验英文名称为Cyclical Redundancy Check,简称CRC.它是利用除法及余数的原理来作错误侦测(Error Detecting)的.实际应用时,发送装置计算出 ...

- ubuntu中在命令行如何打开图形界面的文件夹的几种方法

方法一: 使用自带的命令:nautilus . 打开当前文件夹 nautilus . 打开指定路径文件夹 nautilus ddd/ccc/ 方法二:xdg-open xdg-open 命令相当于在 ...

- pandas DataFrame内存优化技巧:让数据处理更高效

Pandas无疑是我们数据分析时一个不可或缺的工具,它以其强大的数据处理能力.灵活的数据结构以及易于上手的API赢得了广大数据分析师和机器学习工程师的喜爱. 然而,随着数据量的不断增长,如何高效.合理 ...

- KETTLE4个工作中有用的复杂实例--2、两表数据比较,循环取数据,比较后自动同步(部门、单位数据同步)

附:Kettle实战视频教程,需要的朋友可以看看学习下哈~~ kettle实战第一讲-文件和数据库表的互相转换处理_哔哩哔哩 (゜-゜)つロ 干杯~-bilibili kettle实战第二讲-数据库单 ...

- 通达信金融终端解锁Level-2功能 续(202307)

外挂方式,不修改原程序.解锁Level-2 逐笔分析.对"非法访问"Say NO! LEVEL2逐笔分析破解后,仍然被防调试. 竞价分析,实时资金示例. 逆向通达信Level-2 ...

- MyEclipse之各个版本的区别

跟Eclipse一样,MyEclipse的各个版本也是有区别的,他们所集成的插件是不同的. 从插件数量和功能的强大程度上讲:Blue>Professional>Standard MyEcl ...

- drf(Book序列化练习、user表练习)

一. APIView版本 1. models.py from django.db import models # Create your models here. class CommonField( ...

- 记录--Uni-app接入腾讯人脸核身

这里给大家分享我在网上总结出来的一些知识,希望对大家有所帮助 人脸核身功能有多种接入方式,其中包含微信H5.微信小程序.APP.独立H5.PC端.API接入6种方式. 我们的产品是使用uni-ap ...

- 记录-JS简单实现购物车图片局部放大预览效果

这里给大家分享我在网上总结出来的一些知识,希望对大家有所帮助 一.实现效果 二.代码实现 代码不多,先看一下 HTML 里面结构很简单,初始化 MagnifyingGlass 对象来关联一个 IMG ...

- 快速上手系列:传智播客Java基础学习笔记

配置环境,把JDK的bin所在路径复制到Path,末尾加; 基本语法 一 常见的DOS命令 盘符的切换 d:回车 目录的进入 cd javase c ...