2.2 Memory model

1. 内存区域、类型及属性

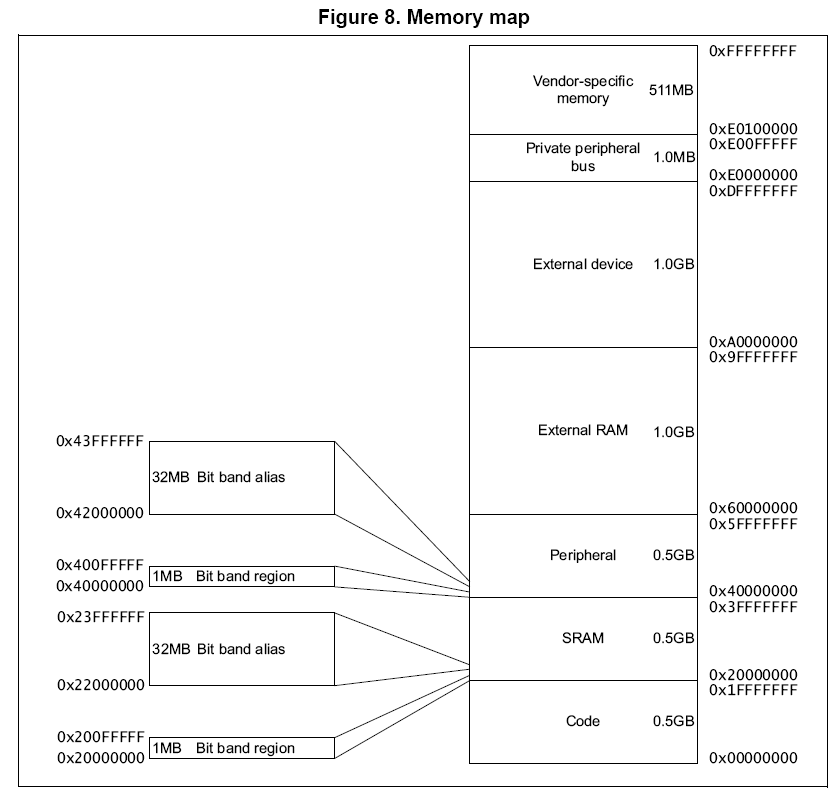

内存被分成不同的区域,不同区域有着不同的类型及属性;内存的类型及属性决定着访问这些区域时的行为。

内存的类型有:

- Normal,处理器可以为了效率而重新排序事务,或者执行推测性的读取。

- Device, 处理器将保持相对于其他Device或者Strongly-ordered内存的事务顺序。

- Strongly-ordered, 处理器将保持相对于其他内存的事务顺序。

- Execute Never (XN),处理器禁止指令访问。从XN区域获取指令的任何尝试都会导致内存管理错误异常。

内存系统可以缓冲对设备内存的写操作,但不能缓冲对Strongly-ordered内存的写操作。

2. 内存访问的系统顺序

对于大多数由显式内存访问指令引起的内存访问,内存系统不保证访问完成的顺序与指令的程序顺序相匹配,前提是这不会影响指令序列的行为。

通常,如果正确的程序执行取决于按程序流程完成的两次内存访问,软件必须在内存访问指令之间插入一条内存屏障指令。

然而,内存系统确实保证了对设备的访问和强顺序内存的一些顺序。对于两个内存访问指令A1和A2,如果在程序顺序中A1出现在A2之前,则由这两条指令引发的内存访问的顺序:

3. 内存访问的行为

Code, SRAM, 和外部RAM区域都可以存储程序,但是还是推荐使用Code区域运行程序,因为这里可以同时获取指令和访问数据。

MPU,内存包含单元,可以重载默认的内存访问行为。

4. 内存访问的软件顺序

在程序流程的指令顺序不一定总能保证和相应的内存事务顺序一致,这是因为:

- 处理器可以重新排序一些内存的访问来提高效率,前提是不会影响指令序列的行为。

- 处理器有多重总线接口

- 在内存区域中的内存或设备有不同的等待状态

- 一些内存的访问已被缓存或者被预测到了

如果内存的访问顺序很关键,软件必须包含内存屏障指令:

- DMB, Data Memory Barrier, 确保显著的内存事务完成在随后的内存事务之前

- DSB, Data Synchronization Barrier,确保内存事务完成在随后的指令执行之前

- ISB, Instruction Synchronization Barrier, 确保所有内存事务完成后的效果被随后的指令所识别

比如,在以下情况下使用内存屏障指令:

- 向量表:如果程序修改了向量表中的入口,然后使能了相应的异常。它们之间可以使用DMB,以保证如果异常在修改入口后立即发生时处理器可以使用新的入口地址。

- 自我修改代码:如果程序中含有自我修改的代码,在修改完代码后立即使用ISB指令,以保证随后的指令执行的是新程序

- 内存映射切换:如果系统包含内存映射切换的机制,在程序里切换完内存映射后使用DSB指令,以确保随后的指令用的是更新后的内存映射。

- 动态异常优先级变更:当一个异常处于挂起或激活状态而必须要修改其优先级时,使用DSB指令在修改完之后,以保证在DSB指令完成后所作的修改生效。

- 在多主控系统使用信号量:假如系统包含不止一个总线主控,如果其他处理器在系统中在用,那么每一个处理器都必须在信号量指令之后使用一个DMB指令来确保其他总线的主控能够看到内存事务按照被执行的顺序排列。

对Strongly-ordered区域的内存访问,比如SCB,不需要使用DMB指令。

对于MPU编程,使用一个DSB指令后跟着ISB指令或异常返回,以确保新的MPU配置已被随后的指令使用。

5. bit-banding, 位段

- 在别名(alias)区域写一个词会更新1个位在位段(bit-band)区域

- alias区域的BIT[0]与bit-band区域的位捆绑

- alias区域的BIT[31:1]对相应的bit-band区域没有影响,写0x01和写0xff效果一样,写0x00和写0xfe效果也一样。

- 读取alias区域:0x00000001表示对应bit-band区域的位为1;0x00000000表示该位是0

6. 内存的字节顺序

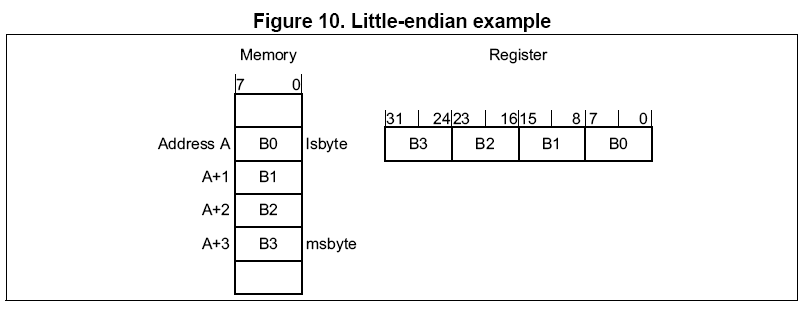

处理器将内存视为一个线性从0开始递增的字节集合。比如,字节0~3是第1个存储的字;字节4~7是第2个存储的字。

小头格式:

7. 同步原语

Cortex-M4指令集包含成对的同步原语。它们提供了一种非阻塞机制,线程或进程可以使用这种机制获得对内存位置的独占访问。软件可以使用它们来执行一个有保证的读-修改-写内存更新序列,或者用于信号量机制。

一对同步原语包括:

- 一种负载独占指令:用于读取内存位置的值,请求对该位置的独占访问。

- 一种存储独占指令:用于尝试写入相同的内存位置,向寄存器返回一个状态位。如果这位是:

- 0:线程或进程获得对内存的独占访问,写操作成功

- 1:线程或进程没有获得对内存的独占访问,并且没有执行写操作。

负载独占与存储独占指令对为:

- 单词指令LDREX和STREX // Load and store register exclusive.

- 半字指令LDREXH和STREXH

- 字节指令LDREXB和STREXB

软件必须使用一个与Store-Exclusive指令相对应的Load-Exclusive指令。

要执行一个有保证的 读-修改-写 内存位置,软件必须:

- 使用负载独占指令读取位置的值。

- 根据需要更新值。

- 使用存储独占指令尝试将新值写回内存位置。

- 测试返回的状态位。如果这部分是:

- 0:读-修改-写成功完成,

1:没有进行写操作。这表明在第1步返回的值可能已经过期。软件必须重试读-修改-写序列,

软件可以使用同步原语实现如下信号量:

- 使用负载独占指令从信号量地址读取信号量,以检查信号量是否空闲。

- 如果信号量是空闲的,则使用存储独占将声称的值写入信号量地址。

- 如果从第2步返回的状态位表明存储独占成功,那么软件就已经获得了信号量。但是,如果存储独占失败,那么在软件执行第1步之后,另一个进程可能已经获得了信号量。

Cortex-M4包含一个独占访问监视器,它标记处理器执行了一个负载独占指令的事实。

如果处理器是多处理器系统的一部分,则系统还全局标记由每个处理器的独占访问寻址的内存位置。

处理器删除它的独占访问标记,如果:

- 它执行一条CLREX指令

- 不管写操作是否成功,它都执行一个存储独占指令。

- 发生异常。这意味着处理器可以解决不同线程之间的信号量冲突。

在多处理器实现中,执行一个:

- CLREX指令只删除处理器的本地独占访问标记

存储独占指令或异常。删除处理器的本地独占访问标记和全局独占访问标记。

2.2 Memory model的更多相关文章

- Java (JVM) Memory Model – Memory Management in Java

原文地址:http://www.journaldev.com/2856/java-jvm-memory-model-memory-management-in-java Understanding JV ...

- 还是说Memory Model,gcc的__sync_synchronize真是太坑爹了

还是说Memory Model,gcc的__sync_synchronize真是太坑爹了! 时间 2012-01-29 03:18:35 IT牛人博客聚合网站 原文 http://www.udpw ...

- memory model

最近看C++11 atomic发现对memory_order很是不理解,memory_order_relaxed/memory_order_consume/memory_order_acquire/m ...

- Keil中Memory Model和Code Rom Size说明

C51中定义变量时如果省略存储器类型,Keil C51编译系统则会按编译模式SMALL.COMPACT和LARGE所规定的默认存储器类型去指定变量的存储区域,无论什么存储模式都可以声明变量在任何的80 ...

- 当我们在谈论JMM(Java memory model)的时候,我们在谈论些什么

前面几篇中,我们谈论了synchronized.final以及voilate的用法和底层实现,都绕不开一个话题-Java内存模型(java memory model,简称JMM).Java内存模型是保 ...

- 【翻译】go memory model

https://studygolang.com/articles/819 原文链接 Introduction The Go memory model specifies the conditions ...

- 并发研究之Java内存模型(Java Memory Model)

Java内存模型JMM java内存模型定义 上一遍文章我们讲到了CPU缓存一致性以及内存屏障问题.那么Java作为一个跨平台的语言,它的实现要面对不同的底层硬件系统,设计一个中间层模型来屏蔽底层的硬 ...

- java学习:JMM(java memory model)、volatile、synchronized、AtomicXXX理解

一.JMM(java memory model)内存模型 从网上淘来二张图: 上面这张图说的是,在多核CPU的系统中,每个核CPU自带高速缓存,然后计算机主板上也有一块内存-称为主内(即:内存条).工 ...

- CUDA ---- Memory Model

Memory kernel性能高低是不能单纯的从warp的执行上来解释的.比如之前博文涉及到的,将block的维度设置为warp大小的一半会导致load efficiency降低,这个问题无法用war ...

- 11 The Go Memory Model go语言内置模型

The Go Memory Model go语言内置模型 Version of May 31, 2014 Introduction 介绍 Advice 建议 Happens Before 在发生之前 ...

随机推荐

- vim 中代码的折叠和打开

# vim 中代码的折叠和打开 reference: vim中代码的折叠和打开(有删改) https://www.cnblogs.com/xuxm2007/archive/2011/11/10/224 ...

- Java 将Markdown文件转换为Word和PDF文档

Markdown 凭借其简洁易用的特性,成为创建和编辑纯文本文档的常用选择.但某些时候我们需要更加精致的展示效果,例如在专业分享文档或打印成离线使用的纸质版时,就需要将Markdown文件以其他固定的 ...

- Maven的依赖详解和打包方式

设置maven maven下载与安装教程: https://blog.csdn.net/YOL888666/article/details/122008374 1. 在File->setting ...

- 使用gitea搭建源码管理【0到1架构系列】

使用开源搭建Git源码方案,gitlab和gitea是两个不错的方案,gitlab以前简单易用,现在功能复杂且对开源并不友好,gitea一直保持功能单一易用且完全开源,个人推荐gitea. 通过容器安 ...

- Oracle 日期减年数、两日期相减

-- 日期减年数 SELECT add_months(DEF_DATE,12*USEFUL_LIFE) FROM S_USER --两日期相减 SELECT round(sysdate-PEI.STA ...

- opc ua设备数据 转MQTT项目案例

目录 1 案例说明 1 2 VFBOX网关工作原理 1 3 准备工作 2 4 配置VFBOX网关采集OPC UA的数据 2 5 用MQTT协议转发数据 4 6 配置参数说明 4 7 上报内容配置 5 ...

- AI生成前端组件的价值思考

想法来源 这个想法来源于我自己的需求,我自己首先就是最精准的目标用户,在这个AI时代,我希望AI可以帮我尽量多地干活. 结合自己的日常独立开发情况,发现花在调前端组件样式上的时间很多,因此思考能不能让 ...

- LLM-01 大模型 本地部署运行 ChatGLM2-6B-INT4(6GB) 简单上手 环境配置 单机单卡多卡 2070Super8GBx2 打怪升级!

搬迁说明 之前在 CSDN 上发文章,一直想着努力发一些好的文章出来!这篇文章在 2024-04-17 10:11:55 已在 CSDN 发布 写在前面 其他显卡环境也可以!但是最少要有8GB的显存, ...

- SpringBoot+ Sharding Sphere 轻松实现数据库字段加解密

一.介绍 在实际的软件系统开发过程中,由于业务的需求,在代码层面实现数据的脱敏还是远远不够的,往往还需要在数据库层面针对某些关键性的敏感信息,例如:身份证号.银行卡号.手机号.工资等信息进行加密存储, ...

- QT 的 ModelView

QApplication a(argc, argv); QDirModel model; //QDirModel, 问文件目录树 QTreeView tree; QListView l ...