用verilog模拟DDS产生正弦波信号

前言:

DDS:直接数字频率合成,正弦波0-2pi周期内,相位到幅度是一一对应的(这里我们使用放大后的整数幅度)。

主要思路:

个人理解,FPGA不擅长直接做数字信号计算,那样太占用片上逻辑资源,所以需要事先建立 正弦波相位-幅度 表,然后在时钟下,通过相位累加并用相位作为地址索引来查询正弦波信号表。

正弦波相位-幅度 表:

存储的是量化的正弦波在一个周期的幅度信息(幅度的地址即相位)。

幅度的地址数目决定了相位量化的误差。

而存储每一个幅度的比特数决定了幅度的量化误差。

可以通过matlab以及Xilinx的IP核向导创建。

Verilog编写的DDS模块主要由三部分组成,

- 相位累加器,用于决定输出信号频率的范围和精度;

- 正弦函数模块,用于存储经量化和离散后的正弦函数的幅值;

- 查表模块,对相位累加器的输出地址查表。

两种方法可以改变输出信号的频率:

- 改变查表寻址的时钟频率,从而改变输出波形的频率。

- 改变寻址的步长来改变输出信号的频率。

步长即为相位增量。

由累加器对相位增量进行累加,

累加器的值作为查表地址。

相位累加器是 DDS 的核心所在,前面在低于时钟频率的任意频率生成(相位累加器)中我们已经进行了叙述。

正弦函数模块包含一个周期正弦波的数字幅度信息,每个地址对应正弦波中0-2pi范围的一个相位点。查表模块把输入的地址相位信息映射成正弦波幅度的数字量信号。相位寄存器每经过 2^N/K 个时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,输出一个正弦波。

输出正弦波周期为fo=fc* K/2^N ,最小分辨率为f=fc/2^N。(通过fc和K控制正弦波频率精度) 其中,N 为累加器位宽,K 为步长,fc 为时钟频率。计数模(最大值):M=2^N。

一般正弦波表幅度地址位宽与累加的查表地址位宽不同,按前者位宽取后者对应高位的位宽即可。(具体见实例)

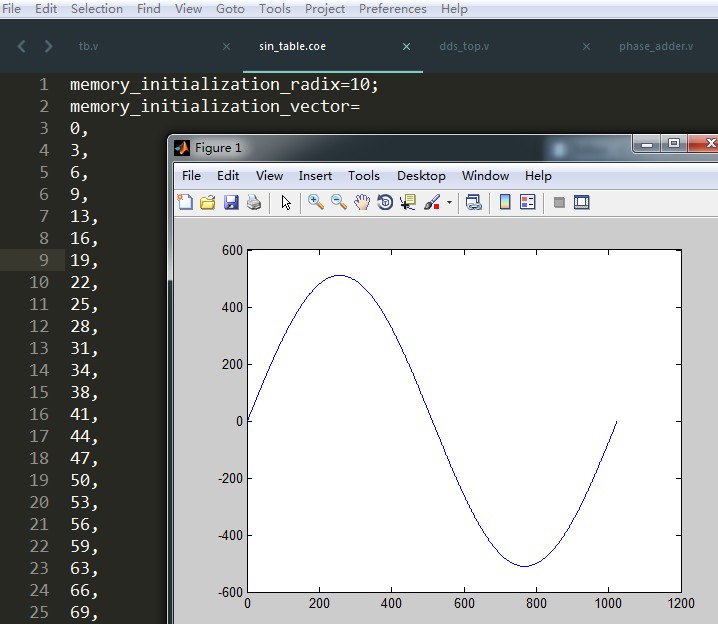

先用matlab生成1024点的正弦波数据:

clc;clear;

N = 10; %储存单元地址线

depth=2^N; %存储单元;

widths=N; %数据宽度为8位;

index = linspace(0,pi*2,depth);

sin_value = sin(index);

sin_value = sin_value * (depth/2 -1); %扩大正弦幅度值

sin_value = fix((sin_value)+0.5);

plot(sin_value);

number = [0:depth];

fid=fopen('sin_table.coe','w+');

fprintf(fid,'memory_initialization_radix=10;\n');

fprintf(fid,'memory_initialization_vector=\n');

for i = 1 : depth - 1

fprintf(fid, '%d,\n', sin_value(i));

end

fprintf(fid, '%d;', sin_value(depth));

fclose(fid);

Verilog程序

1、adder.v文件,相位累加模块

`timescale 1ns/1ps

/***************************************

晶振频率 fc = 100MHz

输出频率 fo = 1kHz(根据需要可以设为任意值)

控制参数 K = (fo*2^N)/fc = 42950

参数 N = 2^32,(32为计数器的位宽)

****************************************/

module PHASE_ADDER(

input clk,

input rst,

output reg [31:0] cnt,

output reg clk_out

);

always @(posedge clk or posedge rst)

if(rst)

cnt <= 0;

else

cnt <= cnt + 32'd42950; //计数器步长K

always @(posedge clk or posedge rst)

if(rst)

clk_out <= 1'b0;

else if(cnt < 32'h7FFF_FFFF)

clk_out <= 1'b0;

else

clk_out <= 1'b1;

endmodule

2、dds_top.v顶层设计

`timescale 10ns /1ns

module dds_top(

input rst,

input clk,

output signed [15:0] sine_o

);

wire [31:0] phase; //32bit内部连接线,传递相位增量

wire clk_out;

wire [9:0] addr; //10bit相位信息

PHASE_ADDER U_PHASE_ADDER(

.clk (clk ),

.rst (rst ),

.cnt (phase ),

.clk_out(clk_out)

);

assign addr = phase[31:22];//addr 10bit

DDS_Table U_DDS_Table(

.clka(clk), // input wire clka

.addra(addr), // input wire [9 : 0] addra

.douta(sine_o) // output wire [15 : 0] douta

);

endmodule

3、仿真测试文件

`timescale 1ns/1ps

module TB;

reg clk;

reg rst;

wire clk_out;

dds_top U_dds_top(

.clk (clk ),

.rst (rst )

);

initial begin

clk = 0;

rst = 0;

#4 rst = 1;

#3 rst = 0;

end

always #5 clk = ~clk;

endmodule

matlab生成正弦数据:

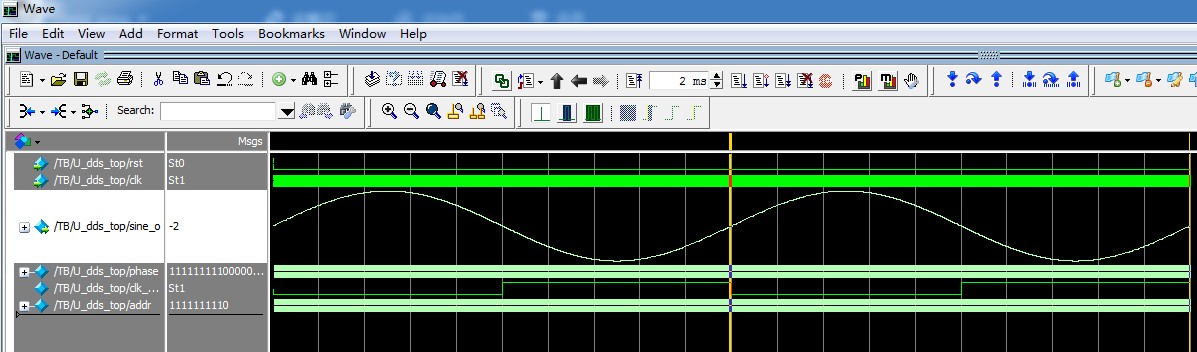

vivado和Modelsim联合仿真结果:

用verilog模拟DDS产生正弦波信号的更多相关文章

- verilog 实现DDS

一.DDS的原理 直接数字频率合成器(DDS),功能是通过输入频率输入字从而实现改变输出信号的频率的功能,它所利用的原理就是虽然对于一段正弦信号来说其幅度值是非线性的,但是其相位的值却是线性增加的,如 ...

- modelsim脚本文件的编写

第一章 ModelSim介 绍 本指南是为 ModelSim5.5f版本编写的,该版本运行于UNIX和Microsoft Windows 95/98/Me/NT/2000的操作系统环境中.本指南覆盖了 ...

- 中国澳门sinox很多平台CAD制图、PCB电路板、IC我知道了、HDL硬件描述语言叙述、电路仿真和设计软件,元素分析表

中国澳门sinox很多平台CAD制图.PCB电路板.IC我知道了.HDL硬件描述语言叙述.电路仿真和设计软件,元素分析表,可打开眼世界. 最近的研究sinox执行windows版protel,powe ...

- 搭建Modelsim SE仿真环境-使用do文件仿真

本章我们介绍仿真环境搭建是基于Modelsim SE的.Modelsim有很多版本,比如说Modelsim-Altera,但是笔者还是建议大家使用Modelsim-SE,Modelsim-Altera ...

- 彻底理解DDS(信号发生器)的fpga实现(verilog设计代码)

DDS(Direct Digital Synthesis)是一种把一系列数字信号通过D/A转换器转换成模拟信号的数字合成技术. 它有查表法和计算法两种基本合成方法.在这里主要记录DDS查表法的fpga ...

- 基于小脚丫DDS 调频 调幅 调相 切换波形 AD5601输出模拟波形

先讲讲里面的矩阵键盘,矩阵键盘列有下拉电阻,默认全为0000,默认行输入为1111,当有按键按下的时候,列输入会被拉高,这时控制行的输出做行扫描,电子琴用key_flag_r0电平作为使能,这里用ke ...

- psoc做dds

今天用psoc做了dds,现在总结一下. 1dds用到的相位累加器是用verilog写的,本来准备用一下datapath,这是和fpga不一样的一点,用了类似alu的结构,但是看手册后发现,虽然可以执 ...

- FPGA内部IP核DDS

项目当中需要正弦信号与余弦信号,首先想到了DDS芯片,例如AD9833.AD9834.由于还需要用FPGA 做一些数据处理,后来干脆直接用FPGA 内部的DDSIP核,同时根据IP核内部的相位累加 ...

- 基于DDS的任意波形发生器

实验原理 DDS的原理 DDS(Direct Digital Frequency Synthesizer)直接数字频率合成器,也可叫DDFS. DDS是从相位的概念直接合成所需波形的一种频率合成技术. ...

随机推荐

- Scala第三章学习笔记

换行后的左大括号造成的问题: class FooHolder { def foo() { println("foo was called") } } Scala认为def foo( ...

- DBA_Oracle Audit基本概念(概念)

2014-08-15 Created By BaoXinjian

- codeforces 336D. Vasily the Bear and Beautiful Strings 组合数学 dp

题意: 给出n,m,g,求好串的个数 0 <= n,m <= 10^5,n + m >= 1,0 <= g <= 1 好串的定义: 1.只由0,1组成,并且恰好有n个0, ...

- Web Penetration Testing 渗透 通信信息安全

参考 http://download.csdn.net/detail/jason571/8146587 一.操作系统原理,JavaScript,http/https的运行原理,Ajax,SQL等技术基 ...

- Windows2008防火墙封ip

http://www.bitscn.com/os/windows/201411/406212.html

- React Native 开发。

1.react-native run-android 安装 2.react-native start 开启调试端口

- 使用maven下载依赖包及maven常见问题汇总

最近下载了SPRING3.1.4,发现只有SPRING相关的源码,没有其依赖的jar包.SPRING依赖的jar相当多,自己一个一个的下载比较费劲,就仔细阅读了SPRING下载说明,新版本的SPRIN ...

- LNMP安装了哪些软件?安装目录在哪?

LNMP官网:http://lnmp.org/faq/lnmp-software-list.html LNMP一键安装包除去安装所必须的依赖包,还会默认安装以下软件: Nginx.MySQL/Mari ...

- http://host:8399/arcgis/rest/services/ 访问不了

一.问题: 安装完arvserver后,rest服务http://host:8399/arcgis/rest/services/访问不了 二.问题原因: 查看了一下manager日志,其中记录了几个r ...

- sql server 与oracle数据互导的一种思路--sql server链接服务器

思路:通过在sql server数据库中添加链接服务器,可以远程查询oracle数据库的表环境准备,安装sql server数据库,并安装好oracle驱动,在配置好tnsname文件中配置好orac ...