Verilog 加法器和减法器(2)

类似半加器和全加器,也有半减器和全减器。

半减器只考虑当前两位二进制数相减,输出为差以及是否向高位借位,而全减器还要考虑当前位的低位是否曾有借位。它们的真值表如下:

对半减器,diff = x ^y, cin = ~x&y

对全减器,要理解真值表,可以用举列子的方法得到,比如4’b1000-4b'0001,则第一位对应0 1 0 1 1第二位对应的是0 0 1 1 1

从真值表中,可以得到 diff = x ^ y ^cout, cin = (~x&(y^cout))|(y&cout)

推导过程:diff = ~x&~y&cout + ~x&y&~cout +x&~y&~cout+x&y&cout=~x&(~y&cout+y&~cout)+x&(~y&~cout+y&cout)=~x&(y^cout)+x&~(y^cout)=x^y^cout;

cin = ~x&~y&cout+~x&y&~cout+~x&y&cout+x&y&cout=~x&(~y&cout+~x&~cout)+(~x+x)&y&cout=~x&(y^cout)+y&cout

注意:这儿 +和|都表示或。

半减器的verilog代码和testbench代码如下:

module halfsub(x,y,d,cin); input x;

input y; output d;

output cin; assign d = x^y;

assign cin = (~x)&y; endmodule

`timescale 1ns/1ns

`define clock_period 20 module halfsub_tb;

reg x,y; wire cin; //carryover

wire d;

reg clk; halfsub halfsub_0(

.x(x),

.y(y),

.d(d),

.cin(cin)

); initial clk = 0;

always #(`clock_period/2) clk = ~clk; initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random; end initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random; end initial begin

#(`clock_period*20)

$stop;

end endmodule

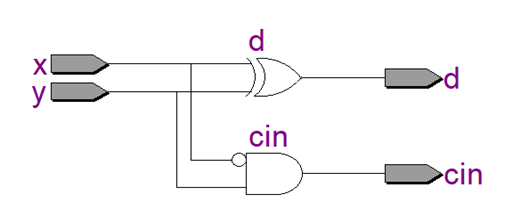

用rtl viewer,可以看到半减器逻辑图如下:

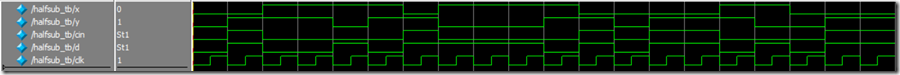

半减器功能验证的波形:

全减器的verilog代码和testbench代码如下:

module fullsub(cout,x,y,d,cin); input cout; // carry out bit, borrowed by its next low bit

input x;

input y; output d;

output cin; assign d = x^y^cout;

assign cin = (~x&(y^cout))|(y&cout); endmodule

`timescale 1ns/1ns

`define clock_period 20 module fullsub_tb;

reg x,y,cout; wire cin; //carryover

wire d;

reg clk; fullsub fullsub_0(

.cout(cout),

.x(x),

.y(y),

.d(d),

.cin(cin)

); initial clk = 0;

always #(`clock_period/2) clk = ~clk; initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random; end initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random; end initial begin

cout = 0;

repeat(20)

#(`clock_period) cout = $random; end initial begin

#(`clock_period*20)

$stop;

end endmodule

用rtl viewer,可以看到全减器逻辑图如下:

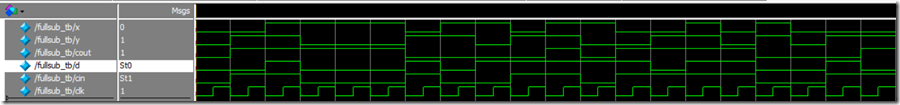

全减器的功能验证波形:

Verilog 加法器和减法器(2)的更多相关文章

- Verilog 加法器和减法器(8)-串行加法器

如果对速度要求不高,我们也可以使用串行加法器.下面通过状态机来实现串行加法器的功能. 设A=an-1an-2-a0, B=bn-1bn-2-b0,是要相加的两个无符号数,相加的和为:sum=sn-1s ...

- Verilog 加法器和减法器(4)

类似于行波进位加法器,用串联的方法也能够实现多位二进制数的减法操作. 比如下图是4位二进制减法逻辑电路图. 8位二进制减法的verilog代码如下: module subn(x, y, d,cin) ...

- Verilog 加法器和减法器(7)

在计算机中浮点数 表示通常采用IEEE754规定的格式,具体参考以下文章. https://www.cnblogs.com/mikewolf2002/p/10095995.html 下面我们在Veri ...

- Verilog 加法器和减法器(6)

为了减小行波进位加法器中进位传播延迟的影响,可以尝试在每一级中快速计算进位,如果能在较短时间完成计算,则可以提高加法器性能. 我们可以进行如下的推导: 设 gi=xi&yi, pi = xi ...

- Verilog 加法器和减法器(3)

手工加法运算时候,我们都是从最低位的数字开始,逐位相加,直到最高位.如果第i位产生进位,就把该位作为第i+1位输入.同样的,在逻辑电路中,我们可以把一位全加器串联起来,实现多位加法,比如下面的四位加法 ...

- Verilog 加法器和减法器(1)

两个一位的二进制数x,y相加,假设和为s,进位为cout,其真值表为: 从真值表中,我们可以得到:s = x^y, cout = x&y,实现两个一位数相加的逻辑电路称为半加器. 实现该电路的 ...

- Verilog 加法器和减法器(5)

前面二进制加法运算,我们并没有提操作数是有符号数,还是无符号数.其实前面的二进制加法对于有符号数和无符号数都成立.比如前面的8位二进制加法运算,第一张图我们选radix是unsigned,表示无符号加 ...

- 基于Xilinx的Synthesize

所谓综合.就是讲HDL语言.原理图等设计输入翻译成由与.或.非们和RAM.触发器登记本逻辑单元的逻辑连接(即网表).并依据目标和要求(约束条件)优化生成的逻辑连接. ISE-XST XST是Xilin ...

- FPGA综合工具--Synplify Pro的常用选项及命令

最近要用到Synplify,但以前没使用过,无基础,找到一篇帖子,隧保存下来. 本文转自:http://blog.sina.com.cn/s/blog_65fe490d0100v8ax.html Sy ...

随机推荐

- 踩过无数坑实现的哈夫曼压缩(JAVA)

最近可能又是闲着没事干了,就想做点东西,想着还没用JAVA弄过数据结构,之前搞过算法,就试着写写哈夫曼压缩了. 本以为半天就能写出来,结果,踩了无数坑,花了整整两天时间!!orz...不过这次踩坑,算 ...

- 简单的CSS3 Loading动画

最终效果如图一,gif图片稍微有点卡顿,事实上代码在浏览器里执行得很流畅.这里面用到的css3技术非常简单,分别是border-radius.伪元素.css3关键帧以及animation动画. 首先整 ...

- 使用ApiPost测试接口时需要先登录怎么办?利用Cookie模拟登陆!

ApiPost简介: ApiPost是一个支持团队协作,并可直接生成文档的API调试.管理工具.它支持模拟POST.GET.PUT等常见请求,是后台接口开发者或前端.接口测试人员不可多得的工具 . 下 ...

- centos 7 安装 BeautifulSoup 和requests

安装beautifulsoup wget https://www.crummy.com/software/BeautifulSoup/bs4/download/4.5/beautifulsoup4-4 ...

- 网络设备Web登录检测工具device-phamer

网络设备Web登录检测工具device-phamer 为了便于管理和维护,大部分网络都提供了Web管理接口.Kali Linux提供了一款专用检测工具device-phamer.该工具可以批量检测 ...

- linux 驱动之LCD驱动(有framebuffer)

<简介> LCD驱动里有个很重要的概念叫帧缓冲(framebuffer),它是Linux系统为显示设备提供的一个接口,应用程序在图形模式允许对显示缓冲区进行读写操作.用户根本不用关心物理显 ...

- Linux驱动之平台设备

<平台设备设备驱动> a:背景: 平台总线是Linux2.6的设备驱动模型中,关心总线,设备和驱动这3个实体.一个现实的Linux设备和驱动通常需要挂接在一种总线上(比如本身依附于PCI, ...

- Bootstrap css-表格

前言:整理的东西比较基础,有不足的地方欢迎大家批评指正! 1,Bootstrap基本的表格结构 源代码: <table class="table"> <cap ...

- HDU 5832 A water problem 水题

A water problem 题目连接: http://acm.hdu.edu.cn/showproblem.php?pid=5832 Description Two planets named H ...

- Android学习笔记PreferenceFragment的使用

相信大家对Perference都比较熟悉了,也就是我们常说的偏好设置,首选项设置,可以保存一些数据,例如我们在上一次使用的时候的一些内容,希望在下一次启动后依然生效,而不需要再进行配置那么麻烦.一般这 ...